### MIXED-SIGNAL MULTIMEDIA SEMICONDUCTORS

### PRODUCT DATA SHEET

# STMP36xx

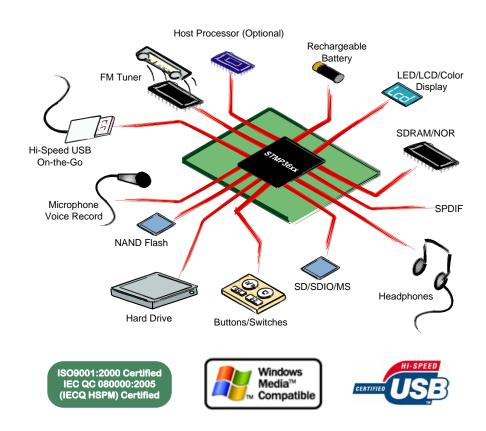

# Audio System on Chip with USB OTG, LCD, Hard Drive, and Battery Charger

Fourth-Generation Audio Decoder Version 1.02 May 3, 2006

# **OFFICIAL PRODUCT DOCUMENTATION 5/3/06**

5-36xx-D1-1.02-050306

Copyright © 2003-2006 SigmaTel, Inc.

All rights reserved.

SigmaTel, Inc. makes no warranty for the use of its products, assumes no responsibility for any errors which may appear in this document, and makes no commitment to update the information contained herein. SigmaTel reserves the right to change or discontinue this product at any time, without notice. There are no express or implied licenses granted hereunder to design or fabricate any integrated circuits based on information in this document.

The following are trademarks of SigmaTel, Inc., and may be used to identify SigmaTel products only: SigmaTel, the SigmaTel Logo, C Major, D Major and Go-Chip. Windows Media and the Windows logo are trademarks or registered trademarks of Microsoft Corporation in the United States and/or other countries. Other product and company names contained herein may be trademarks of their respective owners.

### **CUSTOMER SUPPORT**

Additional product and company information can be obtained by going to the SigmaTel website at: http://www.sigmatel.com

Additional product and design information is available for authorized customers at: http://extranet.sigmatel.com

The product shown in this data sheet is not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Any use or distribution of this product in such applications is at your own risk. SigmaTel, Inc. does not assume any liability arising out of the application or use of any product or circuit shown herein, and specifically disclaims any and all liability, including without limitation special, consequential, or incidental damages. Supply of this Implementation of AAC technology does not convey a license nor imply any right to use this Implementation in any finished end-user or ready-to-use final product. An independent license for such use is required.

2 5-36xx-D1-1.02-050306

# **CONTENTS**

|    | REVISION HISTORY                                                   | . 21 |

|----|--------------------------------------------------------------------|------|

| 1. | PRODUCT OVERVIEW                                                   | 23   |

|    | 1.1. Hardware Features                                             |      |

|    | 1.2. Application Capability                                        |      |

|    | 1.3. Design Support                                                | . 25 |

|    | 1.4. Additional Documentation                                      | 25   |

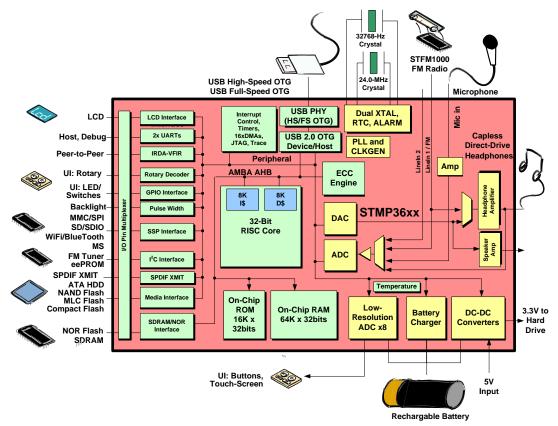

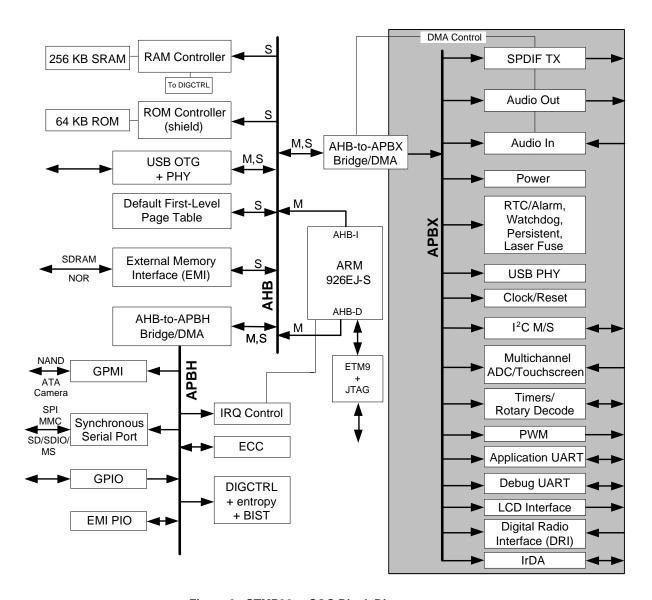

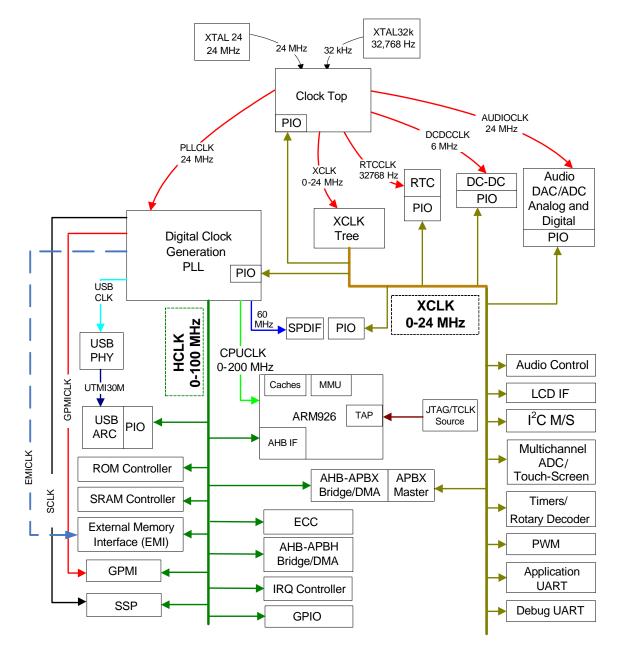

|    | 1.5. STMP36xx System Block Diagram                                 | 26   |

|    | 1.6. STMP36xx Product Features                                     |      |

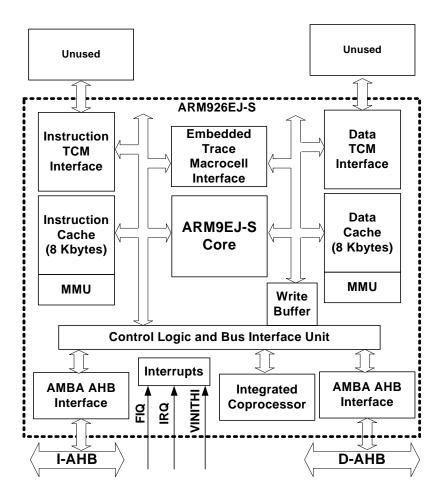

|    | 1.6.1. ARM 926 Processor Core                                      | 27   |

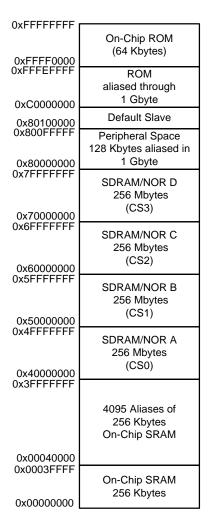

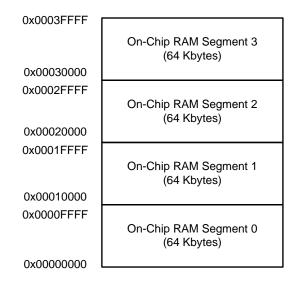

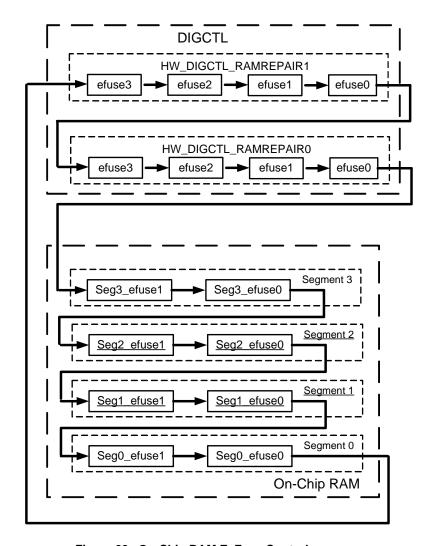

|    | 1.6.2. On-Chip RAM and ROM                                         |      |

|    | 1.6.3. Interrupt Collector                                         | 30   |

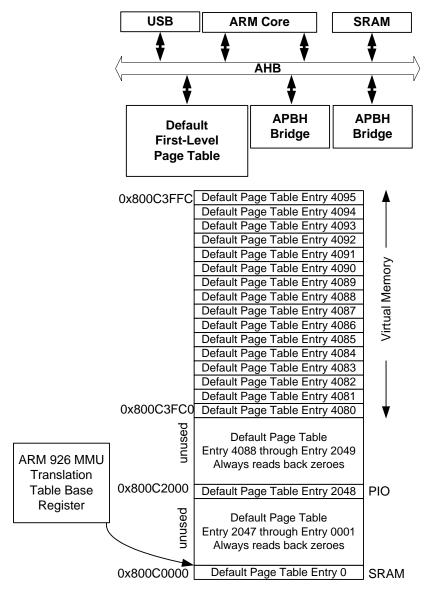

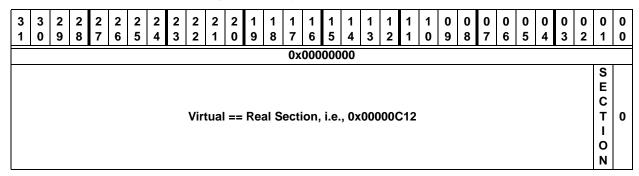

|    | 1.6.4. Default First-Level Page Table                              | 30   |

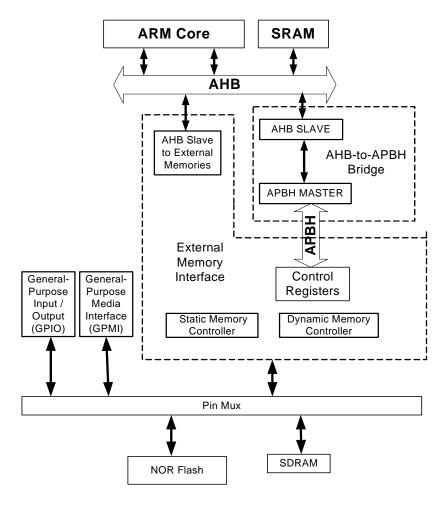

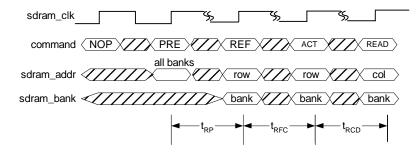

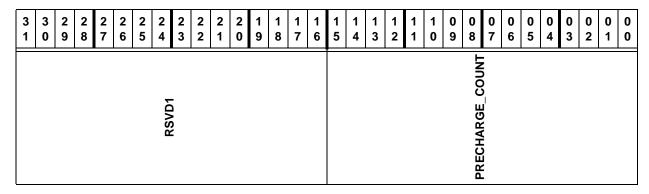

|    | 1.6.5. External Memory Interface (SDRAM/NOR Flash Controller)      | 30   |

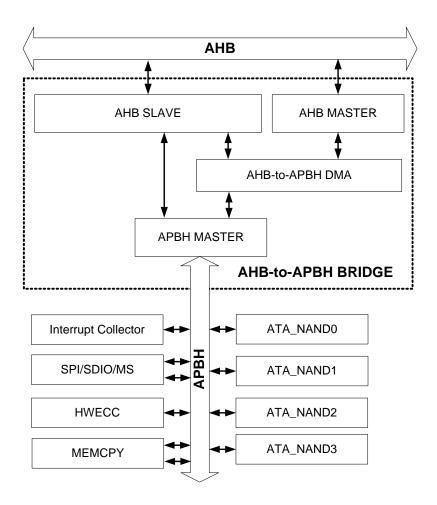

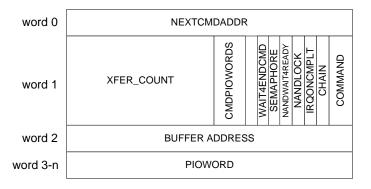

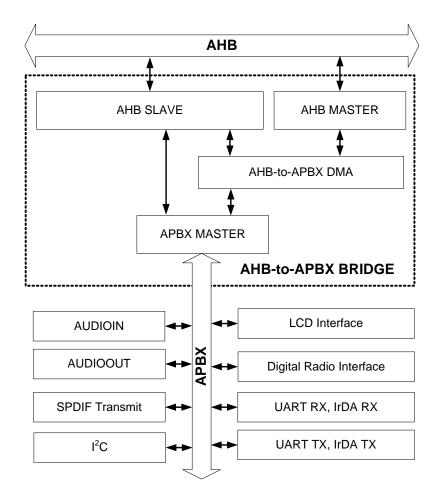

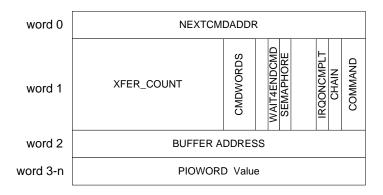

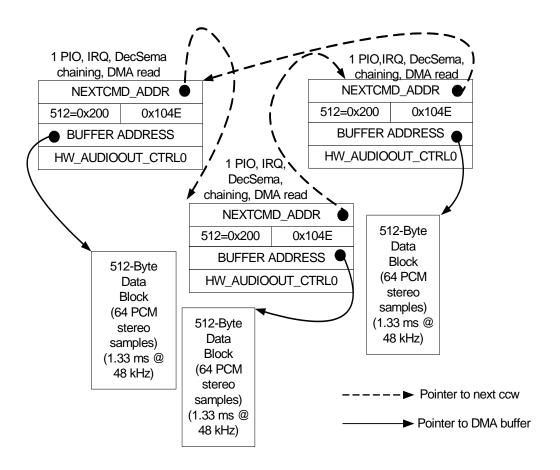

|    | 1.6.6. DMA Controller                                              | 31   |

|    | 1.6.7. Clock Generation Subsystem                                  |      |

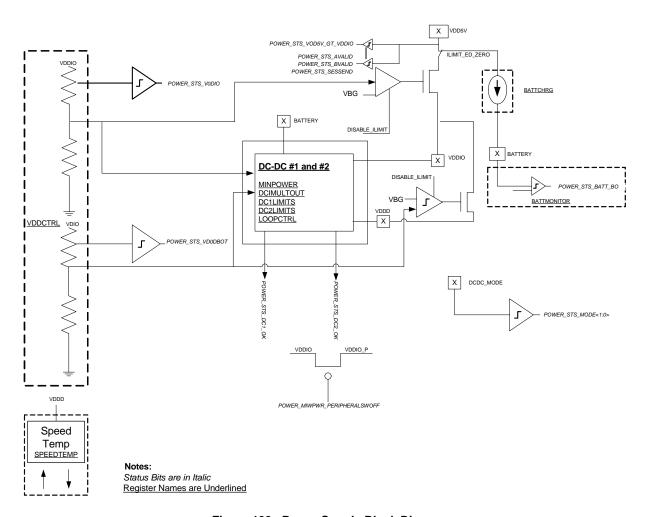

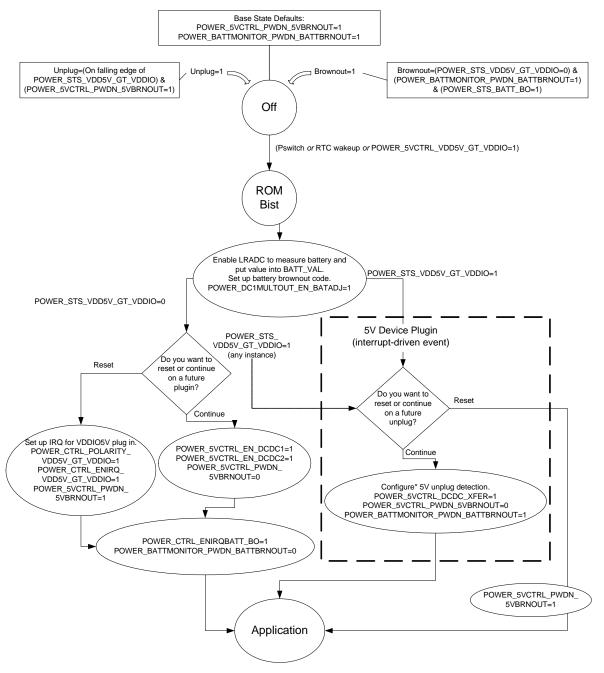

|    | 1.6.8. Power Management Unit                                       |      |

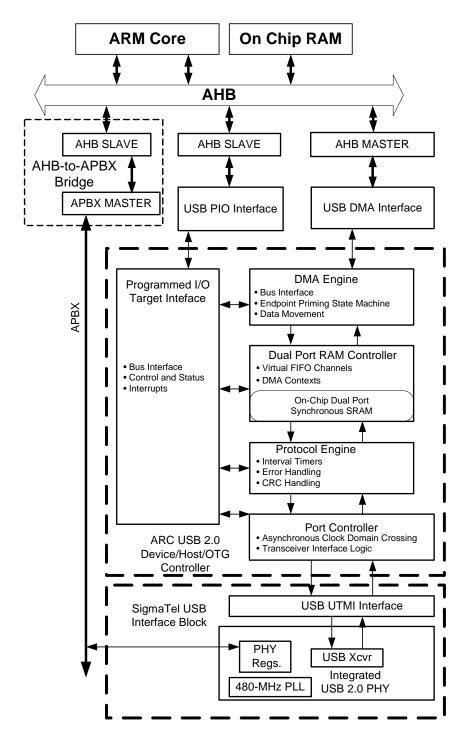

|    | 1.6.9. USB Interface                                               |      |

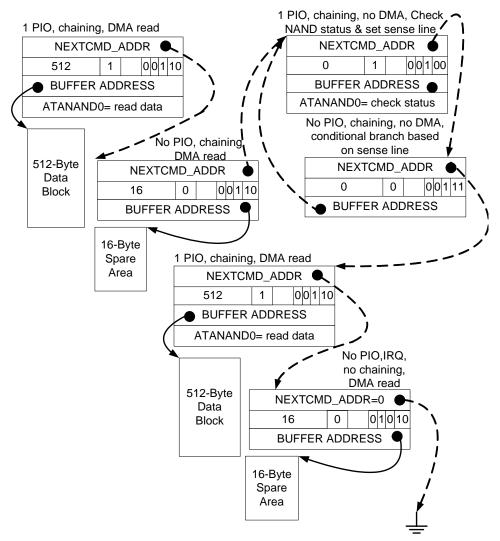

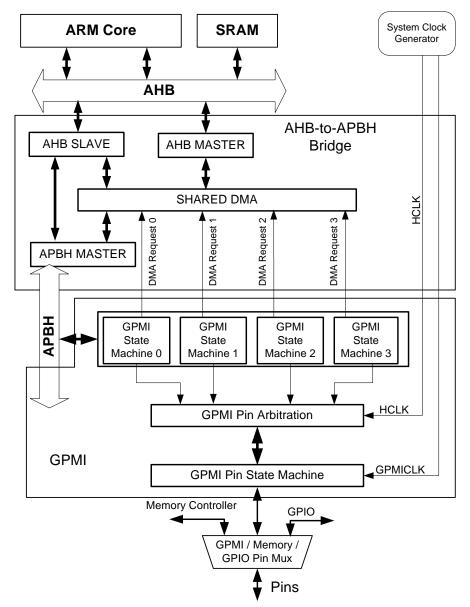

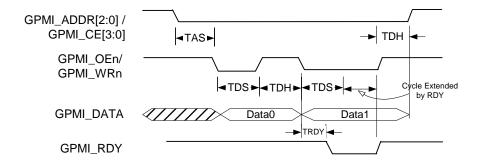

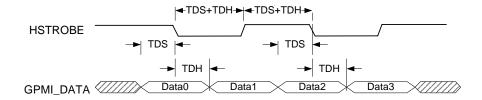

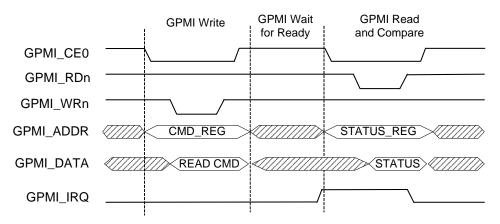

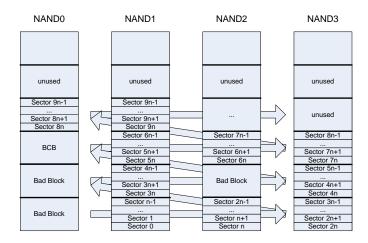

|    | 1.6.10. General-Purpose Media Interface (GPMI)                     | 33   |

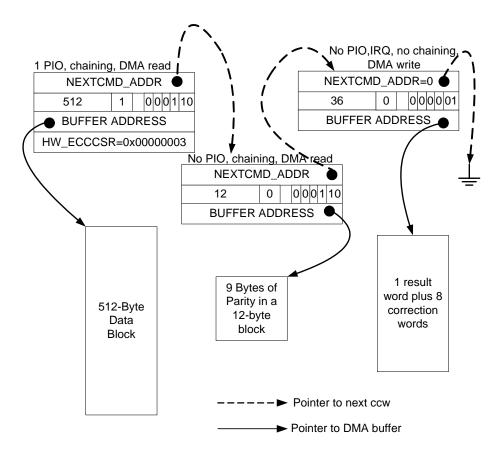

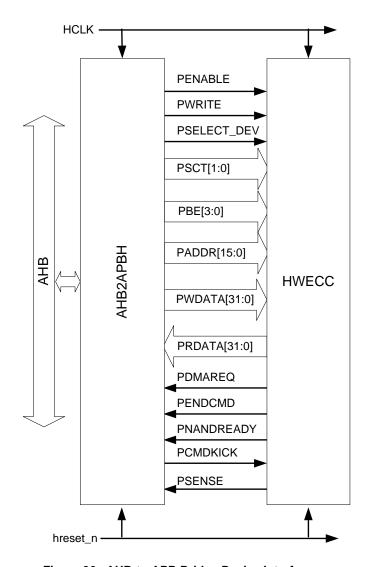

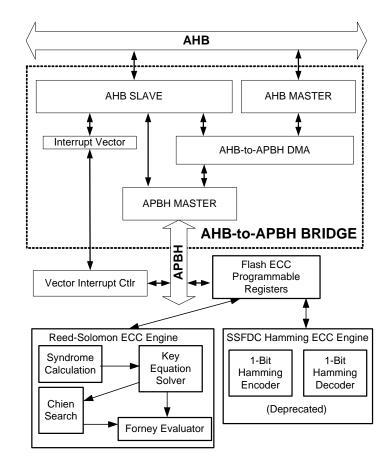

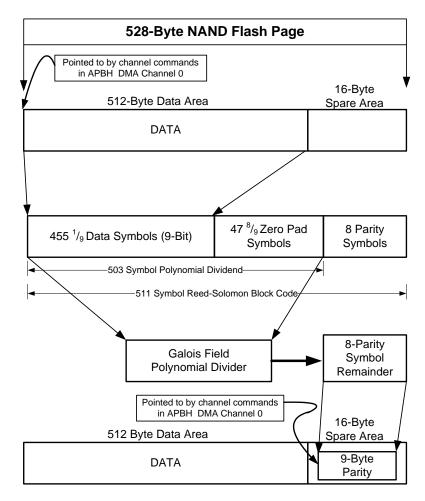

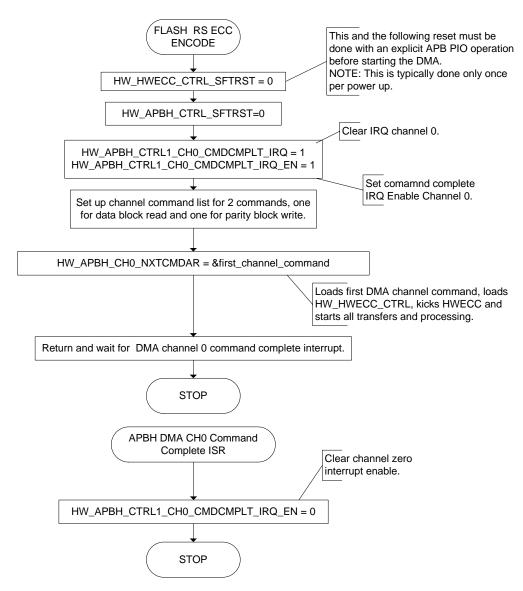

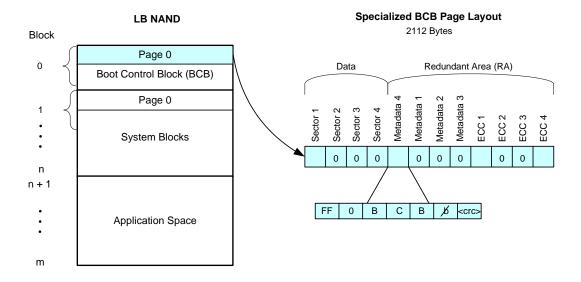

|    | 1.6.11. Hardware Acceleration for ECC for Robust External Storage  | 34   |

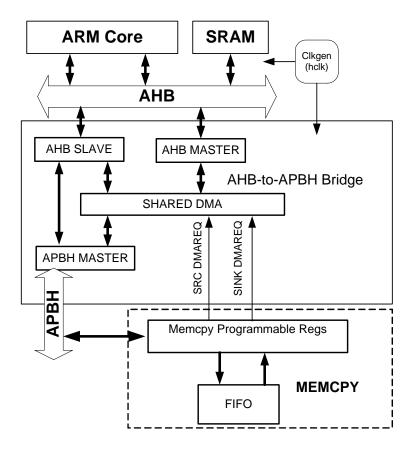

|    | 1.6.12. Memory Copy Unit                                           | 34   |

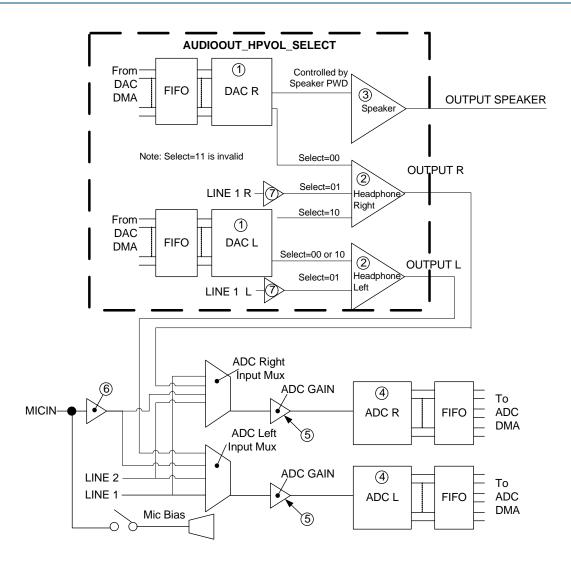

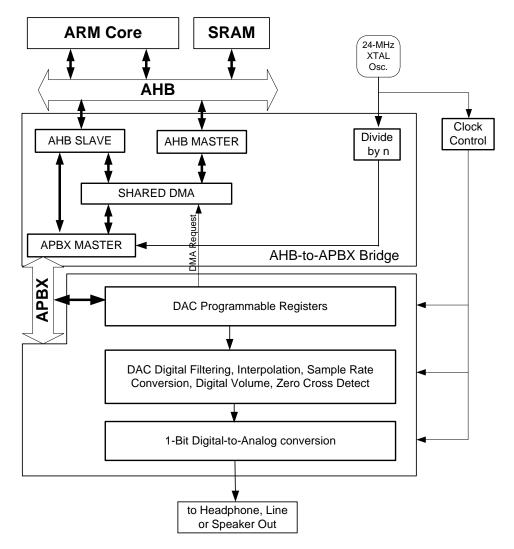

|    | 1.6.13. Mixed Śignal Audio Subsystem                               | 35   |

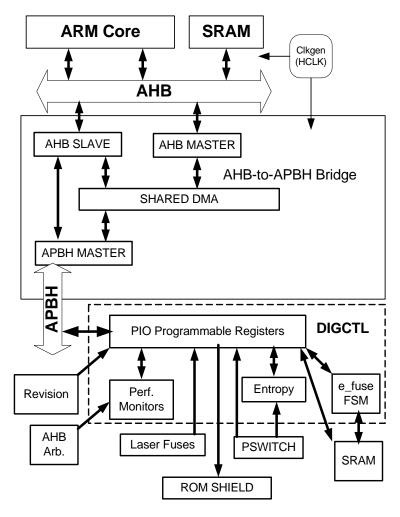

|    | 1.6.14. Master Digital Control Unit (DIGCTL)                       | 35   |

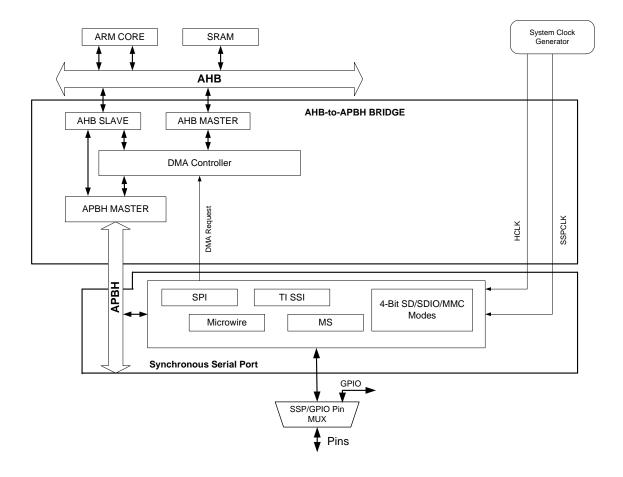

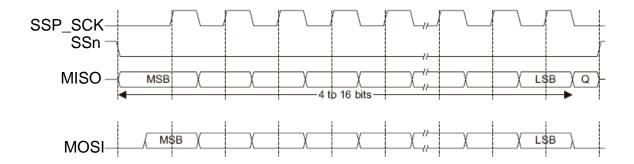

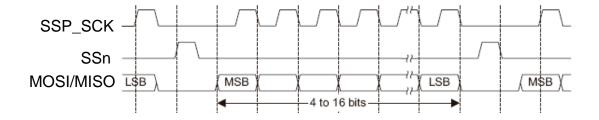

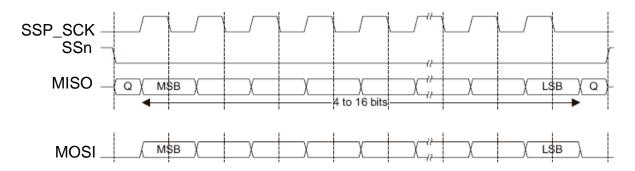

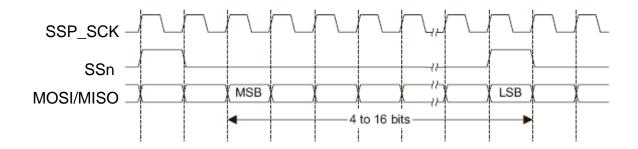

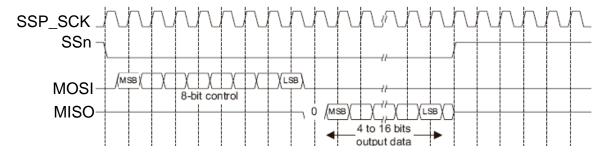

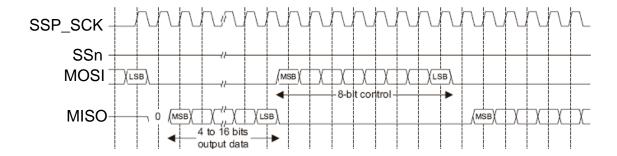

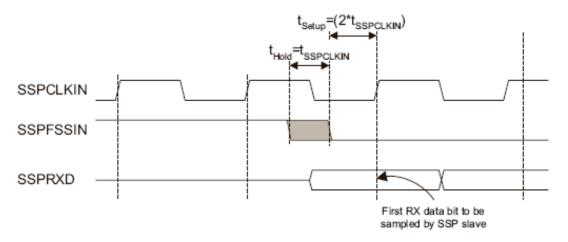

|    | 1.6.15. Synchronous Serial Port (SSP)                              | 35   |

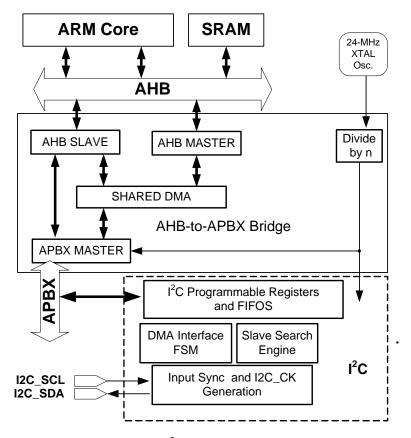

|    | 1.6.16. I <sup>2</sup> C Interface                                 | 35   |

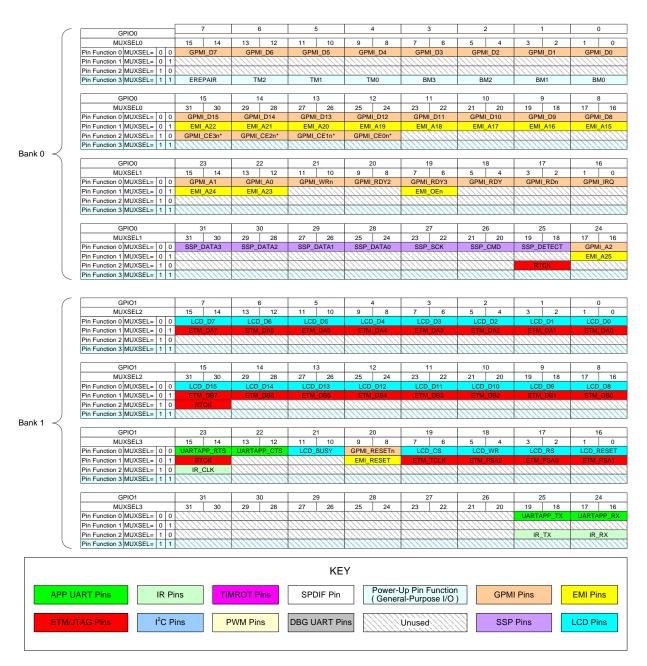

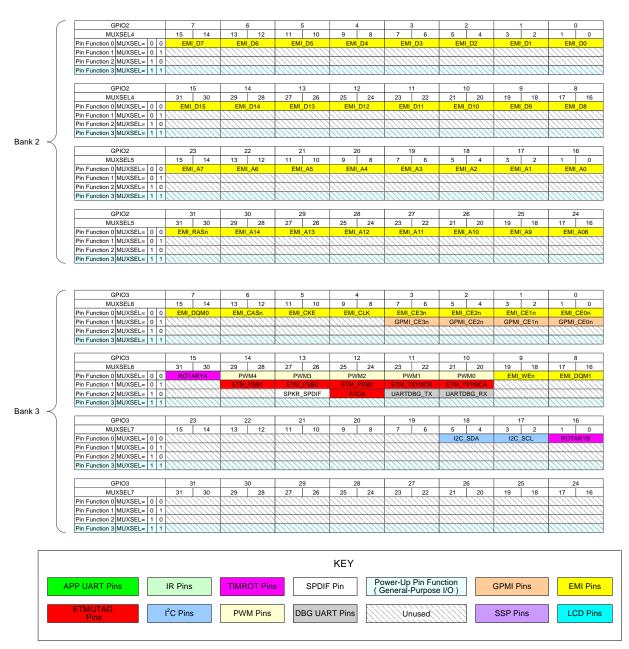

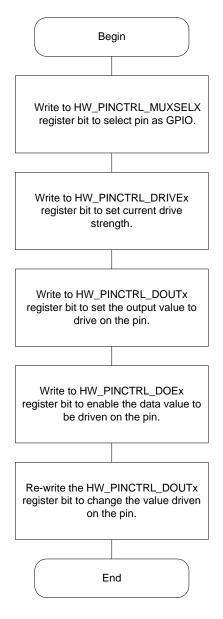

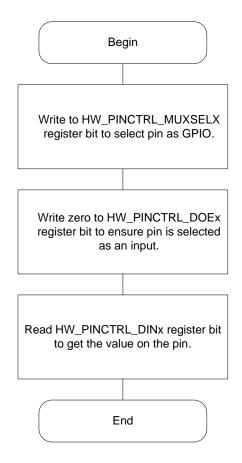

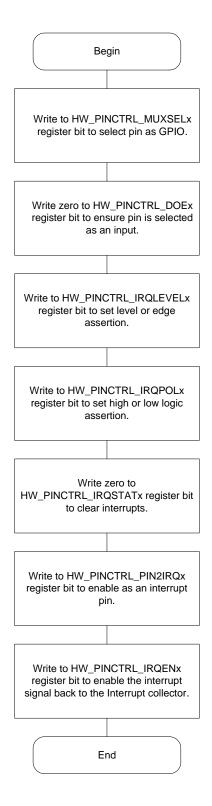

|    | 1.6.17. General-Purpose Input/Output (GPIO)                        | 36   |

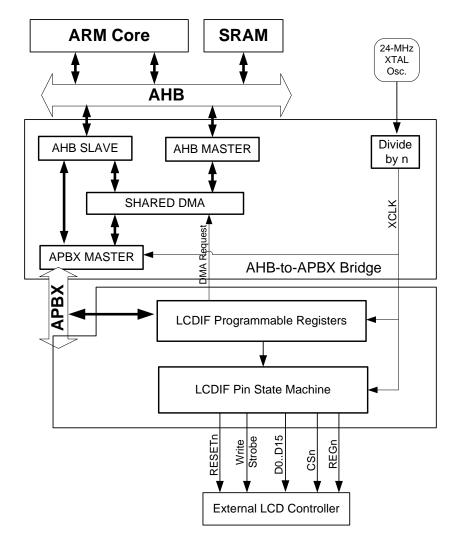

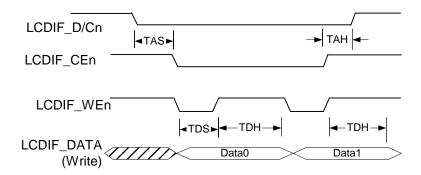

|    | 1.6.18. LCD Controller                                             | 37   |

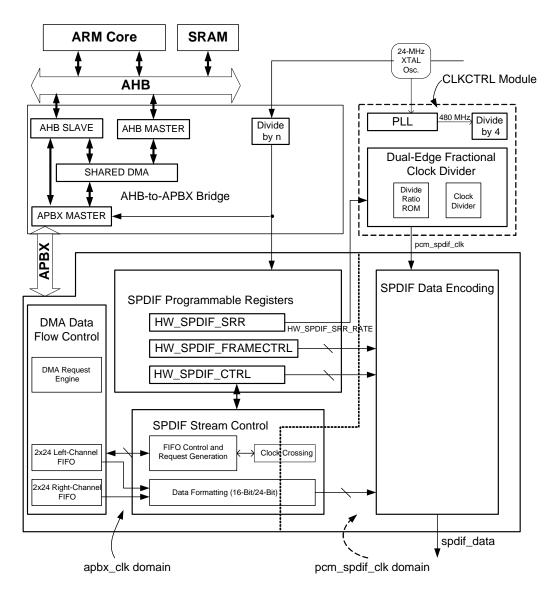

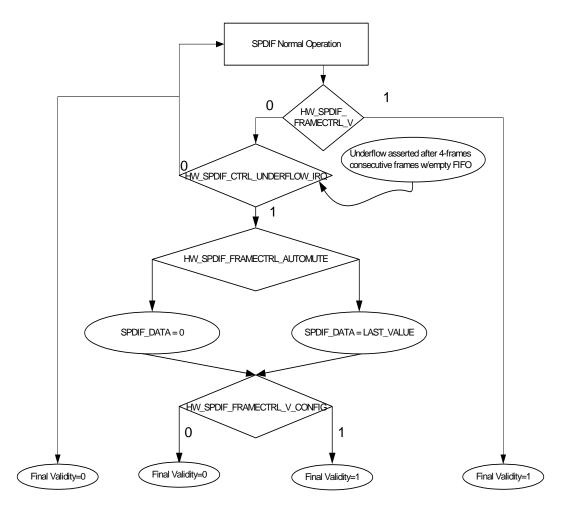

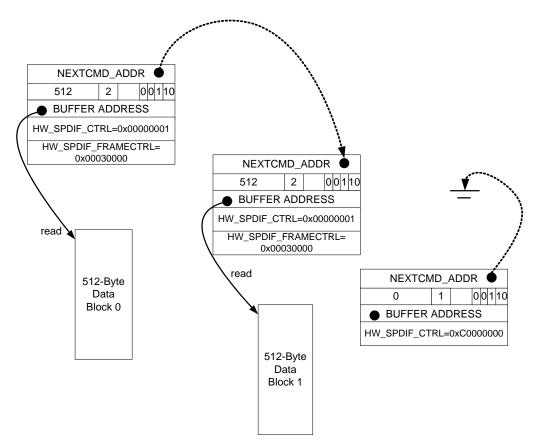

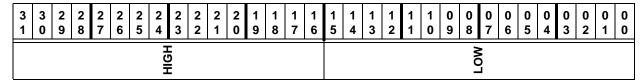

|    | 1.6.19. SPDIF Transmitter                                          | 37   |

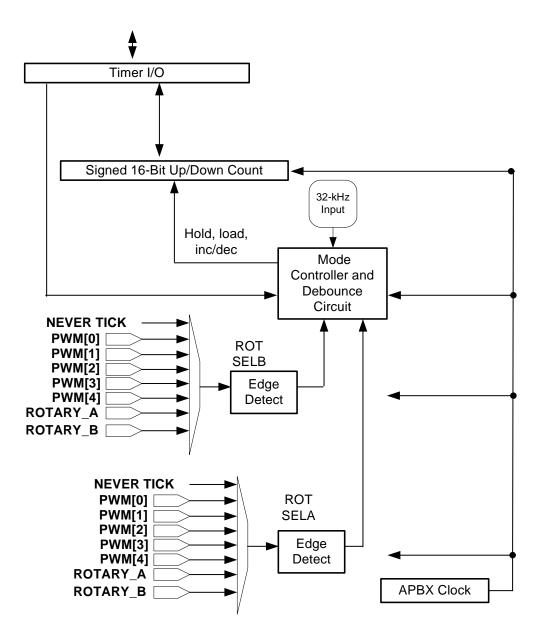

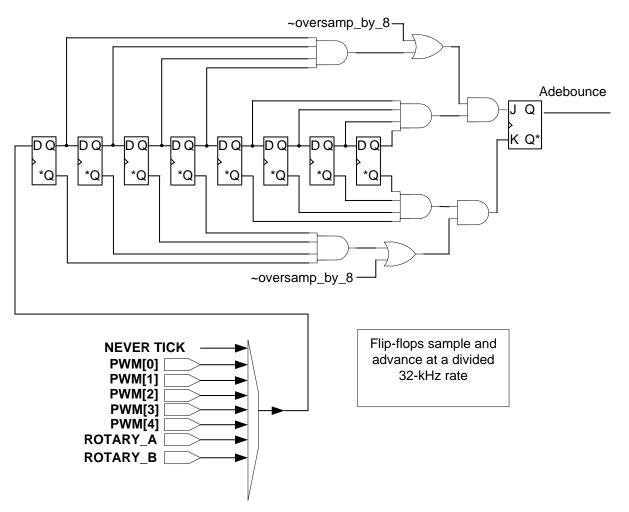

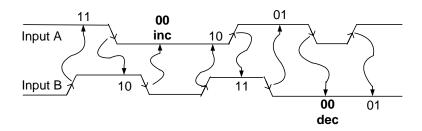

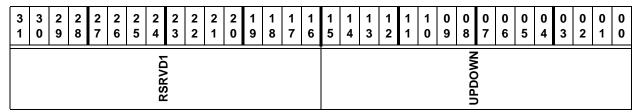

|    | 1.6.20. Rotary Decoder                                             | 37   |

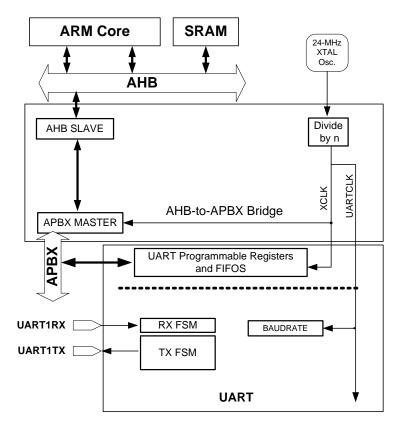

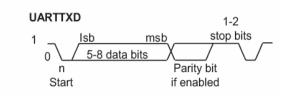

|    | 1.6.21. Dual ÙARTs                                                 | 37   |

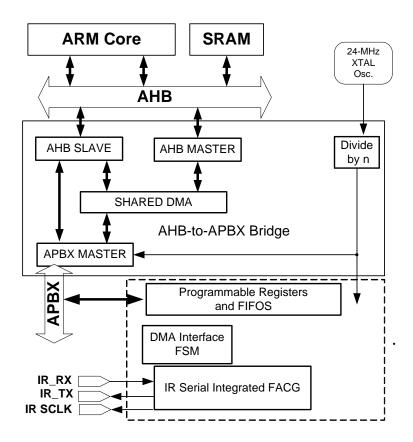

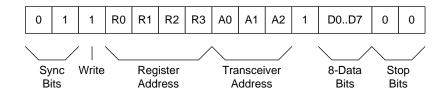

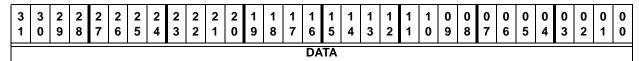

|    | 1.6.22. Infrared Interface                                         | 37   |

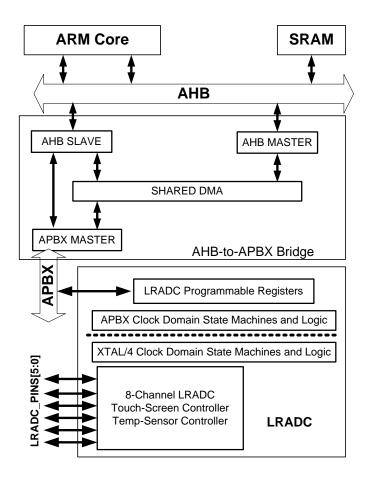

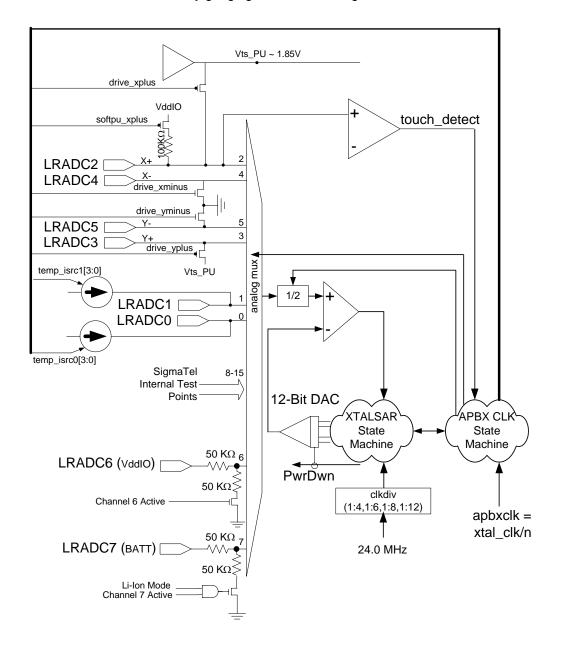

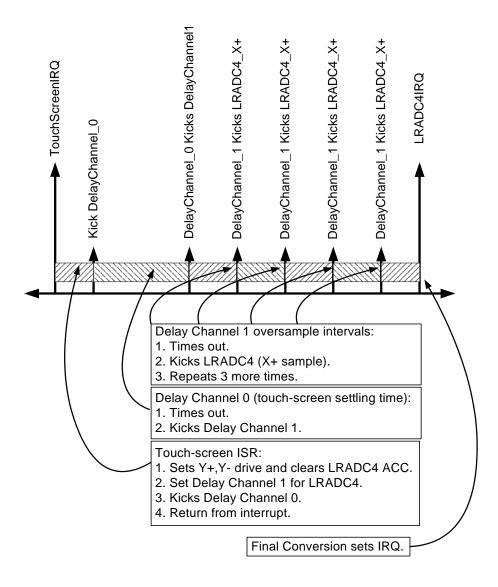

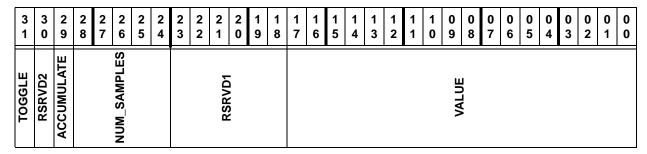

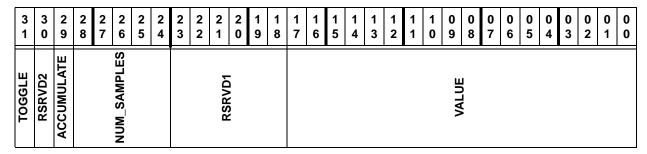

|    | 1.6.23. Low-Resolution ADC and Touch-Screen Interface              | 37   |

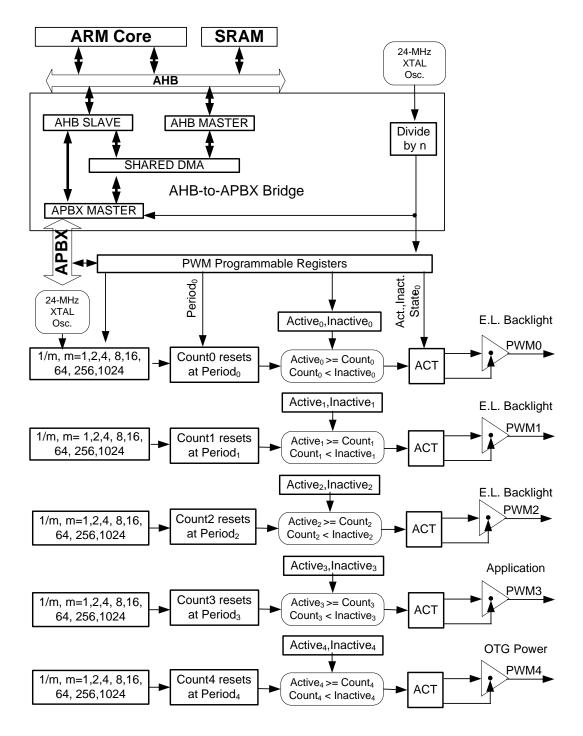

|    | 1.6.24. Pulse Width Modulator (PWM) Controller                     | 37   |

|    | 1.6.25. Camera Interface                                           | 38   |

| 2. | CHARACTERISTICS AND SPECIFICATIONS                                 | 39   |

|    | 2.1. Absolute Maximum Ratings                                      | 30   |

|    | 2.2. Recommended Operating Conditions                              |      |

|    | 2.2.1. Recommended Operating Conditions for Specific Clock Targets | 41   |

|    | 2.3. DC Characteristics                                            | 42   |

|    |                                                                    |      |

| 3. |                                                                    |      |

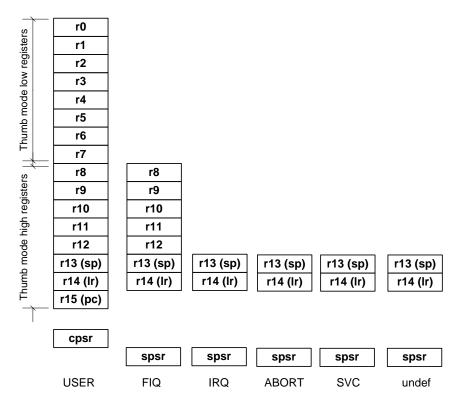

|    | 3.1. ARM 926 Processor Core                                        |      |

|    | 3.2. JTAG Debugger                                                 |      |

|    | 3.2.1. JTAG READ ID                                                |      |

|    | 3.2.2. JTAG Hardware Reset                                         | 45   |

|    | 3.2.3. JTAG Interaction with CPUCLK                                | 45   |

|    | 3.3. Embedded Trace Macroceii (ETM) Interface                      | 40   |

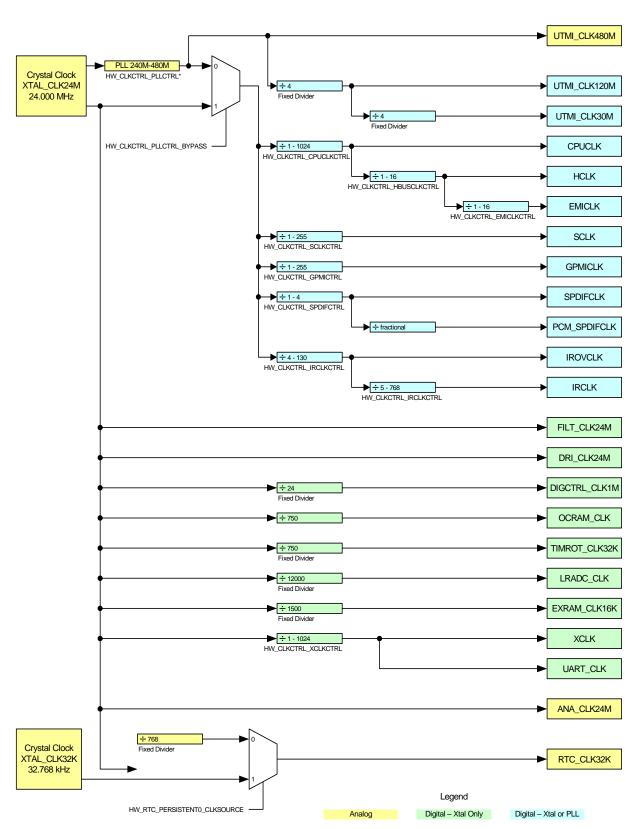

| 4. | CLOCK GENERATION AND CONTROL                                       | 47   |

|    | 4.1. Overview                                                      | 47   |

|    | 4.2. Crystal Oscillators                                           | 47   |

|    | 4.3. Clock Domains                                                 | 47   |

|    | 4.4. Power Saving Features of the Clock Architecture               | 49   |

|    | 4.5. Clock Dividers                                                | 49   |

|    | 4.5.1. Automatic HCLK Divider                                      | 49   |

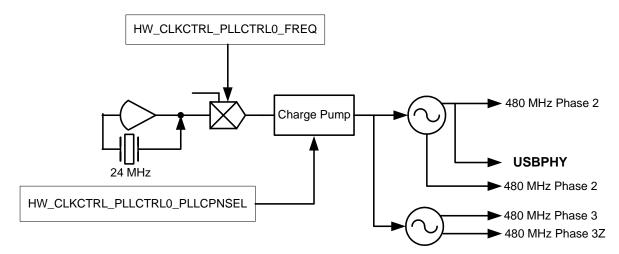

|    | 4.6. Phase-Locked Loop (PLL)                                       | 51   |

|    | 4.6.1. Frequency Program                                           | 52   |

|    | 4.6.2. PLL Use in USB and SPDIF Modes                              | 52   |

|    | 4.6.3. VCO and Phase Followers                                     |      |

|    | 4.6.4. PFD and Charge Pump                                         | 53   |

|    | - · · · · · · · · · · · · · · · · · · ·                            |      |

# SIGMATEL

|    | 4.7.1.4. (1.110D.0.0.DUNALES E. C. EL OL. 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

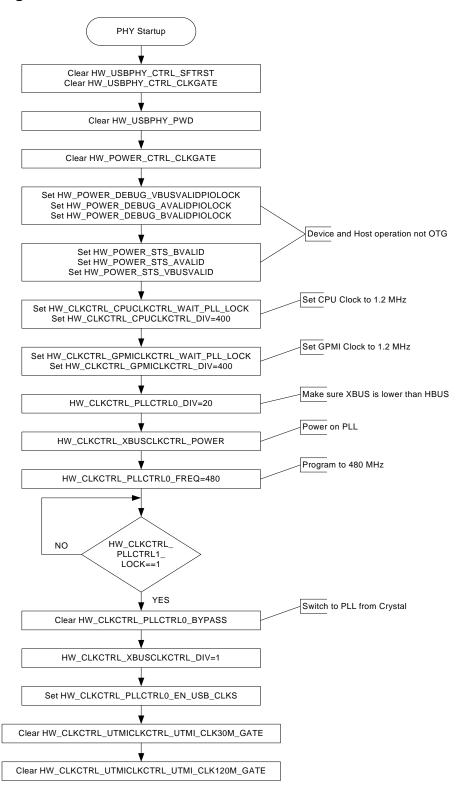

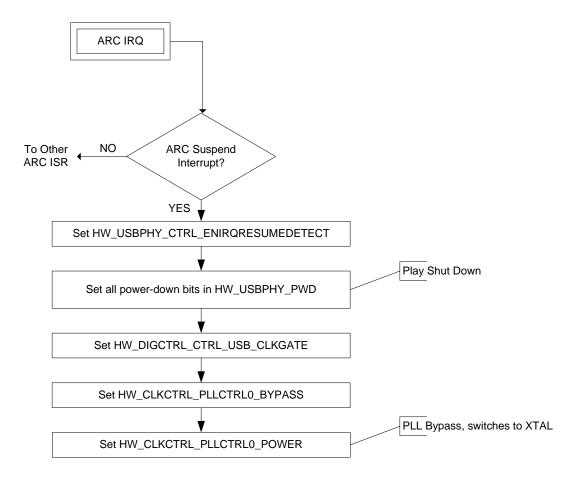

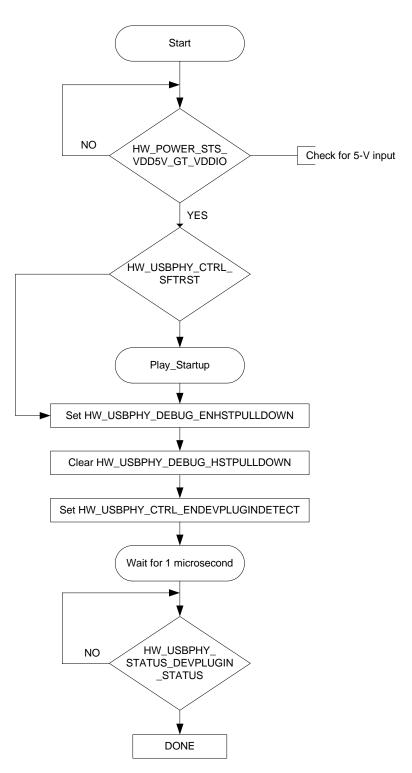

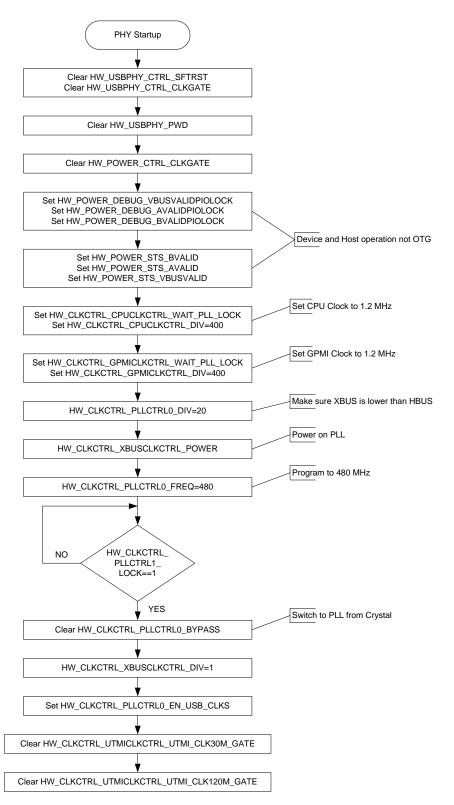

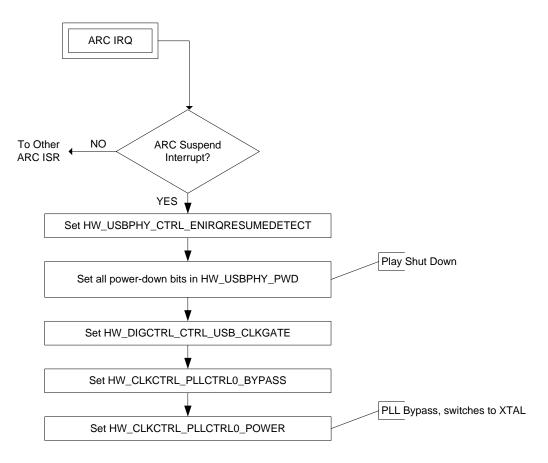

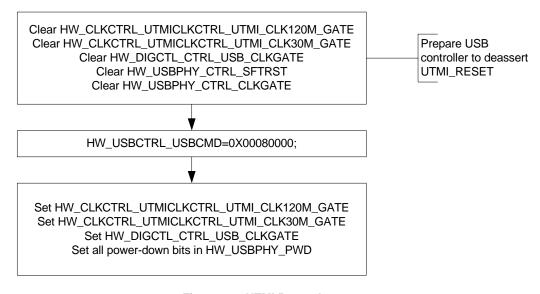

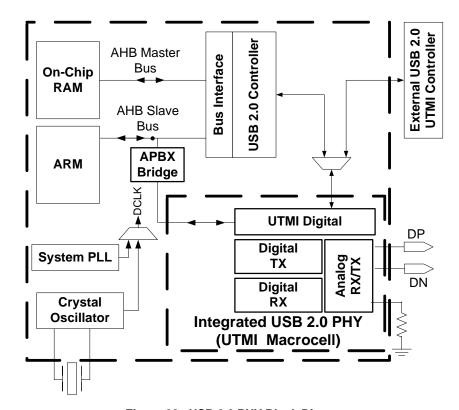

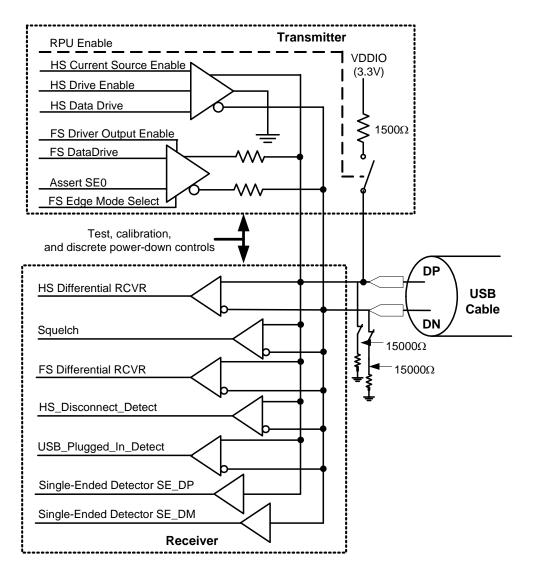

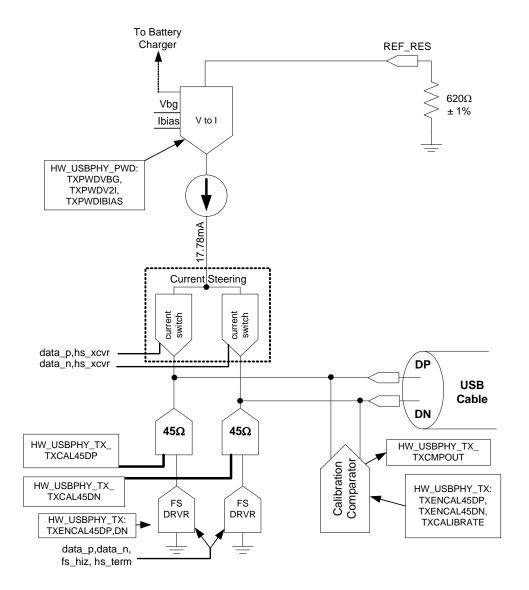

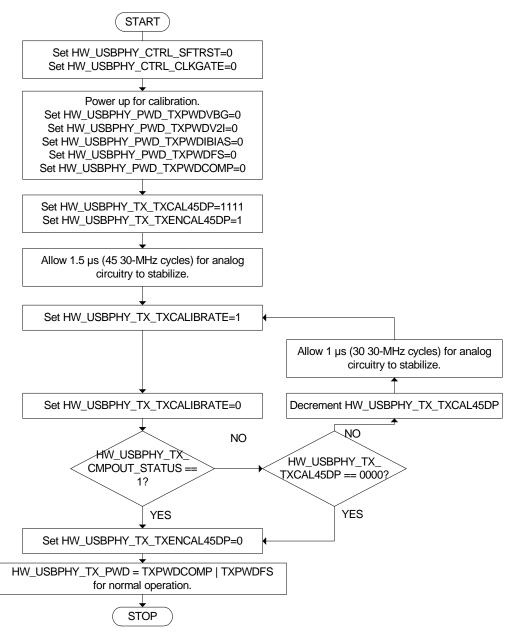

|    | 4.7. Integrated USB 2.0 PHY Initialization Flow Charts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|    | 4.8. Clocking During Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|    | 4.9. Programmable Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56  |

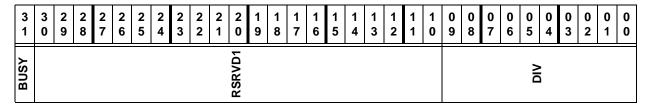

|    | 4.9.1. PLL Control Register 0 Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56  |

|    | 4.9.2. PLL Control Register 1 Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

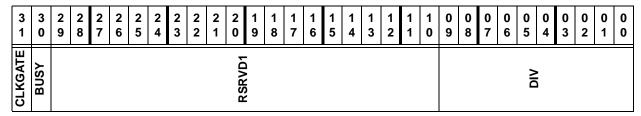

|    | 4.9.3. CPU Clock Control Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

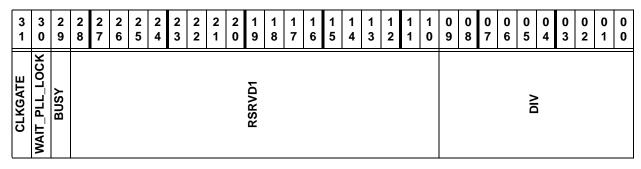

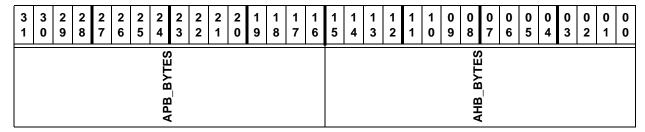

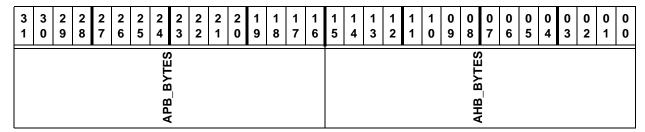

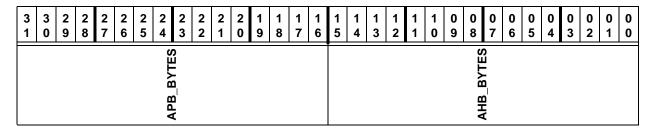

|    | 4.9.4. AHB, APBH Bus Clock Control Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50  |

|    | 4.9.5. APBX Clock Control Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61  |

|    | 4.9.5. APBA Clock Control Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 01  |

|    | 4.9.6. XTAL Clock Control Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 62  |

|    | 4.9.7. On-Chip SRAM Clock Control Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|    | 4.9.8. UTMI Clock Control Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63  |

|    | 4.9.9. Synchronous Serial Port Clock Control Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 64  |

|    | 4.9.10. General-Purpose Media Interface Clock Control Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 65  |

|    | 4.9.11. SPDIF Clock Control Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|    | 4.9.12. EMI Clock Control Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|    | 4.9.13. IR Clock Control Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 67  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

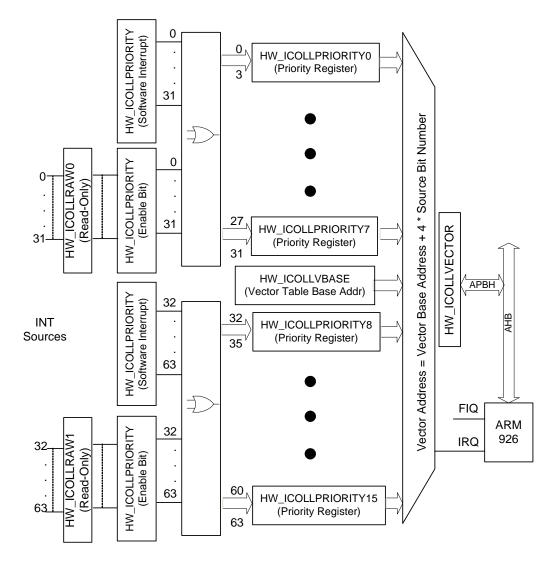

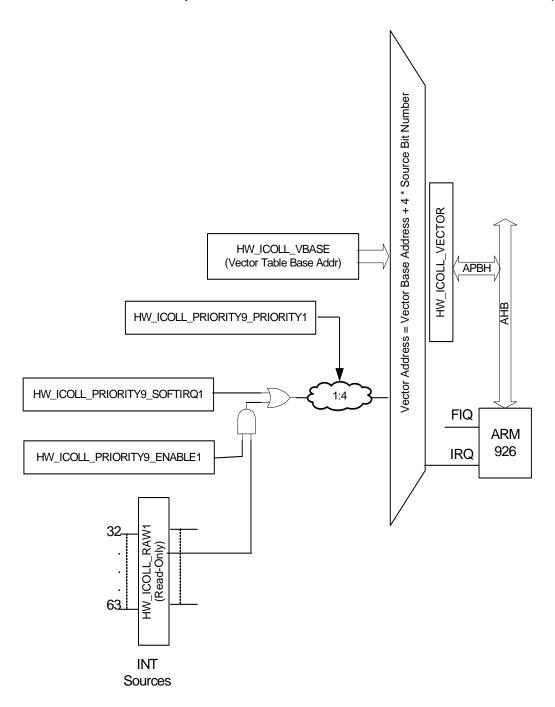

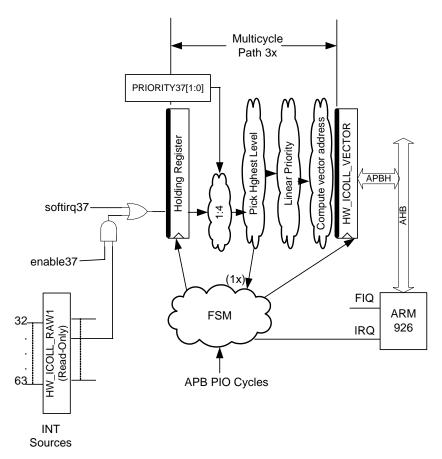

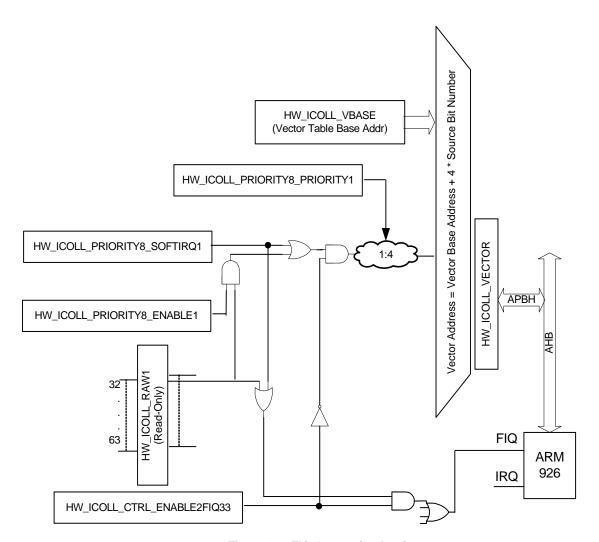

| 5. | INTERRUPT COLLECTOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 69  |

|    | 5.1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

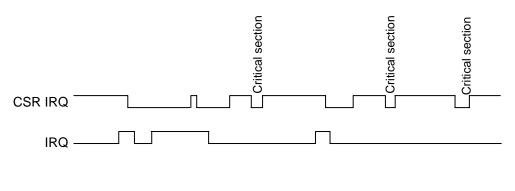

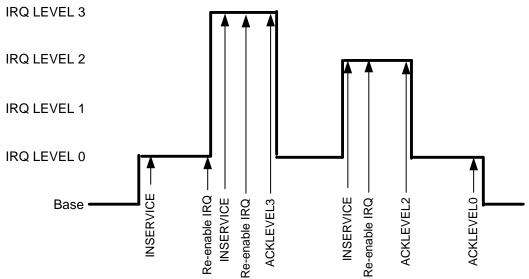

|    | 5.2. Nesting of Multi-Level IRQ Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72  |

|    | 5.2. Nesting of waiting the regular state of the state of | 12  |

|    | 5.3. FIQ Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | / 3 |

|    | 5.4. Interrupt Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|    | 5.5. CPU Wait-for-Interrupt Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 77  |

|    | 5.6. Behavior During Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77  |

|    | 5.7. Programmable Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

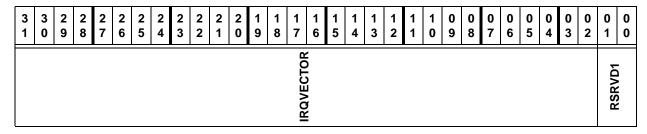

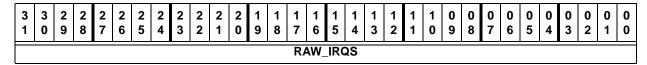

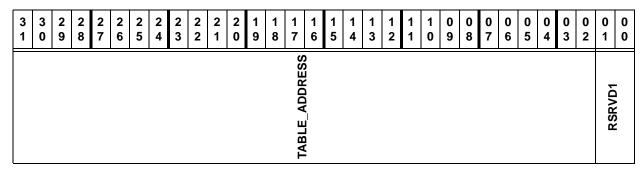

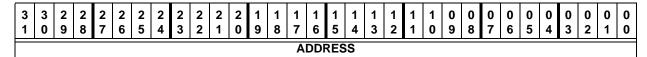

|    | 5.7.1. Interrupt Collector Interrupt Vector Address Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78  |

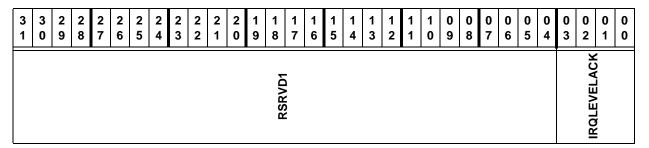

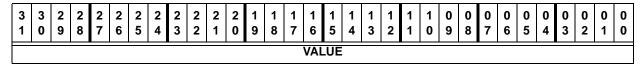

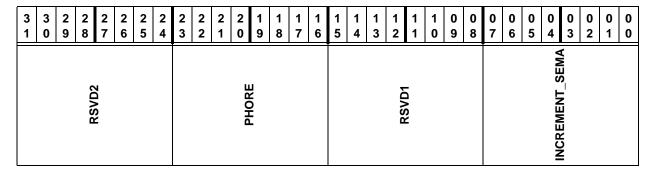

|    | 5.7.2. Interrupt Collector Level Acknowledge Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 79  |

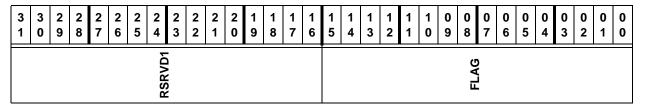

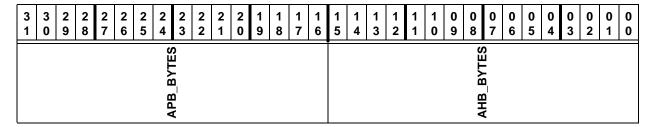

|    | 5.7.3. Interrupt Collector Control Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 70  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

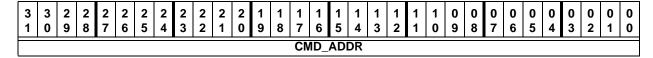

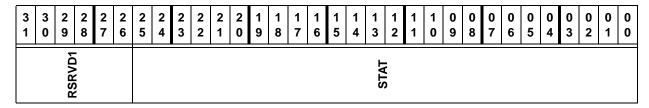

|    | 5.7.4. Interrupt Collector Status Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 81  |