# Index of /ds/FA/

|             | Name               | Last modified   | Size | Description |

|-------------|--------------------|-----------------|------|-------------|

| •           | Parent Directory   |                 |      |             |

| <u> </u>    | FAN1084.pdf        | 22-Dec-99 00:03 | 45K  |             |

| <u> </u>    | FAN1086.pdf        | 27-Jan-00 00:00 | 45K  |             |

| <u>[</u> ]  | FAN1581.pdf        | 02-Feb-00 00:00 | 63K  |             |

| <u>[</u> ]_ | FAN1582.pdf        | 11-Feb-00 00:00 | 66K  |             |

| <u>[</u> ]_ | FAN4040.pdf        | 02-Feb-00 00:00 | 14K  |             |

| <u>[</u> ]_ | FAN4050.pdf        | 27-Jan-00 00:00 | 38K  |             |

| <u>[</u> ]_ | FAN5061.pdf        | 14-Sep-99 00:00 | 149K |             |

| <u>[</u> ]_ | FAN5201.pdf        | 28-Jan-00 00:00 | 122K |             |

| <u>[</u> ]_ | FAN8024D.pdf       | 10-Jan-00 17:01 | 193K |             |

| <u>[</u> ]_ | FAN8026D.pdf       | 10-Jan-00 17:01 | 343K |             |

| <u>[</u> ]  | FAN8037.pdf        | 10-Jan-00 17:01 | 396K |             |

| <u>[</u> ]_ | FAN8038.pdf        | 10-Jan-00 17:01 | 178K |             |

| <u>[</u> ]  | FAN8725.pdf        | 10-Jan-00 17:01 | 264K |             |

| [``         | <u>FAN8800.pdf</u> | 10-Jan-00 17:01 | 99K  |             |

# **FAN1084** 4.5A Adjustable/Fixed Low Dropout Linear Regulator

### Features

- · Fast transient response

- Low dropout voltage at up to 4.5A

- Load regulation: 0.5% typical

AIRCHILD

SEMICONDUCTOR IM

- On-chip thermal limiting

- · Standard TO-220 and TO-263 center cut packages

### **Applications**

- Desktop PCs, RISC and embedded processors' supply

- GTL, SSTL logic Reference bus supply

- Low voltage VCC logic supply

- Battery-powered circuitry

- Post regulator for switching supply

- Cable and ADSL modems' DSP core supply

- · Set Top Boxes and Web Boxes modules' supply

# Description

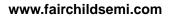

The FAN1084 and FAN1084-1.5 are low dropout three-terminal regulators with 4.5A output current capability. These devices have been optimized for low voltage applications including V<sub>TT</sub> bus termination, where transient response and minimum input voltage are critical. The FAN1084 is ideal for low voltage microprocessor applications requiring a regulated output from 1.5V to 3.6A with an input supply of 5V or less. The FAN1084-1.5 offers fixed 1.5V with 4.5A current capabilities for GTL+ bus V<sub>TT</sub> termination.

On-chip thermal limiting provides protection against any combination of overload and ambient temperature that would create excessive junction temperatures.

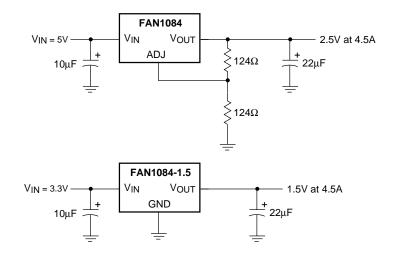

The FAN1084 series regulators are available in the industrystandard TO-220 and TO-263 center cut power packages.

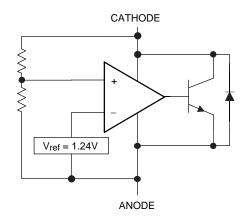

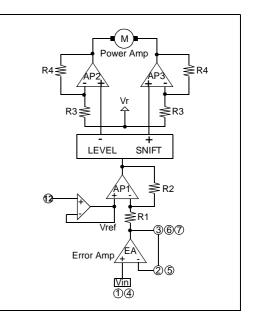

# **Block Diagram**

Rev. 0.8.1

### **Pin Assignments**

\*With package soldered to 0.5 square inch copper area over backside ground plane or internal power plane,  $\Theta_{JA}$  can vary from 30°C/W to more than 40°C/W. Other mounting techniques may provide better power dissipation than 30°C/W.

# **Absolute Maximum Ratings**

| Parameter                                | Min. | Max. | Unit |

|------------------------------------------|------|------|------|

| VIN                                      |      | 7    | V    |

| Operating Junction Temperature Range     | 0    | 125  | °C   |

| Storage Temperature Range                | -65  | 150  | °C   |

| Lead Temperature (Soldering, 10 seconds) |      | 300  | °C   |

### **Electrical Characteristics**

Operating Conditions:  $4.75 \le V_{IN} < 5.25V$ ,  $T_j = 25^{\circ}C$  unless otherwise specified.

| Parameter                         | Conditions                              | Min.  | Тур.  | Max   | Units |

|-----------------------------------|-----------------------------------------|-------|-------|-------|-------|

| Reference Voltage <sup>3</sup>    | Adj connected to ground, IOUT = 10mA    | 1.23  | 1.250 | 1.27  | V     |

| Output Voltage <sup>5</sup>       | IOUT = 10mA                             | 1.475 | 1.5   | 1.525 | V     |

| Line Regulation <sup>1, 2</sup>   | IOUT = 10mA                             |       | 0.5   | 2     | %     |

| Load Regulation <sup>1, 2</sup>   | $10mA \le I_{OUT} \le 4.5A$             |       | 0.5   | 2.5   | %     |

| Dropout Voltage                   | $\Delta VREF = 2\%$ , IOUT = 4.5A       |       |       | 1.5   | V     |

| Current Limit                     | $(V_{IN} - V_{OUT}) = 2V$               |       | 5.5   |       | A     |

| Adjust Pin Current <sup>3</sup>   |                                         |       | 35    | 100   | μA    |

| Mimimum Load Current <sup>4</sup> | $1.5V \le (V_{IN} - V_{OUT}) \le 5.75V$ |       | 10    |       | mA    |

| Quiescent Current <sup>4</sup>    | VIN = 5V                                |       | 4     |       | mA    |

| Thermal Resistance,               | TO-220                                  |       | 3     |       | °C/W  |

| Junction to Case                  | TO-263                                  |       | 10    |       | °C/W  |

| Thermal Shutdown <sup>4</sup>     |                                         |       | 150   |       | °C    |

#### Notes:

1. See thermal regulation specifications for changes in output voltage due to heating effects. Load and line regulation are measured at a constant junction temperature by low duty cycle pulse testing.

2. Line and load regulation are guaranteed up to the maximum power dissipation. Power dissipation is determined by input/ output differential and the output currrent. Guaranteed maximum output power will not be available over the full input/output voltage range.

- 3. FAN1084 only.

- 4. Guaranteed by design.

- 5. FAN1084-1.5 only.

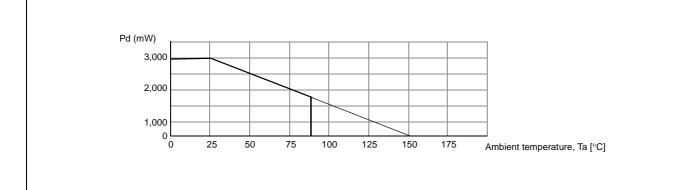

### **Typical Performance Characteristics**

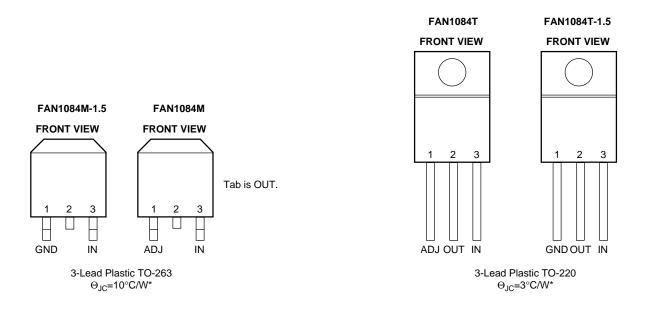

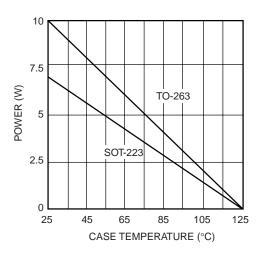

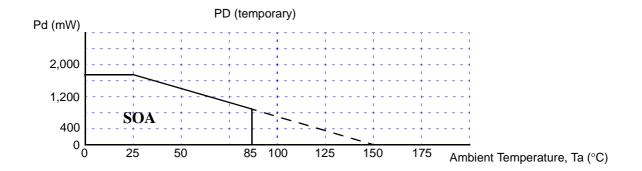

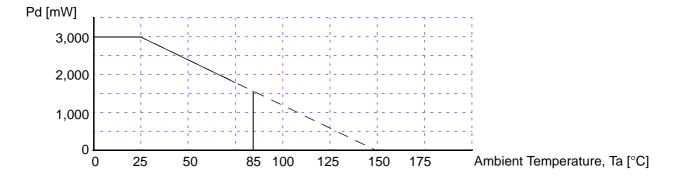

CASE TEMPERATURE

Figure 1. Maximum Power Dissipation

### **Applications Information**

#### General

The FAN1084 and FAN1084-1.5 are three-terminal regulators optimized for GTL+ V<sub>TT</sub> termination and logic applications. These devices are short-circuit protected, and offer thermal shutdown to turn off the regulator when the junction temperature exceeds about 150°C. The FAN1084 series provides low dropout voltage and fast transient response. Frequency compensation uses capacitors with low ESR while still maintaining stability. This is critical in addressing the needs of low voltage high speed microprocessor buses like GTL+.

#### Stability

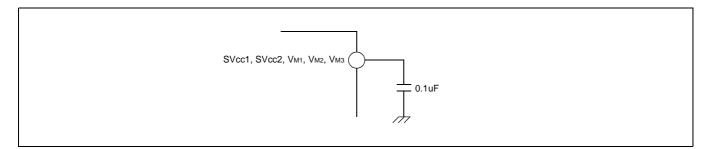

The FAN1084 series requires an output capacitor as a part of the frequency compensation. It is recommended to use a 22µF solid tantalum or a 100µF aluminum electrolytic on the output to ensure stability. The frequency compensation of these devices optimizes the frequency response with low ESR capacitors. In general, it is suggested to use capacitors with an ESR of <1 $\Omega$ . It is also recommended to use bypass capacitors such as a 22µF tantalum or a 100µF aluminum on the adjust pin of the FAN1084 for low ripple and fast transient response. When these bypassing capacitors are not used at the adjust pin, smaller values of output capacitors provide equally good results.

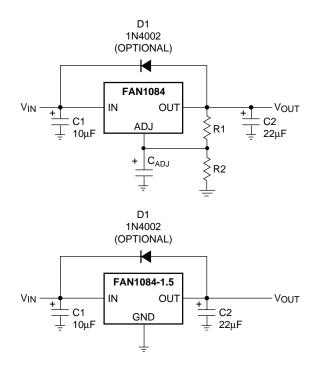

#### **Protection Diodes**

In normal operation, the FAN1084 series does not require any protection diodes. For the FAN1084, internal resistors limit internal current paths on the adjust pin. Therefore, even with bypass capacitors on the adjust pin, no protection diode is needed to ensure device safety under short-circuit conditions.

A protection diode between the input and output pins is usually not needed. An internal diode between the input and the output pins on the FAN1084 series can handle microsecond surge currents of 50A to 100A. Even with large value output capacitors it is difficult to obtain those values of surge currents in normal operation. Only with large values of output capacitance, such as  $1000\mu$ F to  $5000\mu$ F, and with the input pin instantaneously shorted to ground can damage occur. A crowbar circuit at the input to input is then recommended, as shown in Figure 2. Usually, normal power supply cycling or system "hot plugging and unplugging" will not generate current large enough to do any damage.

The adjust pin can be driven on a transient basis  $\pm 7V$  with respect to the ouput, without any device degradation. As with any IC regulator, exceeding the maximum input-to-output voltage differential causes the internal transistors to break down and none of the protection circuitry is then functional.

Figure 2. Optional Protection

#### **Ripple Rejection**

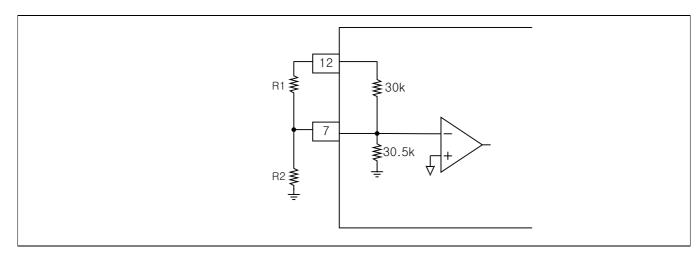

In applications that require improved ripple rejection, a bypass capacitor from the adjust pin of the FAN1084 to ground reduces the output ripple by the ratio of V<sub>OUT</sub>/1.25V. The impedance of the adjust pin capacitor at the ripple frequency should be less than the value of R1 (typically in the range of 100 $\Omega$  to 120 $\Omega$ ) in the feedback divider network in Figure 2. Therefore, the value of the required adjust pin capacitor is a function of the input ripple frequency. For example, if R1 equals 100 $\Omega$  and the ripple frequency equals 120Hz, the adjust pin

capacitor should be 22µF. At 10kHz, only 0.22µF is needed.

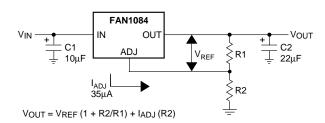

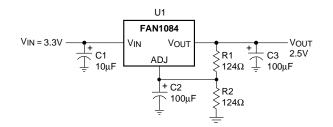

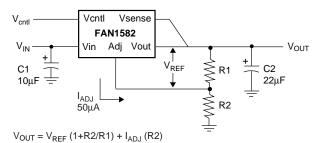

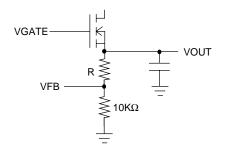

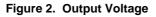

#### **Output Voltage**

The FAN1084 regulator develops a 1.25V reference voltage between the ouput pin and the adjust pin (see Figure 3). Placing a resistor R1 between these two terminals causes a constant current to flow through R1 and down through R2 to set the overall output voltage. Normally, this current is the specified minimum load current of 10mA.

Figure 3. Basic Regulation Circuit

#### Load Regulation

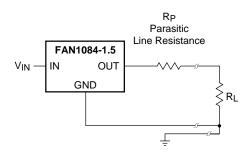

It is not possible to provide true remote load sensing because the FAN1084 series are three-terminal devices. Load regulation is limited by the resistance of the wire connecting the regulator to the load. Load regulation per the data sheet specification is measured at the bottom of the package.

For fixed voltage devices, negative side sensing is a true Kelvin connection with the ground pin of the device returned to the negative side of the load. This is illustrated in Figure 4.

Figure 4. Connection for Best Load Regulation

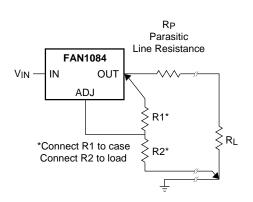

For adjustable voltage devices, negative side sensing is a true Kelvin connection with the bottom of the output divider returned to the negative side of the load. The best load regulation is obtained when the top of the resistor divider R1 connects directly to the regulator output and not to the load. Figure 5 illustrates this point.

If R1 connects to the load, then the effective resistance between the regulator and the load would be:

$R_P X (1 + R2/R1), R_P = Parasitic Line Resistance$

The connection shown in Figure 5 does not multiply Rp by the divider ration. As an example, Rp is about four milliohms per foot with 16-gauge wire. This translates to 4mV per foot at 1A load current. At higher load currents, this drop represents a significant percentage of the overall regulation. It is important to keep the positive lead between the regulator and the load as short as possible and to use large wire or PC board traces.

#### Figure 5. Connection for Best load Regulation

#### **Thermal Conditions**

The FAN1084 series protect themselves under overload conditions with internal power and thermal limiting circuitry. However, for normal continuous load conditions, do not exceed maximum junction temperature ratings. It is important to consider all sources of thermal resistance from junction-to-ambient. These sources include the junction-to-case resistance, the case-to-heatsink interface resistance, and the heat sink resistance. Thermal resistance specifications have been developed to more accurately reflect device temperature and ensure safe operating temperatures. The electrical characteristics section provides a separate thermal resistance and maximum junction temperature for both the control circuitry and the power transistor. Calculate the maximum junction temperature for both sections to ensure that both thermal limits are met.

For example, look at using an FAN1084T to generate 4.5A @ 1.5V from a 3.3V source (3.2V to 3.6V).

#### Assumptions

- VIN = 3.6V worst case

- VOUT = 1.475V worst case

- IOUT = 4.5A continuous

- $T_A = 60^{\circ}C$

- θ<sub>Case-to-Ambient</sub> = 5°C/W (assuming both a heatsink and a thermally conductive material)

The power dissipation in this application is: PD = (VIN - VOUT) \* (IOUT) = (3.6 - 1.475) \* (4.5) = 9.6W

From the specification table:

$TJ = TA + (PD) * (\theta_{Case-to-Ambient} + \theta_{JC})$ = 60 + (9.6) \* (5 + 3) = 137°C

The junction temperature is below the maximum thermal limit.

Junction-to-case thermal resistance is specified from the IC junction to the bottom of the case directly below the die. This is the lowest resistance path for heat flow. Proper mounting ensures the best thermal flow from this area of the package to the heat sink. Use of a thermally conductive material at the

case-to-heat sink interface is recommended. Use a thermally conductive spacer if the case of the device must be electrically isolated and include its contribution to the total thermal resistance. The cases of the FAN1084 series are directly connected to the output of the device.

#### **Figure 6. Application Circuit**

#### Table 1. Bill of Materials for Application Circuit for the FAN1084

| ltem   | Quantity | Manufacturer | Part Number | Description         |

|--------|----------|--------------|-------------|---------------------|

| C1     | 1        | Xicon        | L10V10      | 10µF, 10V Aluminum  |

| C2, C3 | 2        | Xicon        | L10V100     | 100µF, 10V Aluminum |

| R1, R2 | 2        | Generic      |             | 124Ω, 1%            |

| U1     | 1        | Fairchild    | FAN1084T    | 4.5A Regulator      |

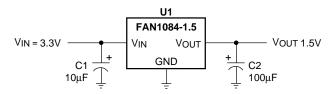

Figure 7. Application Circuit (FAN1084-1.5)

Table 2. Bill of Materials for Application Circuit for the FAN1084-1.5

| ltem | Quantity | Manufacturer | Part Number  | Description         |

|------|----------|--------------|--------------|---------------------|

| C1   | 1        | Xicon        | L10V10       | 10µF, 10V Aluminum  |

| C2   | 1        | Xicon        | L10V100      | 100µF, 10V Aluminum |

| U1   | 1        | Fairchild    | FAN1084T-1.5 | 4.5A Regulator      |

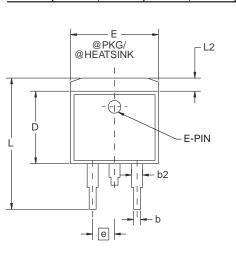

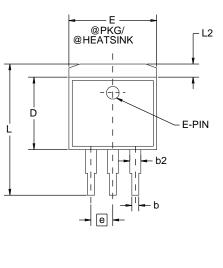

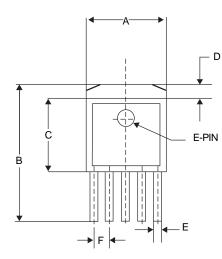

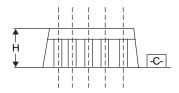

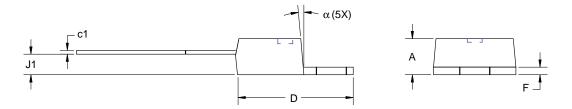

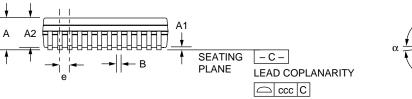

### **Mechanical Dimensions**

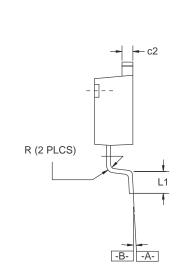

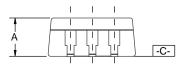

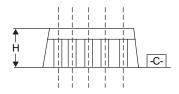

#### 3-Lead TO-263 Center Cut Package

| Symbol | Inc  | Inches |       | Millimeters |       |  |

|--------|------|--------|-------|-------------|-------|--|

|        | Min. | Max.   | Min.  | Max.        | Notes |  |

| А      | .160 | .190   | 4.06  | 4.83        |       |  |

| b      | .020 | .039   | 0.51  | 0.99        |       |  |

| b2     | .049 | .051   | 1.25  | 1.30        |       |  |

| c2     | .045 | .055   | 1.14  | 1.40        |       |  |

| D      | .340 | .380   | 8.64  | 9.65        |       |  |

| E      | .380 | .405   | 9.65  | 10.29       |       |  |

| е      | .100 | BSC    | 2.54  | BSC         |       |  |

| L      | .575 | .625   | 14.61 | 15.88       |       |  |

| L1     | .090 | .110   | 2.29  | 2.79        |       |  |

| L2     | _    | .055   |       | 1.40        |       |  |

| R      | .017 | .019   | 0.43  | 0.48        |       |  |

| α      | 0°   | 8°     | 0°    | 8°          |       |  |

### Notes:

- 1. Dimensions are exclusive of mold flash and metal burrs.

- 2. Standoff-height is measured from lead tip with ref. to Datum -B-.

- Foot length ismeasured with ref. to Datum -A- with lead surface (at inner R).

- 4. Dimension exclusive of dambar protrusion or intrusion.

- 5. Formed leads to be planar with respect to one another at seating place -C-.

#### PRODUCT SPECIFICATION

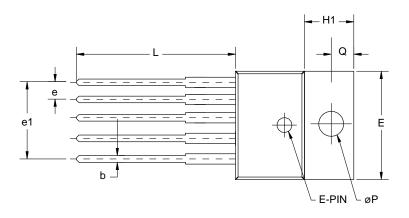

### Mechanical Dimensions (continued)

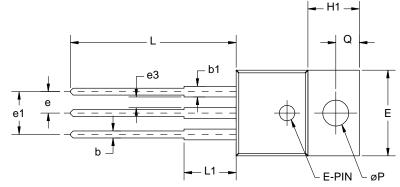

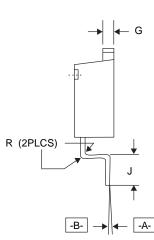

### 3-Lead TO-220 Package

| Symbol | Incl | hes        | Millim   | Notes      |       |

|--------|------|------------|----------|------------|-------|

|        | Min. | Max.       | Min.     | Max.       | Notes |

| A      | .140 | .190       | 3.56     | 4.83       |       |

| b      | .015 | .040       | .38      | 1.02       |       |

| b1     | .045 | .070       | 1.14     | 1.78       |       |

| c1     | .014 | .022       | .36      | .56        |       |

| øP     | .139 | .161       | 3.53     | 4.09       |       |

| D      | .560 | .650       | 14.22    | 16.51      |       |

| E      | .380 | .420       | 9.65     | 10.67      |       |

| е      | .090 | .110       | 2.29     | 2.79       |       |

| e1     | .190 | .210       | 4.83     | 5.33       |       |

| e3     | .045 | _          | 1.14     | —          |       |

| F      | .020 | .055       | .51      | 1.40       |       |

| H1     | .230 | .270       | 5.94     | 6.87       |       |

| J1     | .060 | .115       | 2.04     | 2.92       |       |

| L      | .500 | .580       | 12.70    | 14.73      |       |

| L1     | .250 | BSC        | 6.35 BSC |            |       |

| Q      | 1.00 | 1.35       | 2.54     | 3.43       |       |

| α      | 3°   | <b>7</b> ° | 3°       | <b>7</b> ° |       |

Notes:

1. Dimension c1 apply for lead finish.

### **Ordering Information**

| Product Number | Package |

|----------------|---------|

| FAN1084MC      | TO-263  |

| FAN1084T       | TO-220  |

| FAN1084MC-1.5  | TO-263  |

| FAN1084T-1.5   | TO-220  |

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

# **FAN1086** 1.5A Adjustable/Fixed Low Dropout Linear Regulator

## Features

- Low dropout voltage

- Load regulation: 0.05% typical

AIRCHILD

SEMICONDUCTOR IM

- Trimmed current limit

- On-chip thermal limiting

- Standard SOT-223 and TO-263 packages

- Three-terminal adjustable or fixed 2.5V, 2.85V, 3.3V, 5V

# Applications

- Active SCSI terminators

- High efficiency linear regulators

- Post regulators for switching supplies

- Battery chargers

- 5V to 3.3V linear regulators

- Motherboard clock supplies

# Description

The FAN1086 and FAN1086-2.5, -2.85, -3.3 and -5 are low dropout three-terminal regulators with 1.5A output current capability. These devices have been optimized for low voltage where transient response and minimum input voltage are critical. The 2.85V version is designed specifically to be used in Active Terminators for SCSI bus.

Current limit is trimmed to ensure specified output current and controlled short-circuit current. On-chip thermal limiting provides protection against any combination of overload and ambient temperatures that would create excessive junction temperatures.

Unlike PNP type regulators where up to 10% of the output current is wasted as quiescent current, the quiescent current of the FAN1086 flows into the load, increasing efficiency.

The FAN1086 series regulators are available in the industrystandard SOT-223 and TO-263 power packages.

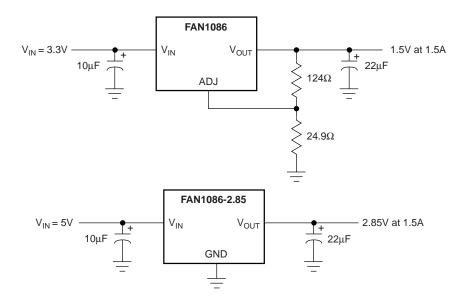

# **Typical Applications**

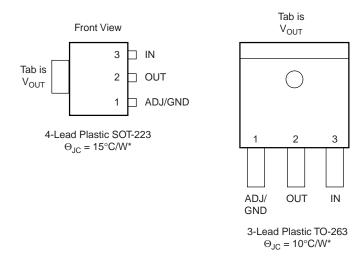

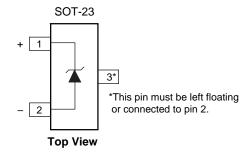

### **Pin Assignments**

\*With package soldered to 0.5 square inch copper area over backside ground plane or internal power plane.,  $\Theta_{JA}$  can vary from 30°C/W to more than 50°C/W. Other mounting techniques may provide better thermal resistance than 30°C/W.

# **Absolute Maximum Ratings**

| Parameter                             | Min. | Max. | Unit |

|---------------------------------------|------|------|------|

| V <sub>IN</sub>                       |      | 7.5  | V    |

| Operating Junction Temperature Range  | 0    | 125  | °C   |

| Storage Temperature Range             | -65  | 150  | °C   |

| Lead Temperature (Soldering, 10 sec.) |      | 300  | °C   |

# **Electrical Characteristics**

Operating Conditions:  $V_{IN} \le 7V$ ,  $T_J = 25^{\circ}C$  unless otherwise specified. The • denotes specifications which apply over the specified operating temperature range.

| Parameter                                    | Conditions                                                                                                                                                                                                                                                                     | Min. | Тур.                             | Max.                      | Units                            |                  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------|---------------------------|----------------------------------|------------------|

| Reference Voltage <sup>3</sup>               | $\begin{array}{l} 1.5V \leq (V_{\text{IN}} - V_{\text{OUT}}) \leq 5.75V, \\ 10\text{mA} \leq I_{\text{OUT}} \leq 1\text{A} \end{array}$                                                                                                                                        | •    | 1.225<br>(-2%)                   | 1.250                     | 1.275<br>(+2%)                   | V                |

| Output Voltage                               | $\begin{array}{ c c c c c c c } & 10mA \leq I_{OUT} \leq 1A \\ \hline FAN1086-2.5, \ 4V \leq V_{IN} \leq 7V \\ \hline FAN1086-2.85, \ 4.35V \leq V_{IN} \leq 7V \\ \hline FAN1086-3.3, \ 4.8V \leq V_{IN} \leq 7V \\ \hline FAN1086-5, \ 6.5V \leq V_{IN} \leq 7V \end{array}$ | •    | 2.450<br>2.793<br>3.234<br>4.900 | 2.5<br>2.85<br>3.3<br>5.0 | 2.550<br>2.907<br>3.366<br>5.100 | V<br>V<br>V<br>V |

| Line Regulation <sup>1,2</sup>               | $(V_{OUT} + 1.5V) \le V_{IN} \le 7V, I_{OUT} = 10mA$                                                                                                                                                                                                                           | •    |                                  | 0.005                     | 0.2                              | %                |

| Load Regulation <sup>1,2</sup>               | $(V_{IN} - V_{OUT}) = 2V, 10mA \le I_{OUT} \le 1A$                                                                                                                                                                                                                             | •    |                                  | 0.05                      | 0.5                              | %                |

| Dropout Voltage                              | ΔV <sub>REF</sub> = 1%, I <sub>OUT</sub> = 1.5A                                                                                                                                                                                                                                | •    |                                  | 1.300                     | 1.500                            | V                |

| Current Limit                                | $(V_{IN} - V_{OUT}) = 2V$                                                                                                                                                                                                                                                      | •    | 1.6                              | 2.0                       |                                  | A                |

| Adjust Pin Current <sup>3</sup>              |                                                                                                                                                                                                                                                                                | •    |                                  | 35                        | 120                              | μA               |

| Adjust Pin Current Change <sup>3</sup>       | $\begin{array}{l} 1.5V \leq (V_{\text{IN}} - V_{\text{OUT}}) \leq 5.75, \\ 10\text{mA} \leq I_{\text{OUT}} \leq 1\text{A} \end{array}$                                                                                                                                         | •    |                                  | 0.2                       | 5                                | μΑ               |

| Minimum Load Current                         | $1.5V \le (V_{IN} - V_{OUT}) \le 5.75$                                                                                                                                                                                                                                         | •    | 10                               |                           |                                  | mA               |

| Quiescent Current                            | $V_{IN} = V_{OUT} + 1.25V$                                                                                                                                                                                                                                                     | •    |                                  | 4                         | 13                               | mA               |

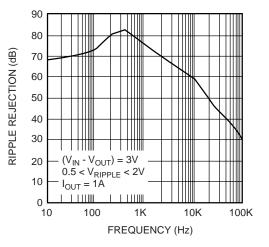

| Ripple Rejection                             | f = 120Hz, $C_{OUT}$ = 22µF Tantalum,<br>( $V_{IN} - V_{OUT}$ ) = 3V, $I_{OUT}$ = 1.5A                                                                                                                                                                                         |      | 60                               | 72                        |                                  | dB               |

| Thermal Regulation                           | $T_A = 25^{\circ}C$ , 30ms pulse                                                                                                                                                                                                                                               |      |                                  | 0.004                     | 0.02                             | %/W              |

| Temperature Stability                        |                                                                                                                                                                                                                                                                                | •    |                                  | 0.5                       |                                  | %                |

| Long-Term Stability                          | T <sub>A</sub> = 125°C, 1000hrs.                                                                                                                                                                                                                                               |      |                                  | 0.03                      | 1.0                              | %                |

| RMS Output Noise<br>(% of V <sub>OUT</sub> ) | $T_A = 25^{\circ}C$ , $10Hz \le f \le 10kHz$                                                                                                                                                                                                                                   |      |                                  | 0.003                     |                                  | %                |

| Thermal Resistance,                          | SOT-223                                                                                                                                                                                                                                                                        |      |                                  | 15                        |                                  | °C/W             |

| Juncation to Case                            | TO-263                                                                                                                                                                                                                                                                         |      |                                  | 10                        |                                  | °C/W             |

| Thermal Shutdown                             | Junction Temperature                                                                                                                                                                                                                                                           |      |                                  | 155                       |                                  | °C               |

| Thermal Shutdown<br>Hysteresis               |                                                                                                                                                                                                                                                                                |      |                                  | 10                        |                                  | °C               |

Notes:

1. See thermal regulation specifications for changes in output voltage due to heating effects. Load and line regulation are measured at a constant junction temperature by low duty cycle pulse testing.

Line and load regulation are guaranteed up to the maximum power dissipation (18W). Power dissipation is determined by input/output differential and the output current. Guaranteed maximum output power will not be available over the full input/ output voltage range.

3. FAN1086 only.

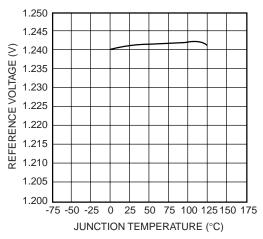

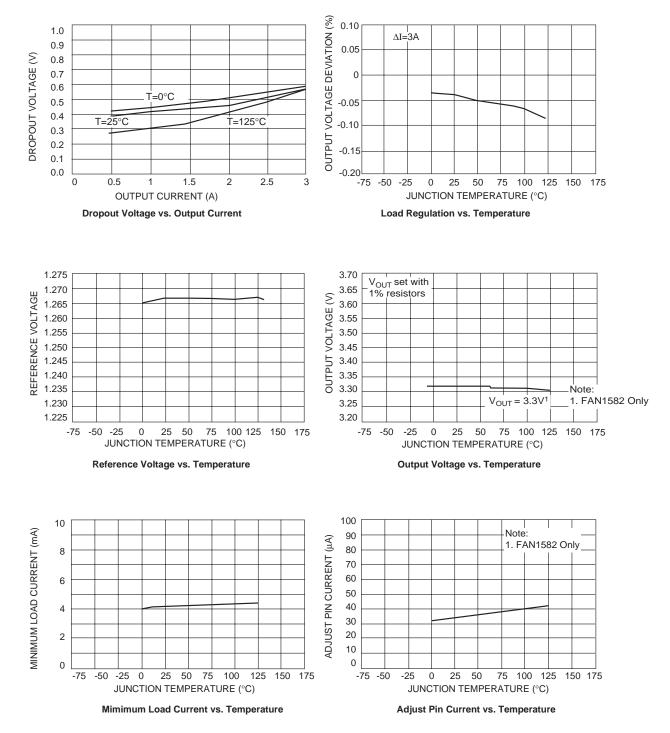

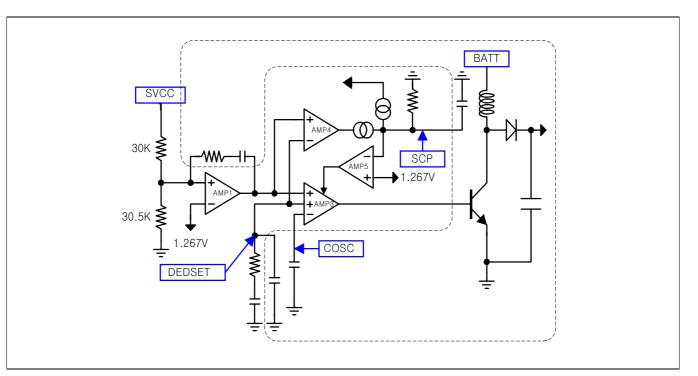

**Typical Performance Characteristics**

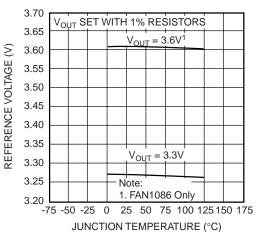

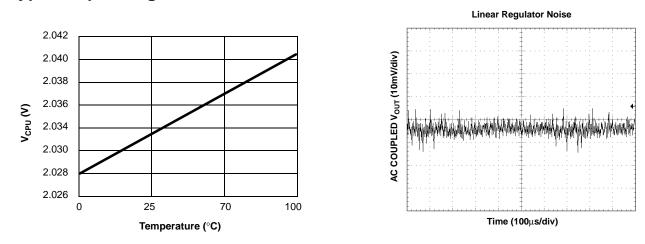

Figure 3. Reference Voltage vs. Temperature

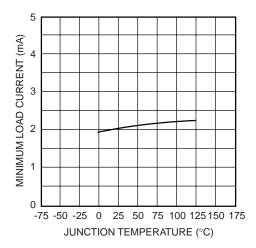

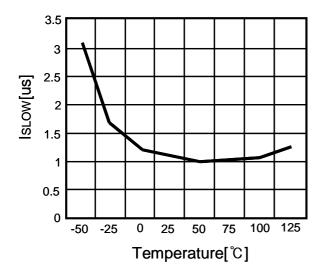

Figure 5. Minimum Load Current vs. Temperature

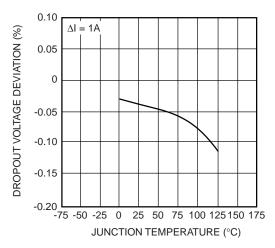

Figure 2. Load Regulation vs. Temperature

Figure 4. Output Voltage vs. Temperature

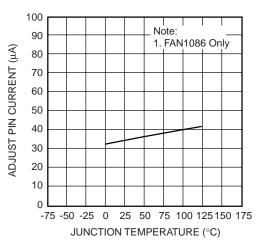

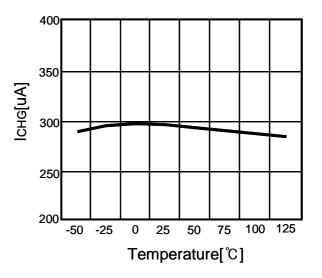

Figure 6. Adjust Pin Current vs. Temperature

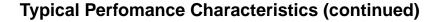

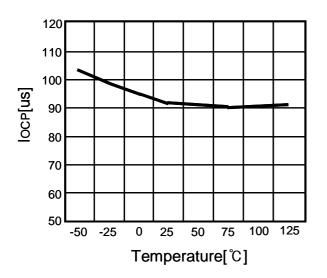

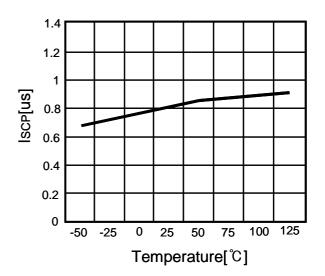

### Typical Performance Characteristics (continued)

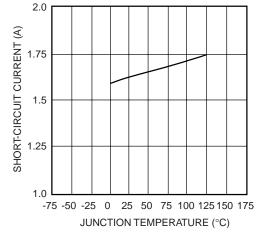

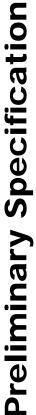

Figure 7. Short-Circuit Current vs. Temperature

Figure 8. Ripple Rejection vs. Frequency

Figure 9. Maximum Power Dissipation

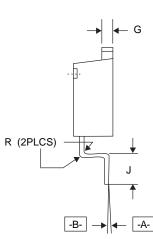

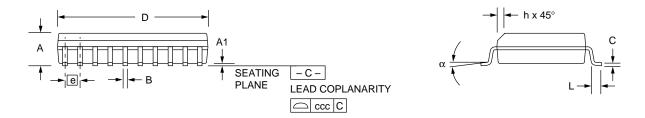

# **Mechanical Dimensions**

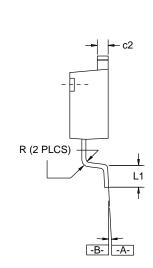

### 3-Lead TO-263 Package

| Cumhal | Inc  | Inches |       | Millimeters |       |

|--------|------|--------|-------|-------------|-------|

| Symbol | Min. | Max.   | Min.  | Max.        | Notes |

| A      | .160 | .190   | 4.06  | 4.83        |       |

| b      | .020 | .039   | 0.51  | 0.99        |       |

| b2     | .049 | .051   | 1.25  | 1.30        |       |

| c2     | .045 | .055   | 1.14  | 1.40        |       |

| D      | .340 | .380   | 8.64  | 9.65        |       |

| E      | .380 | .405   | 9.65  | 10.29       |       |

| е      | .100 | BSC    | 2.54  | BSC         |       |

| L      | .575 | .625   | 14.61 | 10.88       |       |

| L1     | .090 | .100   | 2.29  | 2.79        |       |

| L2     | _    | .055   | _     | 1.40        |       |

| R      | .017 | .019   | 0.43  | 0.48        |       |

| α      | 0°   | 8°     | 0°    | 8°          |       |

### Notes:

- 1. Dimensions are exclusive of mold flash and metal burrs.

- 2. Stand off-height is measured from lead tip with ref. to Datum -B-.

- 3. Foot length is measured with ref. to Datum -A- with lead surface (at inner R).

- 4. Dimension exclusive of dambar protrusion or intrusion.

- 5. Formed leads to be planar with respect to one another at seating place -C-.

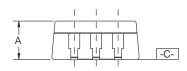

# **Mechanical Dimensions**

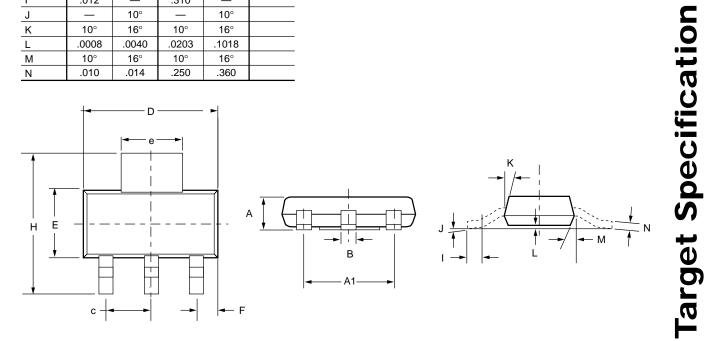

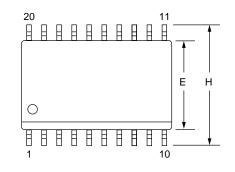

### 4-Lead SOT-223 Package

| Symbol | Inc   | hes   | Millim | Notes |       |

|--------|-------|-------|--------|-------|-------|

| Symbol | Min.  | Max.  | Min.   | Max.  | Notes |

| А      | _     | .071  |        | 1.80  |       |

| A1     |       | .181  | —      | 4.80  |       |

| В      | .025  | .033  | .640   | .840  |       |

| С      | -     | .090  | _      | 2.29  |       |

| D      | .248  | .264  | 6.30   | 6.71  |       |

| Е      | .130  | .148  | 3.30   | 3.71  |       |

| е      | .115  | .124  | 2.95   | 3.15  |       |

| F      | .033  | .041  | .840   | 1.04  |       |

| Н      | .264  | .287  | 6.71   | 7.29  |       |

| 1      | .012  | _     | .310   | —     |       |

| J      | _     | 10°   | —      | 10°   |       |

| К      | 10°   | 16°   | 10°    | 16°   |       |

| L      | .0008 | .0040 | .0203  | .1018 |       |

| М      | 10°   | 16°   | 10°    | 16°   |       |

| Ν      | .010  | .014  | .250   | .360  |       |

### **Ordering Information**

| Product Number | Package |

|----------------|---------|

| FAN1086M       | TO-263  |

| FAN1086S       | SOT-223 |

| FAN1086M-2.5   | TO-263  |

| FAN1086S-2.5   | SOT-223 |

| FAN1086M-2.85  | TO-263  |

| FAN1086S-2.85  | SOT-223 |

| FAN1086M-3.3   | TO-263  |

| FAN1086S-3.3   | SOT-223 |

| FAN1086M-5     | TO-263  |

| FAN1086S-5     | SOT-223 |

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

#### TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

ACEx<sup>TM</sup> CoolFET<sup>TM</sup> CROSSVOLT<sup>TM</sup> E<sup>2</sup>CMOS<sup>TM</sup> FACT<sup>TM</sup> FACT Quiet Series<sup>TM</sup> FAST<sup>®</sup> FAST<sup>®</sup> FASTr<sup>TM</sup> GTO<sup>TM</sup> HiSeC<sup>TM</sup> ISOPLANAR™ MICROWIRE™ POP™ PowerTrench® QFET™ QS™ Quiet Series™ SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SyncFET™ TinyLogic™ UHC™ VCX™

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user. 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **PRODUCT STATUS DEFINITIONS**

**Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                                        |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or<br>In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                |

| Preliminary              | First Production          | This datasheet contains preliminary data, and<br>supplementary data will be published at a later date.<br>Fairchild Semiconductor reserves the right to make<br>changes at any time without notice in order to improve<br>design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild<br>Semiconductor reserves the right to make changes at<br>any time without notice in order to improve design.                                                             |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product<br>that has been discontinued by Fairchild semiconductor.<br>The datasheet is printed for reference information only.                                                         |

# FAN1581 5A Adjustable/Fixed Ultra Low Dropout **Linear Regulator**

### Features

- Ultra Low dropout voltage, 0.4V typical at 5A

- Remote sense operation

-AIRCHILD

SEMICONDUCTOR IM

- Fast transient response

- Load regulation: 0.05% typical

- 0.5% initial accuracy

- On-chip thermal limiting

- · 5 Pin standard TO-220 and TO-263 packages

# Applications

- Pentium<sup>®</sup> Processors

PowerPC<sup>™</sup>, AMD K5 and K6 processors

- Pentium support of GTL+ bus supply

- Low voltage logic supply

- Embedded Processor supplies

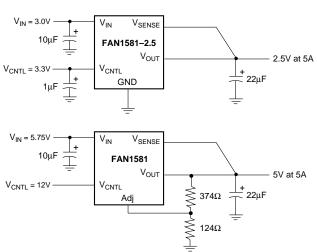

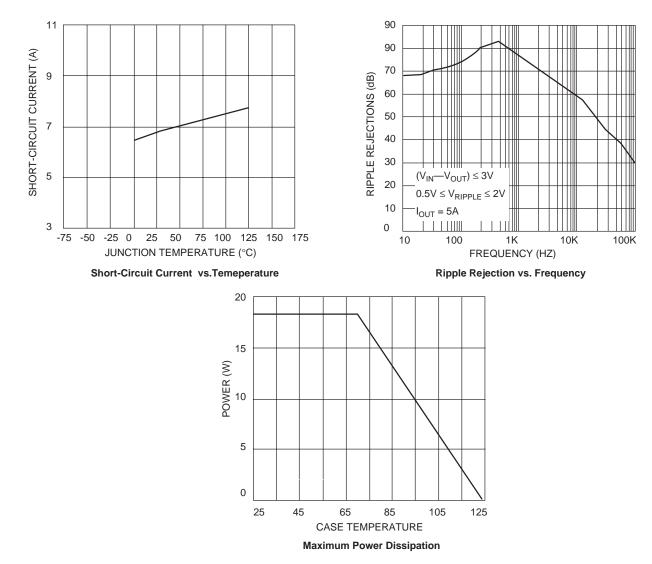

**Typical Applications**

- Split plane regulator

- New 2.5V and 1.8V Logic Families

#### Description

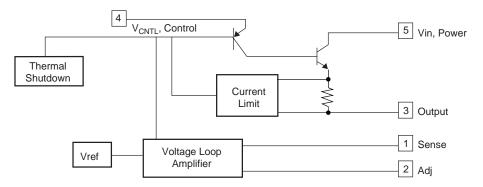

The FAN1581, FAN1581-1.5, and FAN1581-2.5 are ultra-low dropout regulators with 5A output current capability. These devices have been optimized for low voltage applications including VTT bus termination, where transient response and minimum input voltage are critical. The FAN1581 is ideal for low voltage microprocessor applications requiring a regulated output from 1.3V to 5.7V with a power input supply of 1.75V to 6.5V. The FAN1581-1.5 offers fixed 1.5V with 5A current capabilities for GTL+ bus VTT termination. The FAN1581-2.5 offers fixed 2.5V with 5A current capability for logic IC operation and processors while minimizing the overall power dissipation.

Current limit ensures controlled short-circuit current. On-chip thermal limiting provides protection against any combination of overload and ambient temperature that would create excessive junction temperatures.

The FAN1581 series regulators are available in the industrystandard 5-Pin TO-220 and TO-263 power packages.

PRELIMINARY SPECIFICATION describes products that are not in full production at time of printing. Specifications are based on design goals and limited characterization. In the process of final production release, specifications may change. Contact Fairchild Semiconductor for current information.

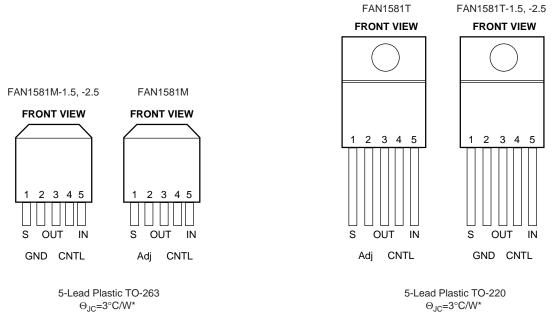

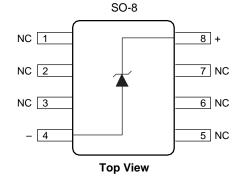

# **Pin Assignments**

\*With package soldered to 0.5 square inch copper area over backside ground plane or internal power plane. Θ<sub>JA</sub> can vary fom 20°C/W to >40°C/W with other mounting techniques.

# **Pin Definitions**

| Pin Number | Pin Name | Pin Function Descrition                                                                                                                                                  |  |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | VSense   | <b>Remote Voltage Sense</b> . Connect this pin to the load to permit true remote sensing and avoid trace drops.                                                          |  |

| 2          | ADJ/GND  | Adjust or Ground. On the FAN1581, this pin forms the feedback to determine the output voltage. On the FAN1581-1.5 and -2.5, connect this pin to ground.                  |  |

| 3          | VOUT     | Output Voltage. This pin and the tab are output.                                                                                                                         |  |

| 4          | VCNTL    | <b>Control Voltage.</b> This pin draws small-signal power to control the FAN1581 circuitry. Connect to a voltage higher than VIN, as shown in the applications circuits. |  |

| 5          | VIN      | Input Voltage.                                                                                                                                                           |  |

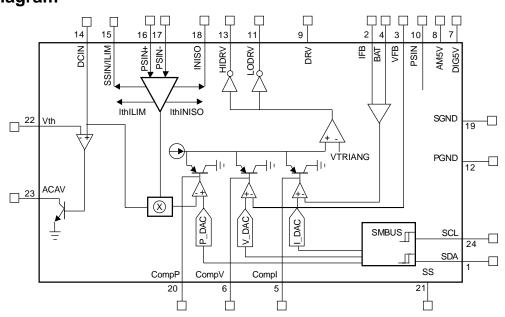

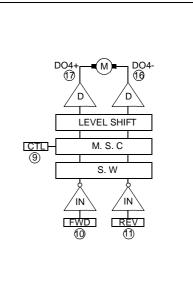

### **Internal Block Diagram**

# **Absolute Maximum Ratings**

| Parameter                             | Min. | Max. | Unit |

|---------------------------------------|------|------|------|

| VIN                                   |      | 7    | V    |

| VCNTL                                 |      | 13.2 | V    |

| Operating Junction Temperature Range  | 0    | 125  | °C   |

| Lead Temperature (Soldering, 10 sec.) |      | 300  | °C   |

| Storage Temperature Range             | -65  | 150  | °C   |

# **Electrical Characteristics**

$TJ=25^{\circ}C$ , VOUT = VS, VADJ = 0V unless otherwise specified.

The  $\bullet$  denotes specifications which apply over the specified operating temperature range.

| Parameter                                                                             | Conditions                                                                                                               |     | Min.  | Тур.  | Max.  | Units |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|-------|-------|

| Reference Voltage <sup>3</sup> $V_{IN} = 2.0V, V_{CNTL} = 2.75V,$<br>$I_{OUT} = 10mA$ |                                                                                                                          |     | 1.243 | 1.250 | 1.257 | V     |

| Reference Voltage <sup>3</sup>                                                        | $\begin{array}{l} 2.05V \leq V_{IN} \leq 5.5V, \\ 2.7V \leq V_{CNTL} \leq 12V, \\ 10mA \leq I_{OUT} \leq 5A \end{array}$ | •   | 1.237 | 1.250 | 1.263 | V     |

| Adjustable Output Voltage                                                             | $3V \le V_{IN} \le 7V$ (function of Vout),<br>10mA \le IOUT \le 5A                                                       | •   | Vref  | 1.5   | 5.7   | V     |

| Output Voltage <sup>4</sup>                                                           | $3V \le V_{IN} \le 7V$ , $10mA \le I_{OUT} \le 5A$                                                                       | •   | 1.47  | 1.5   | 1.53  | V     |

| Output Voltage <sup>5</sup>                                                           | $5.1V \le V_{IN} \le 7V$ , $10mA \le I_{OUT} \le 5A$                                                                     | •   | 2.474 | 2.5   | 2.526 | V     |

| Line Regulation <sup>1,2</sup>                                                        | $1.75V \le V_{IN} \le 5.5V, 2.5V \le V_{CNTL} \le 12V,$<br>IOUT = 10mA                                                   | , • |       | 1     | 3     | mV    |

| Load Regulation <sup>1,2</sup>                                                        | $V_{IN} = 2.1V, V_{CNTL} = 2.75V,$<br>10mA $\leq I_{OUT} \leq 5A$                                                        | •   |       | 1     | 5     | mV    |

| Dropout Voltage Minimum VCNTL                                                         | VIN = 2.05V, ΔVREF = 1%, IOUT = 5A                                                                                       | •   |       | 1.05  | 1.18  | V     |

| Dropout Voltage Minimum VIN                                                           | VCNTL = 2.75V, $\Delta$ VREF = 1%,<br>IOUT = 5A                                                                          |     |       | 0.4   | 0.5   | V     |

| Dropout Voltage Minimum VIN                                                           | VCNTL = 2.75V, $\Delta$ VREF = 1%,<br>IOUT = 5A                                                                          | •   |       | 0.5   | 0.6   | V     |

| Current Limit                                                                         | VIN = 2.05V, VCNTL = 2.75V                                                                                               | •   | 5.2   |       |       | Α     |

| Control Pin Current                                                                   | VIN = 2.05V, VCNTL = 2.75V,<br>IOUT = 10mA                                                                               | •   |       | 30    | 120   | μA    |

| Adjust Pin Current <sup>3</sup>                                                       | VIN = 2.05V, VCNTL = 2.75V                                                                                               | •   |       | 50    | 120   | mA    |

| Minimum Load Current                                                                  | VIN = 3.3V, VCNTL = 5V                                                                                                   | •   |       | 5.0   | 10    | mA    |

| Ripple Rejection                                                                      | $V_{IN} = 3.75V, V_{CNTL} = 3.75V, f = 120Hz, C_{OUT} = 22\mu F Tantalum, I_{OUT} = 2.5A$                                |     | 60    | 80    |       | dB    |

| Thermal Resistance, Junction to Case                                                  |                                                                                                                          |     |       | 3     |       | °C/W  |

| Thermal Regulation                                                                    | TA = 25°C, 30ms pulse                                                                                                    |     |       | 0.002 | 0.02  | %/W   |

| Thermal Shutdown                                                                      |                                                                                                                          |     |       | 150   |       | °C    |

#### Notes:

3. FAN1581 only.

4. FAN1581-1.5 only.

5. FAN1581-2.5 only.

<sup>1.</sup> See thermal regulation specifications for changes in output voltage due to heating effects. Load and line regulation are measured at a constant junction temperature by low duty cycle pulse testing.

<sup>2.</sup> Line and load regulation are guaranteed up to the maximum power dissipation (18W). Power dissipation is determined by input/output differential and the output current. Guaranteed maximum output power will not be available over the full input/ output voltage range.

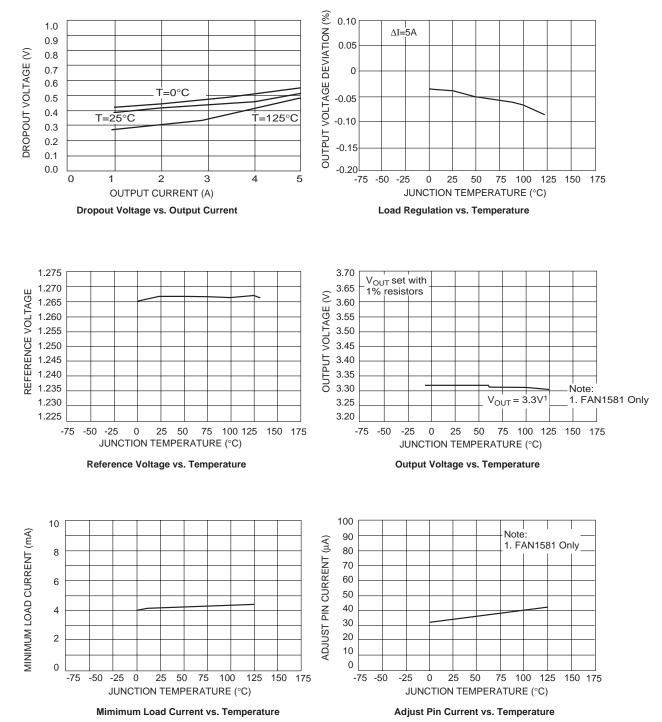

## **Typical Perfomance Characteristics**

## **Typical Perfomance Characteristics (continued)**

### General

The FAN1581, FAN1581-1.5, and FAN1581-2.5 are threeterminal regulators optimized for GTL+ VTT termination and logic applications. These devices are short-circuit protected, and offer thermal shutdown to turn off the regulator when the junction temperature exceeds about 150°C. The FAN1581 series provides low dropout voltage and fast transient response. Frequency compensation uses capacitors with low ESR while still maintaining stability. This is critical in addressing the needs of low voltage high speed microprocessor buses like GTL+.

#### Stability

The FAN1581 series requires an output capacitor as a part of the frequency compensation. It is recommended to use a  $22\mu$ F solid tantalum or a  $100\mu$ F aluminum electrolytic on the output

to ensure stability. The frequency compensation of these devices optimizes the frequency response with low ESR capacitors. In general, it is suggested to use capacitors with an ESR of <1 $\Omega$ . It is also recommended to use bypass capacitors such as a 22µF tantalum or a 100µF aluminum on the adjust pin of the FAN1581 for low ripple and fast transient response. When these bypassing capacitors are not used at the adjust pin, smaller values of output capacitors provide equally good results.

#### **Protection Diodes**

In normal operation, the FAN1581 series does not require any protection diodes. For the FAN1581, internal resistors limit internal current paths on the adjust pin. Therefore, even with bypass capacitors on the adjust pin, no protection diode is needed to ensure device safety under short-circuit conditions.

A protection diode between the input and output pins is usually not needed. An internal diode between the input and the output pins on the FAN1581 series can handle microsecond surge currents of 50A to 100A. Even with large value output capacitors it is difficult to obtain those values of surge currents in normal operation. Only with large values of output capacitance, such as  $1000\mu$ F to  $5000\mu$ F, and with the input pin instantaneously shorted to ground can damage occur. A crowbar circuit at the input can generate those levels of current; a diode from output to input is then recommended, as shown in Figure 1. Usually, normal power supply cycling or system "hot plugging and unplugging" will not generate current large enough to do any damage.

The adjust pin can be driven on a transient basis  $\pm 7V$  with respect to the output, without any device degradation. As with any IC regulator, exceeding the maximum input-to-output voltage differential causes the internal transistors to break down and none of the protection circuitry is then functional.

Figure 1. Optional Protection Diode

#### **Ripple Rejection**

In applications that require improved ripple rejection, a bypass capacitor from the adjust pin of the FAN1581 to ground reduces the output ripple by the ratio of VOUT/1.25V. The impedance of the adjust pin capacitor at the ripple frequency should be less than the value of R1 (typically in the range of  $100\Omega$  to  $120\Omega$ ) in the feedback divider network in Figure 1. Therefore, the value of the required adjust pin capacitor is a function of the input ripple frequency. For example, if R1 equals

$100\Omega$  and the ripple frequency equals 120Hz, the adjust pin capacitor should be 22µF. At 10kHz, only 0.22µF is needed.

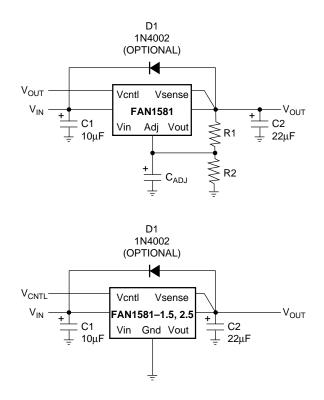

#### **Output Voltage**

The FAN1581 regulator develops a 1.25V reference voltage between the output pin and the adjust pin (see Figure 2). Placing a resistor R1 between these two terminals causes a constant current to flow through R1 and down through R2 to set the overall output voltage. Normally, this current is the specified minimum load current of 10mA.

The current out of the adjust pin adds to the current from R1 and is typically  $35\mu$ A. Its output voltage contribution is small and only needs consideration when a very precise output voltage setting is required.

Figure 2. Basic Regulator Circuit

#### Load Regulation

The FAN1581 family provides true remote sensing, eliminating output voltage errors due to trace resistance. To utilize remote sensing, connect the VSENSE pin directly to the load, rather than at the VOUT pin. If the load is more than 1" away from the FAN1581, it may be necessary to increase the load capacitance to ensure stability.

#### **Thermal Considerations**

The FAN1581 series protect themselves under overload conditions with internal power and thermal limiting circuitry. However, for normal continuous load conditions, do not exceed maximum junction temperature ratings. It is important to consider all sources of thermal resistance from junction-toambient. These sources include the junction-to-case resistance, the case-to-heat sink interface resistance, and the heat sink resistance. Thermal resistance specifications have been developed to more accurately reflect device temperature and ensure safe operating temperatures. The electrical characteristics section provides a separate thermal resistance and maximum junction temperature for both the control circuitry and the power transistor. Calculate the maximum junction temperature for both sections to ensure that both thermal limits are met.

For example, look at using an FAN1581T-1.5 to generate 5A @  $1.5V \pm 2\%$  from a 3.3V source (3.2V to 3.6V).

- Vin = 3.6V worst case

- VOUT = 1.47V worst case

- IOUT = 5A continuous

- $T_A = 40^{\circ}C$

- $\Theta$  Case-to-Ambient = 5°C/W (assuming both a heatsink and a thermally conductive material)

The power dissipation in this application is:

$$P_D = (V_{IN} - V_{OUT}) * (I_{OUT}) = (3.6-1.47) * (5) = 10.65W$$

From the specification table,

$$TJ = TA + (PD) * (\Theta \text{ Case-to-Ambient} + \Theta JC) = 40 + (10.65) * (5 + 3) = 125^{\circ}C$$

The junction temperature is within the maximum rating.

Junction-to-case thermal resistance is specified from the IC junction to the bottom of the case directly below the die. This is the lowest resistance path for heat flow. Proper mounting ensures the best thermal flow from this area of the package to the heat sink. Use of a thermally conductive material at the case-to-heat sink interface is recommended. Use a thermally conductive spacer if the case of the device must be electrically isolated and include its contribution to the total thermal resistance.

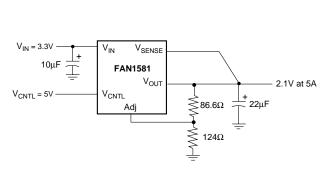

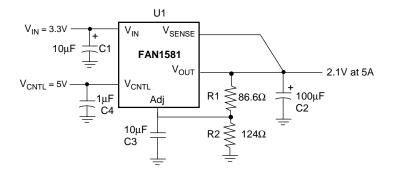

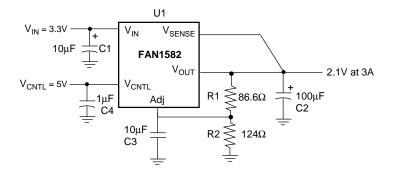

Figure 3. Application Circuit (FAN1581)

| Table 1. Bill of Materials for Application Cir | rcuit for the FAN1581 |

|------------------------------------------------|-----------------------|

|------------------------------------------------|-----------------------|

| Item   | Quantity | Manufacturer | Part Number | Description         |

|--------|----------|--------------|-------------|---------------------|

| C1, C3 | 2        | Xicon        | L10V10      | 10µF, 10V Aluminum  |

| C2     | 1        | Xicon        | L10V100     | 100µF, 10V Aluminum |

| C4     | 1        | Any          |             | 1µF Ceramic         |

| R1     | 1        | Generic      |             | 86.6Ω, 1%           |

| R2     | 1        | Generic      |             | 124Ω, 1%            |

| U1     | 1        | Fairchild    | FAN1581T    | 5A Regulator        |

FAN1581

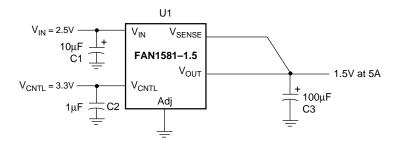

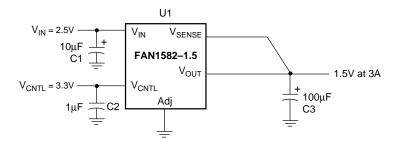

Figure 4. Application Circuit (FAN1581-1.5)

Table 2. Bill of Materials for Application Circuit for the RC1581-1.5

| ltem | Quantity | Manufacturer | Part Number  | Description         |

|------|----------|--------------|--------------|---------------------|

| C1   | 1        | Xicon        | L10V10       | 10µF, 10V Aluminum  |

| C2   | 1        | Any          |              | 1µF Ceramic         |

| C3   | 1        | Xicon        | L10V100      | 100µF, 10V Aluminum |

| U1   | 1        | Fairchild    | FAN1581T-1.5 | 5A Regulator        |

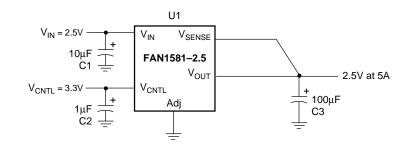

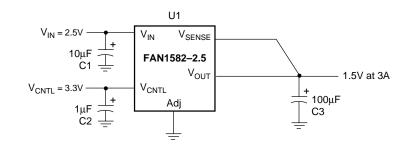

Figure 5. Application Circuit (FAN1581-2.5)

Table 3. Bill of Materials for Application Circuit for the RC1581-2.5

| ltem | Quantity | Manufacturer | Part Number  | Description         |

|------|----------|--------------|--------------|---------------------|

| C1   | 1        | Xicon        | L10V10       | 10µF, 10V Aluminum  |

| C2   | 1        | Any          |              | 1µF Ceramic         |

| C3   | 1        | Xicon        | L10V100      | 100µF, 10V Aluminum |

| U1   | 1        | Fairchild    | FAN1581T-2.5 | 5A Regulator        |

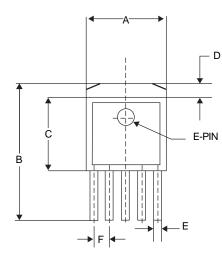

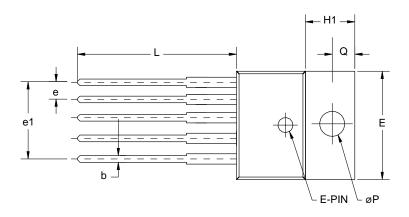

# **Mechanical Dimensions**

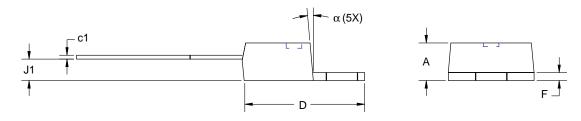

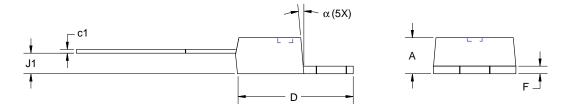

### 5-Lead TO-263 Package

| Symbol | Inches |       | Millim | neters |

|--------|--------|-------|--------|--------|

|        | Min.   | Max.  | Min.   | Max.   |

| А      | .380   | .405  | 9.65   | 10.29  |

| В      | .575   | .625  | 14.60  | 15.88  |

| С      | .325   | .380  | 8.25   | 9.66   |

| D      | -      | .055  | -      | 1.40   |

| E      | .020   | .039  | .50    | .99    |

| F      | .060   | .072  | 1.52   | 1.83   |

| G      | 0.45   | .055  | 1.14   | 1.40   |

| Н      | .160   | .190  | 4.06   | 4.83   |

| J      | .090   | 0.110 | 2.28   | 2.80   |

| К      | .018   | .029  | .457   | .736   |

| R      | .017   | .019  | 0.43   | 0.48   |

#### Notes:

- 1. Dimensions are exclusive of mold flash and metal burrs.

- 2. Standoff-height is measured from lead tip with ref. to Datum -B-. 3. Foot length is measured with ref. to Datum -A- with lead surface

- (at inner R).Dimension exclusive of dambar protrusion or intrusion.

- 5. Formed leads to be planar with respect to one another at seating place –C-.

# **Mechanical Demensions (continued)**

### 5-Lead TO-220 Package

| Symbol | Inches |            |       |       | Notes |

|--------|--------|------------|-------|-------|-------|

| Symbol | Min.   | Max.       | Min.  | Max.  | notes |

| А      | .140   | .190       | 3.56  | 4.83  |       |

| b      | .025   | .040       | .63   | 1.02  |       |

| c1     | .140   | .220       | .356  | .559  |       |

| øP     | .139   | .161       | 3.53  | 4.09  |       |

| D      | .560   | .650       | 14.22 | 16.51 |       |

| E      | .380   | .420       | 9.65  | 10.67 |       |

| е      | .062   | .072       | 1.57  | 1.83  |       |

| e1     | .263   | .273       | 6.68  | 6.94  |       |

| F      | .045   | .055       | 1.14  | 1.40  |       |

| H1     | .230   | .270       | 5.84  | 6.87  |       |

| J1     | .080   | .115       | 2.04  | 2.92  |       |

| L      | .500   | .580       | 12.70 | 14.73 |       |

| Q      | .100   | .135       | .254  | .343  |       |

| α      | 3°     | <b>7</b> ° | 3°    | 7°    |       |

Notes:

1. Dimension c1 apply for lead finish.

### **Ordering Information**

| Product Number | Package |

|----------------|---------|

| FAN1581M       | TO-263  |

| FAN1581T       | TO-220  |

| FAN1581M-1.5   | TO-263  |

| FAN1581T-1.5   | TO-220  |

| FAN1581M-2.5   | TO-263  |

| FAN1581T-2.5   | TO-220  |

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

#### TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

ACEx<sup>TM</sup> CoolFET<sup>TM</sup> CROSSVOLT<sup>TM</sup> E<sup>2</sup>CMOS<sup>TM</sup> FACT<sup>TM</sup> FACT Quiet Series<sup>TM</sup> FAST<sup>®</sup> FAST<sup>®</sup> FASTr<sup>TM</sup> GTO<sup>TM</sup> HiSeC<sup>TM</sup> ISOPLANAR™ MICROWIRE™ POP™ PowerTrench® QFET™ QS™ Quiet Series™ SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SyncFET™ TinyLogic™ UHC™ VCX™

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user. 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **PRODUCT STATUS DEFINITIONS**

**Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                                        |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or<br>In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                |

| Preliminary              | First Production          | This datasheet contains preliminary data, and<br>supplementary data will be published at a later date.<br>Fairchild Semiconductor reserves the right to make<br>changes at any time without notice in order to improve<br>design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild<br>Semiconductor reserves the right to make changes at<br>any time without notice in order to improve design.                                                             |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product<br>that has been discontinued by Fairchild semiconductor.<br>The datasheet is printed for reference information only.                                                         |

# FAN1582 **3A Adjustable/Fixed Ultra Low Dropout Linear Regulator**

### Features

- Ultra Low dropout voltage, 0.4V typical at 3A

- Remote sense operation

-AIRCHILD

SEMICONDUCTOR IM

- · Fast transient response

- Load regulation: 0.05% typical

- 0.5% initial accuracy

- On-chip thermal limiting

- · 5 Pin standard TO-220 and TO-263 packages

# Applications

- Pentium<sup>®</sup> Processors

PowerPC<sup>™</sup>, AMD K5 and K6 processors

- Pentium support of GTL+ bus supply

- Low voltage logic supply

- Embedded Processor supplies

- Split plane regulator

- New 2.5V and 1.8V Logic Families

#### Description

The FAN1582, FAN1582-1.5, and FAN1582-2.5 are ultra-low dropout regulators with 3A output current capability. These devices have been optimized for low voltage applications including VTT bus termination, where transient response and minimum input voltage are critical. The FAN1582 is ideal for low voltage microprocessor applications requiring a regulated output from 1.3V to 5.7V with a power input supply of 1.75V to 6.5V. The FAN1582-1.5 offers fixed 1.5V with 3A current capabilities for GTL+ bus VTT termination. The FAN1582-2.5 offers fixed 2.5V with 3A current capability for logic IC operation and processors while minimizing the overall power dissipation.

Current limit ensures controlled short-circuit current. On-chip thermal limiting provides protection against any combination of overload and ambient temperature that would create excessive junction temperatures.

The FAN1582 series regulators are available in the industrystandard 5-Pin TO-220 and TO-263 power packages.

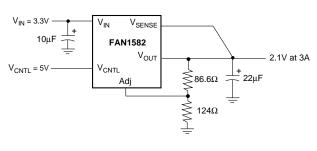

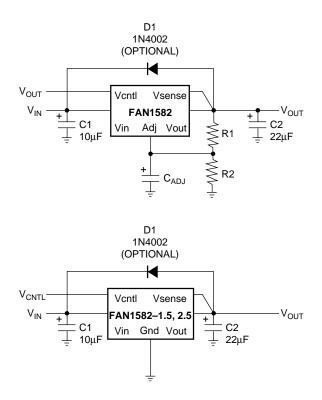

# **Typical Applications**

PRELIMINARY SPECIFICATION describes products that are not in full production at time of printing. Specifications are based on design goals and limited characterization. In the process of final production release, specifications may change. Contact Fairchild Semiconductor for current information.

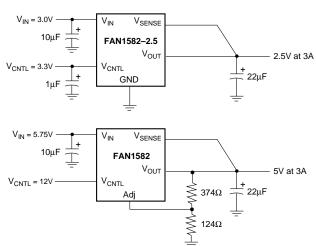

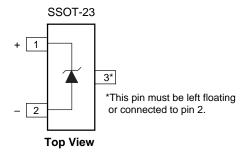

# **Pin Assignments**

\*With package soldered to 0.5 square inch copper area over backside ground plane or internal power plane. Θ<sub>JA</sub> can vary fom 20°C/W to >40°C/W with other mounting techniques.

# **Pin Definitions**

| Pin Number | Pin Name | Pin Function Descrition                                                                                                                                                  |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VSense   | <b>Remote Voltage Sense</b> . Connect this pin to the load to permit true remote sensing and avoid trace drops.                                                          |

| 2          | ADJ/GND  | Adjust or Ground. On the FAN1582, this pin forms the feedback to determine the output voltage. On the FAN1582-1.5 and -2.5, connect this pin to ground.                  |

| 3          | VOUT     | Output Voltage. This pin and the tab are output.                                                                                                                         |

| 4          | VCNTL    | <b>Control Voltage.</b> This pin draws small-signal power to control the FAN1582 circuitry. Connect to a voltage higher than VIN, as shown in the applications circuits. |

| 5          | VIN      | Input Voltage.                                                                                                                                                           |

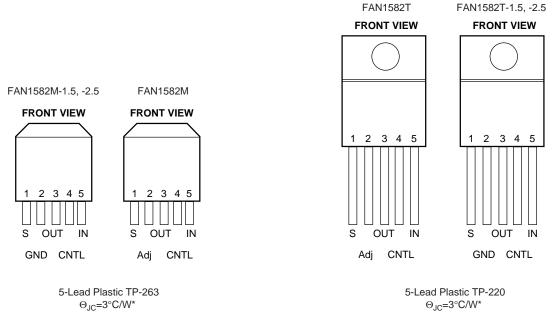

### **Internal Block Diagram**

# **Absolute Maximum Ratings**

| Parameter                             | Min. | Max. | Unit |  |

|---------------------------------------|------|------|------|--|

| VIN                                   |      | 7    | V    |  |

| VCNTL                                 |      | 13.2 | V    |  |

| Operating Junction Temperature Range  | 0    | 125  | °C   |  |

| Lead Temperature (Soldering, 10 sec.) |      | 300  | °C   |  |

| Storage Temperature Range             | -65  | 150  | °C   |  |

# **Electrical Characteristics**

$TJ=25^{\circ}C$ , VOUT = VS, VADJ = 0V unless otherwise specified.

The  ${\mbox{\circ}}$  denotes specifications which apply over the specified operating temperature range.

| Parameter                            | Conditions                                                                                                               |   | Min.  | Тур.  | Max.  | Units |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---|-------|-------|-------|-------|

| Reference Voltage <sup>3</sup>       | VIN = 2.0V, VCNTL = 2.75V,<br>IOUT = 10mA                                                                                |   | 1.243 | 1.250 | 1.257 | V     |

| Reference Voltage <sup>3</sup>       | $\begin{array}{l} 2.05V \leq V_{IN} \leq 5.5V, \\ 2.7V \leq V_{CNTL} \leq 12V, \\ 10mA \leq I_{OUT} \leq 3A \end{array}$ | • | 1.237 | 1.250 | 1.263 | V     |

| Adjustable Output Voltage            | $3V \le V_{IN} \le 7V$ (function of Vout),<br>10mA \le IOUT \le 3A                                                       | • | Vref  | 1.5   | 5.7   | V     |

| Output Voltage <sup>4</sup>          | $3V \le V_{IN} \le 7V$ , $10mA \le I_{OUT} \le 3A$                                                                       | • | 1.47  | 1.5   | 1.53  | V     |

| Output Voltage <sup>5</sup>          | $5.1V \le V_{IN} \le 7V$ , $10mA \le I_{OUT} \le 3A$                                                                     | • | 2.474 | 2.5   | 2.526 | V     |

| Line Regulation <sup>1,2</sup>       | $1.75V \le V_{IN} \le 5.5V, 2.5V \le V_{CNTL} \le 12V,$<br>IOUT = 10mA                                                   | • |       | 1     | 3     | mV    |

| Load Regulation <sup>1,2</sup>       | $V_{IN} = 2.1V, V_{CNTL} = 2.75V,$<br>$10mA \le I_{OUT} \le 3A$                                                          | • |       | 1     | 5     | mV    |

| Dropout Voltage Minimum VCNTL        | VIN = 2.05V, ΔVREF = 1%, IOUT = 3A                                                                                       | • |       | 1.05  | 1.18  | V     |

| Dropout Voltage Minimum VIN          | VCNTL = 2.75V, ΔVREF = 1%,<br>IOUT = 3A                                                                                  |   |       | 0.4   | 0.5   | V     |

| Dropout Voltage Minimum VIN          | VCNTL = 2.75V, ΔVREF = 1%,<br>IOUT = 3A                                                                                  | • |       | 0.5   | 0.6   | V     |

| Current Limit                        | VIN = 2.05V, VCNTL = 2.75V                                                                                               | • | 3.1   |       |       | Α     |

| Control Pin Current                  | V <sub>IN</sub> = 2.05V, V <sub>CNTL</sub> = 2.75V,<br>IOUT = 10mA                                                       | • |       | 30    | 120   | μA    |

| Adjust Pin Current <sup>3</sup>      | VIN = 2.05V, VCNTL = 2.75V                                                                                               | • |       | 50    | 120   | mA    |

| Minimum Load Current                 | VIN = 3.3V, VCNTL = 5V                                                                                                   | • |       | 5.0   | 10    | mA    |

| Ripple Rejection                     | $V_{IN} = 3.75V$ , $V_{CNTL} = 3.75V$ , $f = 120Hz$ ,<br>$C_{OUT} = 22\mu F$ Tantalum, $I_{OUT} = 1.5A$                  |   | 60    | 80    |       | dB    |

| Thermal Resistance, Junction to Case |                                                                                                                          |   |       | 3     |       | °C/W  |

| Thermal Regulation                   | TA = 25°C, 30ms pulse                                                                                                    |   |       | 0.002 | 0.02  | %/W   |

| Thermal Shutdown                     |                                                                                                                          |   |       | 150   |       | °C    |

#### Notes:

3. FAN1582 only.

4. FAN1582-1.5 only.

5. FAN1582-2.5 only.

<sup>1.</sup> See thermal regulation specifications for changes in output voltage due to heating effects. Load and line regulation are measured at a constant junction temperature by low duty cycle pulse testing.

<sup>2.</sup> Line and load regulation are guaranteed up to the maximum power dissipation (18W). Power dissipation is determined by input/output differential and the output current. Guaranteed maximum output power will not be available over the full input/ output voltage range.

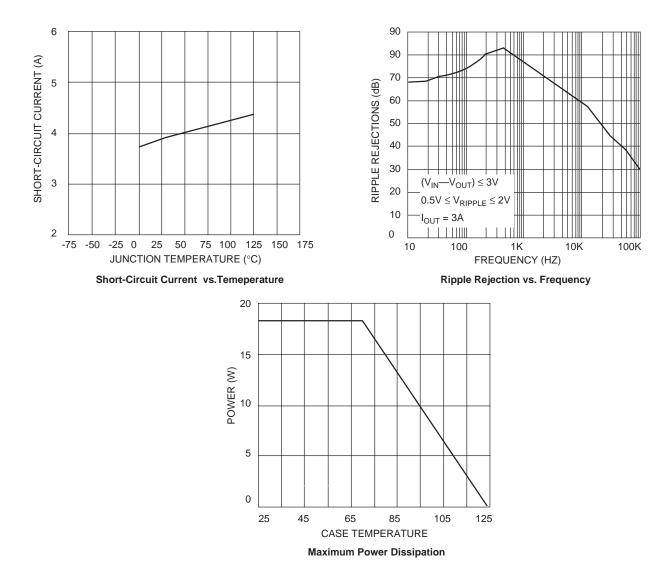

### **Typical Perfomance Characteristics**

#### General

The FAN1582, FAN1582-1.5, and FAN1582-2.5 are threeterminal regulators optimized for GTL+ VTT termination and logic applications. These devices are short-circuit protected, and offer thermal shutdown to turn off the regulator when the junction temperature exceeds about 150°C. The FAN1582 series provides low dropout voltage and fast transient response. Frequency compensation uses capacitors with low ESR while still maintaining stability. This is critical in addressing the needs of low voltage high speed microprocessor buses like GTL+.

#### Stability

The FAN1582 series requires an output capacitor as a part of the frequency compensation. It is recommended to use a  $22\mu F$  solid tantalum or a  $100\mu F$  aluminum electrolytic on the output

to ensure stability. The frequency compensation of these devices optimizes the frequency response with low ESR capacitors. In general, it is suggested to use capacitors with an ESR of <1 $\Omega$ . It is also recommended to use bypass capacitors such as a 22µF tantalum or a 100µF aluminum on the adjust pin of the FAN1582 for low ripple and fast transient response. When these bypassing capacitors are not used at the adjust pin, smaller values of output capacitors provide equally good results.

#### **Protection Diodes**

In normal operation, the FAN1582 series does not require any protection diodes. For the FAN1582, internal resistors limit internal current paths on the adjust pin. Therefore, even with bypass capacitors on the adjust pin, no protection diode is needed to ensure device safety under short-circuit conditions.

A protection diode between the input and output pins is usually not needed. An internal diode between the input and the output pins on the FAN1582 series can handle microsecond surge currents of 50A to 100A. Even with large value output capacitors it is difficult to obtain those values of surge currents in normal operation. Only with large values of output capacitance, such as  $1000\mu$ F to  $5000\mu$ F, and with the input pin instantaneously shorted to ground can damage occur. A crowbar circuit at the input can generate those levels of current; a diode from output to input is then recommended, as shown in Figure 1. Usually, normal power supply cycling or system "hot plugging and unplugging" will not generate current large enough to do any damage.

The adjust pin can be driven on a transient basis  $\pm 7V$  with respect to the output, without any device degradation. As with any IC regulator, exceeding the maximum input-to-output voltage differential causes the internal transistors to break down and none of the protection circuitry is then functional.

Figure 1. Optional Protection Diode

#### **Ripple Rejection**

In applications that require improved ripple rejection, a bypass capacitor from the adjust pin of the FAN1582 to ground reduces the output ripple by the ratio of VOUT/1.25V. The impedance of the adjust pin capacitor at the ripple frequency should be less than the value of R1 (typically in the range of  $100\Omega$  to  $120\Omega$ ) in the feedback divider network in Figure 1. Therefore, the value of the required adjust pin capacitor is a function of the input ripple frequency. For example, if R1 equals

$100\Omega$  and the ripple frequency equals 120Hz, the adjust pin capacitor should be 22µF. At 10kHz, only 0.22µF is needed.

#### **Output Voltage**

The FAN1582 regulator develops a 1.25V reference voltage between the output pin and the adjust pin (see Figure 2). Placing a resistor R1 between these two terminals causes a constant current to flow through R1 and down through R2 to set the overall output voltage. Normally, this current is the specified minimum load current of 10mA.

The current out of the adjust pin adds to the current from R1 and is typically  $35\mu$ A. Its output voltage contribution is small and only needs consideration when a very precise output voltage setting is required.

Figure 2. Basic Regulator Circuit

#### Load Regulation

The FAN1582 family provides true remote sensing, eliminating output voltage errors due to trace resistance. To utilize remote sensing, connect the VSENSE pin directly to the load, rather than at the VOUT pin. If the load is more than 1" away from the FAN1582, it may be necessary to increase the load capacitance to ensure stability.

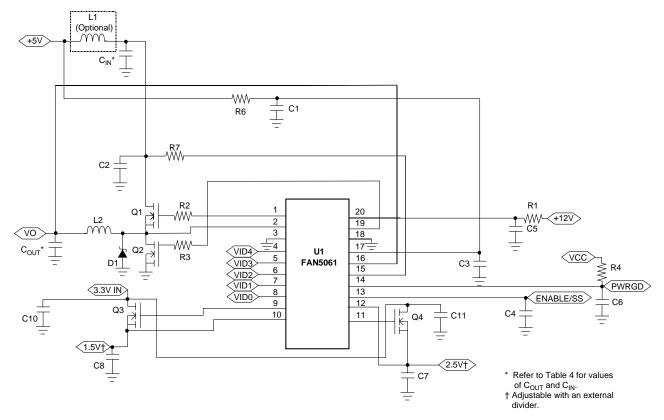

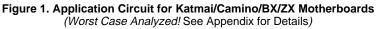

#### **Thermal Considerations**