# Am25LS2520

Octal D-Type Flip-Flop with Clear, Clock Enable and Three-State Control

### **DISTINCTIVE CHARACTERISTICS**

- Buffered common clock enable input

- Buffered common asynchronous clear input

- Three-state outputs

- 8-bit, high-speed parallel register with positive edgetriggered, D-type flip-flops

- Am25LS Family offers improved sink current, source current and noise margin

#### GENERAL DESCRIPTION

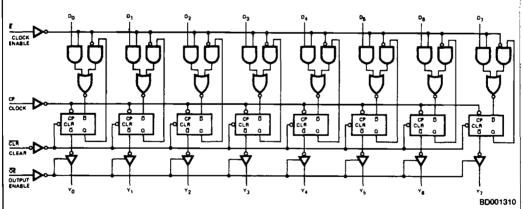

The Am25LS2520 is an 8-bit register built using advanced Low-Power Schottky technology. The register consists of eight D-type flip-flops with a buffered common clock, a buffered common clock enable, a buffered asynchronous clear input, and three-state outputs.

When the clear input is LOW, the internal flip-flops of the register are reset to logic 0 (LOW), independent of all other inputs. When the clear input is HIGH, the register operates in the normal fashion.

When the three-state output enable  $(\overline{OE})$  input is LOW, the Y outputs are enabled and appear as normal TTL outputs.

When the output enable (OE) input is HIGH, the Y outputs are in the high impedance (three-state) condition. This does not affect the internal state of the flip-flop Q output.

The clock enable input (Ē) is used to selectively load data into the register. When the Ē input is HIGH, the register will retain its current data. When the Ē is LOW, new data is entered into the register on the LOW-to-HIGH transition of the clock input.

This device is packaged in a space-saving (0.4-inch row spacing) 22-pin package and in a 24-pin flatpack,

### **BLOCK DIAGRAM**

### **RELATED PRODUCTS**

| Part No. | Description            |

|----------|------------------------|

| Am25S18  | Quad D Register        |

| Am2920   | Octal D-Type Flip-flop |

| Am2954/5 | Octal D Registers      |

03698B

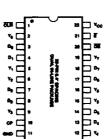

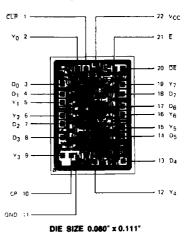

# CONNECTION DIAGRAM Top View

L-28-1

Note: Pin 1 is marked for orientation \*Reserved - do not use.

CD001900

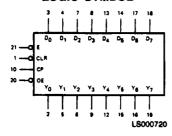

### LOGIC SYMBOL

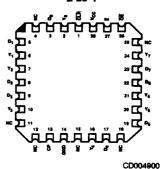

### METALLIZATION AND PAD LAYOUT

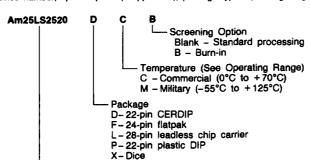

### ORDERING INFORMATION

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

Device type

Octal D-type Flip-Flop

| Valid Con  | nbinations                             |

|------------|----------------------------------------|

| Am25LS2520 | PC<br>DC, DM<br>FM<br>LC, LM<br>XC, XM |

### **Valid Combinations**

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

# 9

### PIN DESCRIPTION

| Pin No. | Name | 1/0 | Description                                                                                                                                                                                                                                                                                     |

|---------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Di   | 1   | The D flip-flop data inputs.                                                                                                                                                                                                                                                                    |

| 1       | CLR  | 1   | When the clear input is LOW, the Q <sub>i</sub> outputs are LOW, regardless of the other inputs. When the clear input is HIGH, data can be entered into the register.                                                                                                                           |

| 11      | CP   | 1   | Clock Pulse for the Register; enters data into the register on the LOW-to-HIGH transition.                                                                                                                                                                                                      |

|         | Yi   | 0   | The register three-state outputs.                                                                                                                                                                                                                                                               |

| 21      | Ē    | 1   | Clock Enable. When the clock enable is LOW, data on the D <sub>i</sub> input is transferred to the Q <sub>i</sub> output on the LOW-to-HIGH clock transition. When the clock enable is HIGH, the Q <sub>i</sub> outputs do not change state, regardless of the data or clock input transitions. |

| 20      | ŌĒ   | 1   | Output Control. When the $\overline{OE}$ input is HIGH, the Y <sub>i</sub> outputs are in the high impedance state. When the $\overline{OE}$ input is LOW, the TRUE register data is present at the Y <sub>i</sub> outputs.                                                                     |

### **FUNCTION TABLE**

|          |         | 1    | nput   |      | Internal | Outputs  |                  |

|----------|---------|------|--------|------|----------|----------|------------------|

| Function | OE CLR  |      | E      | DI   | СР       | Qi       | Yį               |

| Hi-Z     | н       | Х    | Х      | Х    | х        | X        | Z                |

| Clear    | H       | ГГ   | X      | X    | X        | L        | Z<br>L           |

| Hold     | H       | ΗH   | H<br>H | X    | X        | NC<br>NC | Z<br>NC          |

| Load     | # # L L | TITI |        | LHLH | † † †    | LHLH     | Z<br>Z<br>L<br>H |

t = LOW-to-HIGH Transition X = Don't Care Z = High-Impedance

H = HIGH L = LOW NC = No change

### **APPLICATIONS** 16 BIT DATA BUS Am25LS2520 INSTRUCTION REGISTER Am25LS2520 - OTHER 18 18 Am27LS11 Am27LS11 Am27LS1 1 MICROPROCESSOR SEQUENCER 12 PROM ARRAY **∦**8 Χa Am25LS2520 Am25L\$2520 Am25LS2520 Am25LS2520 PIPELINE REGISTER Am25LS2520 Am25L52520 Am25LS2520 56 BIT PIPELINE REGISTER AF000670 A typical Computer Control Unit for a microprogrammed machine.

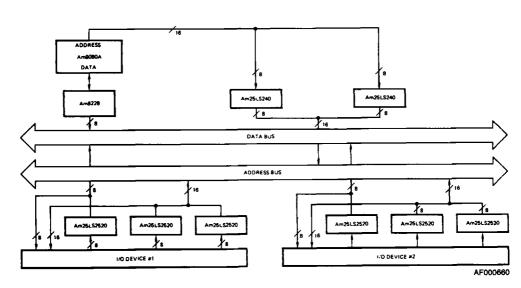

The Am25LS2520 is a useful device in interfacing with the Am9080A system buses.

### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                           |

|-----------------------------------------------|

| Continuous0.5V to +7.0V                       |

| DC Voltage Applied to Outputs For             |

| High Output State0.5V to +V <sub>CC</sub> max |

| DC input Voltage0.5V to +7.0V                 |

| DC Output Current, Into Outputs               |

| DC Input Current30mA to +5.0mA                |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

### **OPERATING RANGES**

| Commercial (C) Devices            |                              |

|-----------------------------------|------------------------------|

| Temperature                       | 0°C to +70°C                 |

| Supply Voltage                    | + 4.75V to + 5.25V           |

| Military (M) Devices              |                              |

| Temperature                       | 55°C to +125°C               |

| Supply Voltage                    | +4.5V to +5.5V               |

| Operating ranges define those lim | its over which the function- |

| ality of the device in averanteed |                              |

### DC CHARACTERISTICS over operating range unless otherwise specified

| Parameters      | Description                              | Test Conditions (Note 2)                             |                                             |          | Min  | Typ<br>(Note 1) | Max   | Units |

|-----------------|------------------------------------------|------------------------------------------------------|---------------------------------------------|----------|------|-----------------|-------|-------|

|                 |                                          | V <sub>CC</sub> = MIN MIL, I <sub>OH</sub> = -1.0mA  |                                             | = -1.0mA | 2.4  | 3.4             |       |       |

| VOH             | Output HIGH Voltage                      | VIN = VIH or VIL                                     |                                             |          | 2.4  | 3.4             |       | Volts |

|                 |                                          | V <sub>CC</sub> = MIN                                | loL = 4.0                                   | mA       |      |                 | 0.4   |       |

| VOL             | Output LOW Voltage                       | VIN - VIH OF VIL                                     |                                             |          |      |                 | 0.45  | Volts |

| V <sub>IH</sub> | Input HIGH Level                         | Guaranteed input logical HIGH voltage for all inputs |                                             |          | 2.0  |                 |       | Volts |

|                 |                                          | Guaranteed input logical LOW                         |                                             | MIL      |      |                 | 0.7   |       |

| VIL             | VIL Input LOW Level                      | voltage for all inputs. COM'L                        |                                             |          |      |                 | 0.8   | Volts |

| V <sub>I</sub>  | Input Clamp Voltage                      | VCC = MIN, IIN = -                                   | 18mA                                        |          |      |                 | -1.5  | Volts |

| IfL             | Input LOW Current                        | V <sub>CC</sub> = MAX, V <sub>IN</sub> =             | 0.4V                                        |          |      | 1               | -0.36 | mA    |

| Чн              | Input HIGH Current                       | V <sub>CC</sub> = MAX, V <sub>IN</sub> =             | 2.7V                                        |          |      |                 | 20    | μА    |

| lj              | Input HIGH Current                       | V <sub>CC</sub> = MAX, V <sub>IN</sub> =             | 7.0V                                        |          |      |                 | 0.1   | mA    |

|                 | Off-State (High-Impedance)               |                                                      | Vo = 0.4\                                   | /        |      |                 | -20   |       |

| ю               | Output Current                           | V <sub>CC</sub> = MAX                                | V <sub>CC</sub> = MAX V <sub>O</sub> = 2.4V |          |      |                 | 20    | μA    |

| Isc             | Output Short Circuit Current<br>(Note 3) | V <sub>CC</sub> = MAX                                |                                             |          | - 15 |                 | -85   | mA    |

| loc             | Power Supply Current<br>(Note 4)         | V <sub>CC</sub> = MAX                                |                                             |          |      | 24              | 37    | mA    |

- Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

For conditions shown as MIN or MAX, use the appropriate value specified under Operating Ranges for the applicable device type.

Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

All outputs open. E = GND, Di Inputs = CLR = DE = 4.5V. Apply momentary ground, then 4.5V to clock input.

### SWITCHING CHARACTERISTICS (TA = +25°C, VCC = 5.0V)

| Parameters                | Description                         |                      | Test Conditions        | Min | Тур | Max   | Units |

|---------------------------|-------------------------------------|----------------------|------------------------|-----|-----|-------|-------|

| <b>t</b> PLH              |                                     |                      |                        |     | 18  | 27    |       |

| <b>¹</b> PHL              | Clock to Yi (O                      | E LOW)               | i F                    |     | 24  | 24 36 | ns ns |

| tphL                      | Clear to Y                          |                      |                        | 10  | 22  | 35    | ns    |

| te                        | Data (Di)                           |                      | 7                      |     | 3   |       | ns    |

| t <sub>h</sub>            | Data (Di)                           |                      | Ι Γ                    | 10  | 3   |       | ns    |

| t <sub>8</sub> Enable (Ē) |                                     | Active               | 1                      | 15  | 10  |       | ns    |

|                           | Enable (E)                          | Inactive             | C <sub>L</sub> = 15pF  | 20  | 12  |       |       |

| th                        | Enable (E)                          |                      | P <sub>L</sub> = 2.0kΩ | 0   | 0   |       | ns    |

| ts                        | Clear Recovery (In-Active) to Clock |                      |                        | 11  | 7   |       | ns    |

|                           |                                     | HIGH                 | 1                      | 20  | 14  |       |       |

| t <sub>w</sub>            | Clock                               | LOW                  | 1                      | 25  | 13  |       | ns    |

| 1 <sub>pw</sub>           | Clear                               |                      |                        | 20  | 13  |       | ns    |

| <sup>1</sup> ZH           |                                     |                      | Τ                      |     | 9   | 13    |       |

| tzL                       | OE to Yi                            |                      |                        |     | 14  | 21    | i ne  |

| tHZ                       | OE to Yi                            |                      | C <sub>L</sub> = 5.0pF |     | 20  | 30    |       |

| 1LZ                       |                                     |                      | R <sub>L</sub> = 2.0kΩ |     | 24  | 36    | 1 №   |

| fmax                      | Maximum Clock                       | k Frequency (Note 1) |                        |     | 40  |       | MHz   |

Note 1. Per industry convention, f<sub>max</sub> is the worst case value of the maximum device operating frequency with no constraints on t<sub>r</sub>, t<sub>t</sub>, pulse width or duty cycle.

### SWITCHING CHARACTERISTICS over operating range unless otherwise specified\*

| Parameters       |                                        |          |                        | COMMERCIAL |         | MILITARY Am25LS2520 |     | _     |

|------------------|----------------------------------------|----------|------------------------|------------|---------|---------------------|-----|-------|

|                  | Description                            |          |                        | Am25       | L\$2520 |                     |     | ]     |

|                  |                                        |          | Test Conditions        | Min        | Max     | Min                 | Max | Units |

| ФСН              | Clock to Yi (OE LOW)                   |          |                        |            | 33      |                     | 39  |       |

| <sup>†</sup> PHL |                                        |          | 1 E                    |            | 45      |                     | 54  | ns    |

| 1PHL             | Clear to Y                             |          | 7 [                    |            | 43      |                     | 51  | ns    |

| t <sub>s</sub>   | Data (D <sub>i</sub> )                 |          | 7 [                    | 12         |         | 15                  |     | ns    |

| ኒክ               | Data (D <sub>i</sub> )                 |          |                        | 12         |         | 15                  |     | ns    |

|                  | Enable (E)                             | Active   | 7 [                    | 17         |         | 20                  |     | ne    |

| t <sub>s</sub>   |                                        | Inactive | C <sub>L</sub> = 50pF  | 20         |         | 23                  |     |       |

| t <sub>h</sub>   | Enable (E)                             |          | R <sub>L</sub> = 2.0kΩ | 0          |         | 0                   |     | ns    |

| l <sub>a</sub>   | Clear Recovery (In-Active) to<br>Clock |          |                        | 13         |         | 15                  |     | ns    |

|                  |                                        | HIGH     | 7 [                    | 25         |         | 30                  |     |       |

| tpw              | Clock                                  | LOW      | 7                      | 30         |         | 35                  |     | ns    |

| t <sub>pw</sub>  | Clear                                  |          |                        | 22         |         | 25                  |     | ns    |

| †ZH              | Ĭ <b>_</b>                             |          | 7 [                    |            | 19      |                     | 25  |       |

| <sup>t</sup> ZL  | TE to Yi                               |          |                        | -          | 30      |                     | 39  | ns    |

| <sup>t</sup> HZ  | T                                      |          | C <sub>L</sub> = 5.0pF |            | 35      |                     | 40  | ا     |

| tLZ              | OE to Yi                               |          | AL = 2.0kΩ             |            | 39      |                     | 42  | ne    |

| fmex             | Maximum Clock Frequency<br>(Note 1)    |          |                        | 25         |         | 20                  |     | MHz   |

<sup>\*</sup>AC performance over the operating temperature range is guaranteed by testing defined in Group A, Subgroup 9.

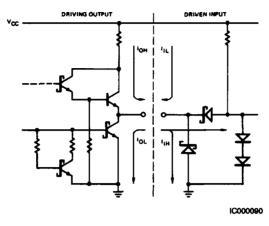

# Am25LS2520 LOW-POWER SCHOTTKY INPUT/OUTPUT CURRENT INTERFACE CONDITIONS

Note: Actual current flow direction shown.

q