# MC9RS08KA2 MC9RS08KA1

Data Sheet

RS08 Microcontrollers

MC9RS08KA2 Rev. 2 12/2006

freescale.com

# MC9RS08KA2 Features

#### 8-Bit RS08 Central Processor Unit (CPU)

- Simplified S08 instruction set with added high-performance instructions

- LDA, STA, and CLR instructions support the short addressing mode; address \$0000 to \$001F can be accessed via a single-byte instruction

- ADD, SUB, INC, and DEC instructions support the tiny addressing mode; address \$0000 to \$000F can be accessed via a single-byte instruction with reduced instruction cycle

- Shadow PC register instructions: SHA and SLA

- Pending interrupt indication

- Index addressing via D[X] and X register

- Direct page access to the entire memory map through paging window

#### Memory

- On-chip Flash EEPROM

- MC9RS08KA2: 2048 bytes

- MC9RS08KA1: 1024 bytes

- 63 bytes on-chip RAM

#### **Power-Saving Modes**

- Wait and stop

- Wakeup from power-saving modes using real-time interrupt (RTI), KBI, or ACMP

#### **Clock Source**

- ICS Trimmable 20-MHz internal clock source

- Up to 10-MHz internal bus operation

- 0.2% trimmable resolution, 2% deviation over temperature and voltage range

#### **System Protection**

- Computer operating properly (COP) reset running off bus-independent clock source

- Low-voltage detection with reset or stop wakeup

#### Peripherals

- MTIM 8-bit modulo timer

- ACMP Analog comparator

- Full rail-to-rail supply operation

- Option to compare to fixed internal bandgap reference voltage

- Can operate in stop mode

- **KBI** Keyboard interrupt ports

- Three KBI ports in 6-pin package

- Five KBI ports in 8-pin package

#### **Development Support**

- Background debug system

- Breakpoint capability to allow single breakpoint setting during in-circuit debug

#### **Package Options**

- 6-pin dual flat no lead (DFN) package

- Two general-purpose input/output (I/O) pins

- One general-purpose input pin

- One general-purpose output pin

- 8-pin plastic dual in-line pin (PDIP) package

- Four general-purpose input/output (I/O) pins

- One general-purpose input pin

- One general-purpose output pin

- 8-pin narrow body SOIC package

- Four general-purpose input/output (I/O) pins

- One general-purpose input pin

- One general-purpose output pin

# **MC9RS08KA2 Series Data Sheet**

Covers: MC9RS08KA2 MC9RS08KA1

> MC9RS08KA2 Rev. 2 12/2006

# **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

#### http://freescale.com

The following revision history table summarizes changes contained in this document.

| Revision<br>Number | Revision<br>Date | Description of Changes         |

|--------------------|------------------|--------------------------------|

| 1.0                | 04/2006          | Initial public release version |

| 2                  | 12/2006          | Added MC9RS08KA1               |

This product incorporates SuperFlash<sup>®</sup> technology licensed from SST.

Freescale, and the Freescale logo are trademarks of Freescale Semiconductor, Inc. © Freescale Semiconductor, Inc., 2006. All rights reserved.

# **List of Chapters**

| Chapter 1  | MC9RS08KA2 Series Device Overview              | 15  |

|------------|------------------------------------------------|-----|

| Chapter 2  | Pins and Connections                           | 17  |

| Chapter 3  | Modes of Operation                             | 21  |

| Chapter 4  | Memory                                         | 25  |

| Chapter 5  | Resets, Interrupts, and General System Control | 35  |

| Chapter 6  | Parallel Input/Output Control                  | 45  |

| Chapter 7  | Keyboard Interrupt (RS08KBIV1)                 | 51  |

| Chapter 8  | Central Processor Unit (RS08CPUV1)             | 57  |

| Chapter 9  | Internal Clock Source (RS08ICSV1)              | 73  |

| Chapter 10 | Analog Comparator (RS08ACMPV1)                 | 81  |

| Chapter 11 | Modulo Timer (RS08MTIMV1)                      | 87  |

| Chapter 12 | Development Support                            | 95  |

| Appendix A | Electrical Characteristics                     | 107 |

| Appendix B | Ordering Information and Mechanical Drawings   | 121 |

# **Table of Contents**

**Section Number**

Title

Page

### Chapter 1 MC9RS08KA2 Series Device Overview

| 1.1 | Overview15                | ĵ. |

|-----|---------------------------|----|

| 1.2 | MCU Block Diagram         | ý  |

| 1.3 | System Clock Distribution | )  |

### Chapter 2 Pins and Connections

| 2.1 | Introduc | tion                                     | 17 |

|-----|----------|------------------------------------------|----|

|     |          | Pin Assignment                           |    |

|     |          | nended System Connections                |    |

|     |          | uil                                      |    |

|     | 2.4.1    | Power                                    | 19 |

|     | 2.4.2    | PTA2/KBIP2/TCLK/RESET/V <sub>PP</sub>    | 19 |

|     |          | PTA3/ACMPO/BKGD/MS                       |    |

|     |          | General-Purpose I/O and Peripheral Ports |    |

### Chapter 3 Modes of Operation

| 3.1 | Introduc        | tion                            | 21 |

|-----|-----------------|---------------------------------|----|

| 3.2 | Features        |                                 | 21 |

| 3.3 | Run Mo          | de                              | 21 |

| 3.4 | Active <b>B</b> | Background Mode                 | 21 |

|     |                 | ode                             |    |

| 3.6 | Stop Mc         | ode                             | 23 |

|     | 1               | Active BDM Enabled in Stop Mode |    |

|     |                 | LVD Enabled in Stop Mode        |    |

|     |                 | 1                               |    |

### Chapter 4 Memory

| 4.1 | Memory                      | Мар                                      | 25 |

|-----|-----------------------------|------------------------------------------|----|

|     |                             | emented Memory                           |    |

|     | Indexed/Indirect Addressing |                                          |    |

| 4.4 | RAM an                      | d Register Addresses and Bit Assignments | 27 |

|     |                             |                                          |    |

| 4.6 | Flash                       |                                          | 29 |

|     | 4.6.1                       | Features                                 | 29 |

|     | 4.6.2                       | Flash Programming Procedure              | 30 |

|     |                             | Flash Mass Erase Operation               |    |

|     | 4.6.4                       | Security                                 |    |

|     |                             |                                          |    |

#### MC9RS08KA2 Series Data Sheet, Rev. 2

| 4.7 | Flash Re | gisters and Control Bits                | 32 |

|-----|----------|-----------------------------------------|----|

|     |          | Flash Options Register (FOPT and NVOPT) |    |

|     | 4.7.2    | Flash Control Register (FLCR)           | 33 |

| 4.8 | Page Sel | ect Register (PAGESEL)                  | 33 |

### Chapter 5 Resets, Interrupts, and General System Control

| 5.1 | Introduc | tion                                                            |    |

|-----|----------|-----------------------------------------------------------------|----|

| 5.2 |          |                                                                 |    |

| 5.3 |          | eset                                                            |    |

| 5.4 |          | er Operating Properly (COP) Watchdog                            |    |

| 5.5 | -        | ts                                                              |    |

| 5.6 | -        | tage Detect (LVD) System                                        |    |

|     |          | Power-On Reset Operation                                        |    |

|     | 5.6.2    | -                                                               |    |

|     | 5.6.3    | LVD Interrupt Operation                                         |    |

| 5.7 | Real-Tin | ne Interrupt (RTI)                                              |    |

| 5.8 |          | terrupt, and System Control Registers and Control Bits          |    |

|     | 5.8.1    | System Reset Status Register (SRS)                              |    |

|     | 5.8.2    | System Options Register (SOPT)                                  |    |

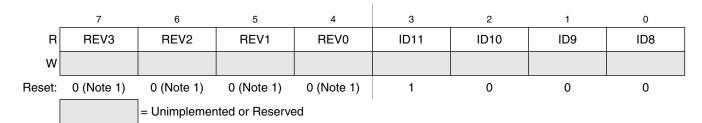

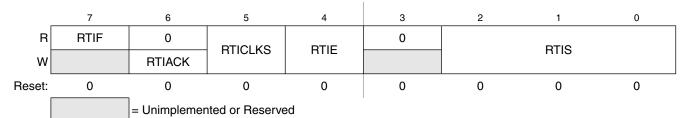

|     | 5.8.3    | System Device Identification Register (SDIDH, SDIDL)            |    |

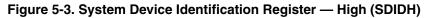

|     | 5.8.4    | System Real-Time Interrupt Status and Control Register (SRTISC) | 41 |

|     | 5.8.5    | System Power Management Status and Control 1 Register (SPMSC1)  |    |

|     | 5.8.6    | System Interrupt Pending Register (SIP1)                        |    |

|     |          |                                                                 |    |

### Chapter 6 Parallel Input/Output Control

| 6.1 | Pin Beha | vior in Lo | w-Power Modes                   | 46 |

|-----|----------|------------|---------------------------------|----|

|     |          |            | ers                             |    |

|     |          | -          | Registers                       |    |

| 6.3 |          |            | ers                             |    |

|     |          | -          | in Control Registers            |    |

|     |          |            | Internal Pulling Device Enable  |    |

|     |          |            | Pullup/Pulldown Control         |    |

|     |          |            | Output Slew Rate Control Enable |    |

|     |          |            |                                 |    |

### Chapter 7 Keyboard Interrupt (RS08KBIV1)

| 7.1 | Introduc | tion                                        |  |

|-----|----------|---------------------------------------------|--|

|     |          | Features                                    |  |

|     |          | Modes of Operation                          |  |

|     |          | 7.1.2.1 Operation in Wait Mode              |  |

|     |          | 7.1.2.2 Operation in Stop Mode              |  |

|     |          | 7.1.2.3 Operation in Active Background Mode |  |

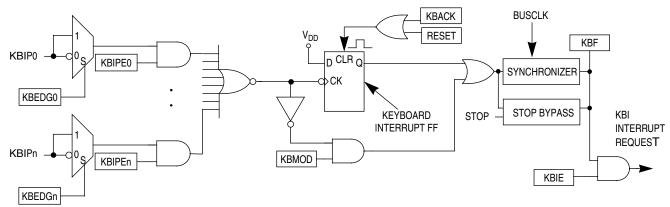

|     | 7.1.3    | Block Diagram                               |  |

|     |          |                                             |  |

#### MC9RS08KA2 Series Data Sheet, Rev. 2

### Page

| 7.2 | External | Signal Description                      | 52 |

|-----|----------|-----------------------------------------|----|

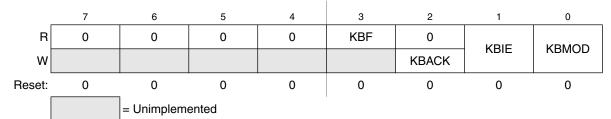

| 7.3 | Register | Definition                              | 53 |

|     | 0        | KBI Status and Control Register (KBISC) |    |

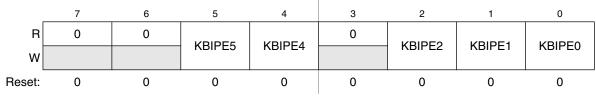

|     |          | KBI Pin Enable Register (KBIPE)         |    |

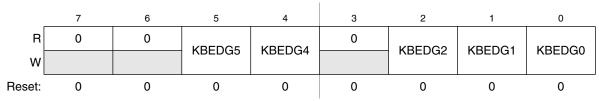

|     |          | KBI Edge Select Register (KBIES)        |    |

| 7.4 |          | al Description                          |    |

|     |          | Edge Only Sensitivity                   |    |

|     |          | Edge and Level Sensitivity              |    |

|     |          | KBI Pullup/Pulldown Device              |    |

|     |          | KBI Initialization                      |    |

Title

# Chapter 8 Central Processor Unit (RS08CPUV1)

| 8.1 | Introduction |                                                                  |    |

|-----|--------------|------------------------------------------------------------------|----|

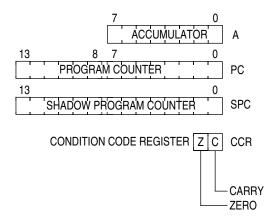

| 8.2 | Program      | mer's Model and CPU Registers                                    | 57 |

|     | 8.2.1        | Accumulator (A)                                                  |    |

|     | 8.2.2        | Program Counter (PC)                                             |    |

|     | 8.2.3        | Shadow Program Counter (SPC)                                     |    |

|     | 8.2.4        | Condition Code Register (CCR)                                    |    |

|     | 8.2.5        | Indexed Data Register (D[X])                                     | 60 |

|     | 8.2.6        | Index Register (X)                                               | 60 |

|     | 8.2.7        | Page Select Register (PAGESEL)                                   | 61 |

| 8.3 | Addressi     | ng Modes                                                         | 61 |

|     | 8.3.1        | Inherent Addressing Mode (INH)                                   | 61 |

|     | 8.3.2        | Relative Addressing Mode (REL)                                   |    |

|     | 8.3.3        | Immediate Addressing Mode (IMM)                                  | 62 |

|     | 8.3.4        | Tiny Addressing Mode (TNY)                                       | 62 |

|     | 8.3.5        | Short Addressing Mode (SRT)                                      | 63 |

|     | 8.3.6        | Direct Addressing Mode (DIR)                                     | 63 |

|     | 8.3.7        | Extended Addressing Mode (EXT)                                   | 63 |

|     | 8.3.8        | Indexed Addressing Mode (IX, Implemented by Pseudo Instructions) | 63 |

| 8.4 | Special C    | Derations                                                        | 63 |

|     | 8.4.1        | Reset Sequence                                                   | 64 |

|     | 8.4.2        | Interrupts                                                       | 64 |

|     | 8.4.3        | Wait and Stop Mode                                               | 64 |

|     | 8.4.4        | Active Background Mode                                           | 64 |

| 8.5 | Summary      | / Instruction Table                                              | 65 |

# Page

## Title

### Page

### Chapter 9 Internal Clock Source (RS08ICSV1)

| 9.1 | Introduct | tion                                            | 73 |

|-----|-----------|-------------------------------------------------|----|

| 9.2 | Introduct | tion                                            | 74 |

|     | 9.2.1     | Features                                        | 74 |

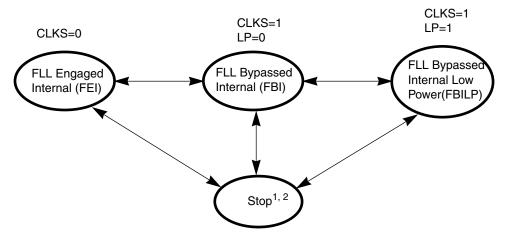

|     | 9.2.2     | Modes of Operation                              | 74 |

|     |           | 9.2.2.1 FLL Engaged Internal (FEI)              | 74 |

|     |           | 9.2.2.2 FLL Bypassed Internal (FBI)             | 74 |

|     |           | 9.2.2.3 FLL Bypassed Internal Low Power (FBILP) | 74 |

|     |           | 9.2.2.4 Stop (STOP)                             | 75 |

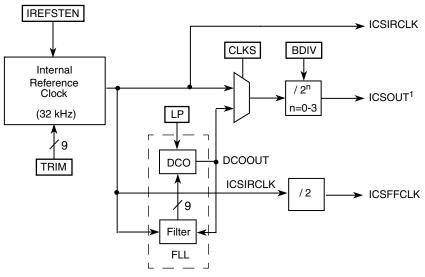

|     | 9.2.3     | Block Diagram                                   | 75 |

| 9.3 | External  | Signal Description                              | 75 |

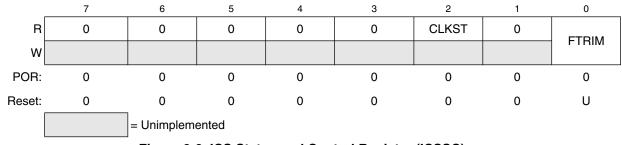

| 9.4 | Register  | Definition                                      | 76 |

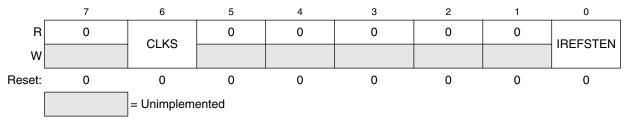

|     | 9.4.1     | ICS Control Register 1 (ICSC1)                  | 76 |

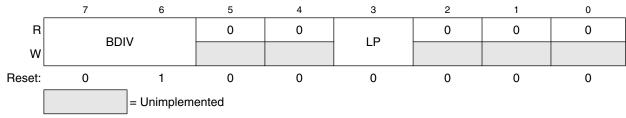

|     | 9.4.2     | ICS Control Register 2 (ICSC2)                  | 77 |

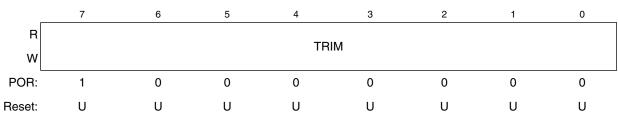

|     | 9.4.3     | ICS Trim Register (ICSTRM)                      |    |

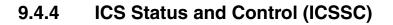

|     | 9.4.4     | ICS Status and Control (ICSSC)                  | 78 |

| 9.5 | Function  | nal Description                                 | 78 |

|     | 9.5.1     | Operational Modes                               |    |

|     |           | 9.5.1.1 FLL Engaged Internal (FEI)              |    |

|     |           | 9.5.1.2 FLL Bypassed Internal (FBI)             |    |

|     |           | 9.5.1.3 FLL Bypassed Internal Low Power (FBILP) |    |

|     |           | 9.5.1.4 Stop                                    | 79 |

|     | 9.5.2     | Mode Switching                                  | 79 |

|     | 9.5.3     | Bus Frequency Divider                           | 79 |

|     | 9.5.4     | Low Power Bit Usage                             | 79 |

|     | 9.5.5     | Internal Reference Clock                        | 80 |

|     | 9.5.6     | Fixed Frequency Clock                           | 80 |

# Chapter 10 Analog Comparator (RS08ACMPV1)

| 10.1 | Introduct | tion                                         | 81 |

|------|-----------|----------------------------------------------|----|

|      | 10.1.1    | Features                                     | 82 |

|      | 10.1.2    | Modes of Operation                           | 82 |

|      |           | 10.1.2.1 Operation in Wait Mode              | 82 |

|      |           | 10.1.2.2 Operation in Stop Mode              | 82 |

|      |           | 10.1.2.3 Operation in Active Background Mode | 82 |

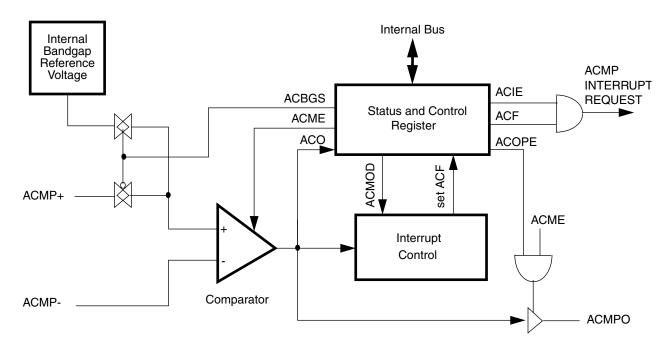

|      | 10.1.3    | Block Diagram                                | 82 |

| 10.2 | External  | Signal Description                           | 84 |

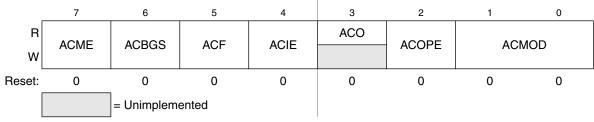

| 10.3 | Register  | Definition                                   | 84 |

|      | 10.3.1    | ACMP Status and Control Register (ACMPSC)    | 84 |

| 10.4 | Function  | al Description                               | 85 |

|      |           |                                              |    |

# Title

### Page

# Chapter 11 Modulo Timer (RS08MTIMV1)

| Introduct | tion                                                                                                   | 87                                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

|           |                                                                                                        |                                                                                                                              |

| 11.1.2    | Modes of Operation                                                                                     | 88                                                                                                                           |

|           | 11.1.2.1 Operation in Wait Mode                                                                        |                                                                                                                              |

|           | 11.1.2.2 Operation in Stop Modes                                                                       | 88                                                                                                                           |

|           | 11.1.2.3 Operation in Active Background Mode                                                           | 88                                                                                                                           |

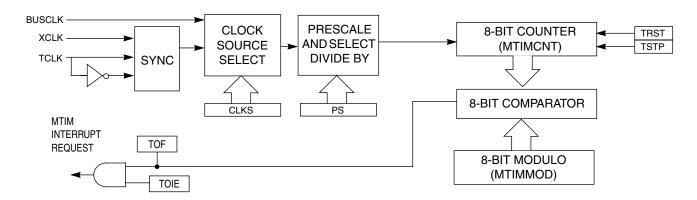

| 11.1.3    | Block Diagram                                                                                          | 89                                                                                                                           |

| External  | Signal Description                                                                                     | 89                                                                                                                           |

|           |                                                                                                        |                                                                                                                              |

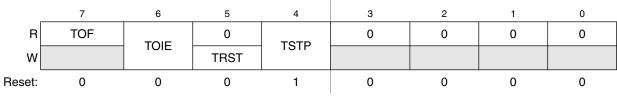

| 11.3.1    | MTIM Status and Control Register (MTIMSC)                                                              | 90                                                                                                                           |

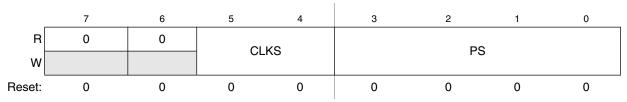

| 11.3.2    | MTIM Clock Configuration Register (MTIMCLK)                                                            | 91                                                                                                                           |

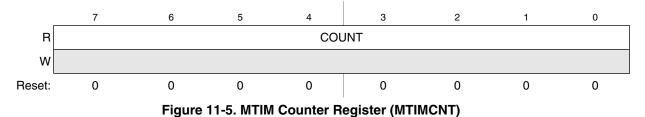

| 11.3.3    | MTIM Counter Register (MTIMCNT)                                                                        | 91                                                                                                                           |

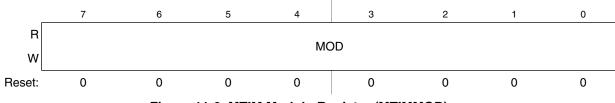

| 11.3.4    | MTIM Modulo Register (MTIMMOD)                                                                         | 92                                                                                                                           |

| Function  | al Description                                                                                         | 93                                                                                                                           |

|           |                                                                                                        |                                                                                                                              |

|           | 11.1.1<br>11.1.2<br>11.1.3<br>External<br>Register<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>Function | <ul><li>11.1.2 Modes of Operation</li><li>11.1.2.1 Operation in Wait Mode</li><li>11.1.2.2 Operation in Stop Modes</li></ul> |

# Chapter 12 Development Support

| 12.1 | Introduct | ion                                      | 95  |

|------|-----------|------------------------------------------|-----|

| 12.2 | Features  |                                          | 95  |

| 12.3 | RS08 Ba   | ckground Debug Controller (BDC)          | 96  |

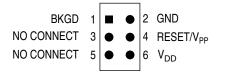

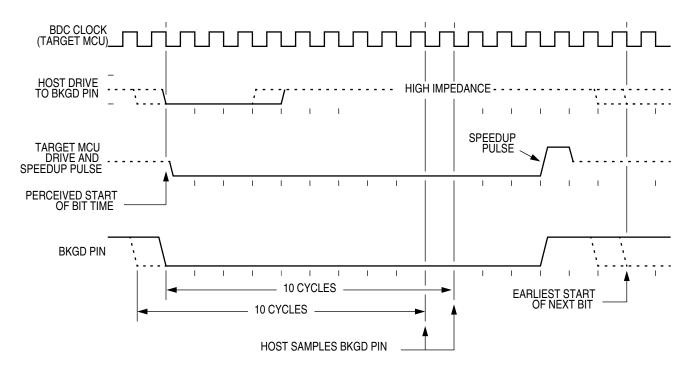

|      | 12.3.1    | BKGD Pin Description                     | 97  |

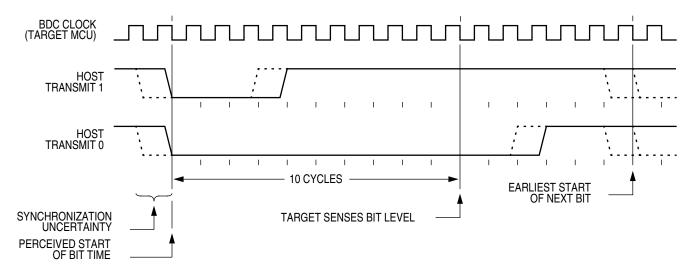

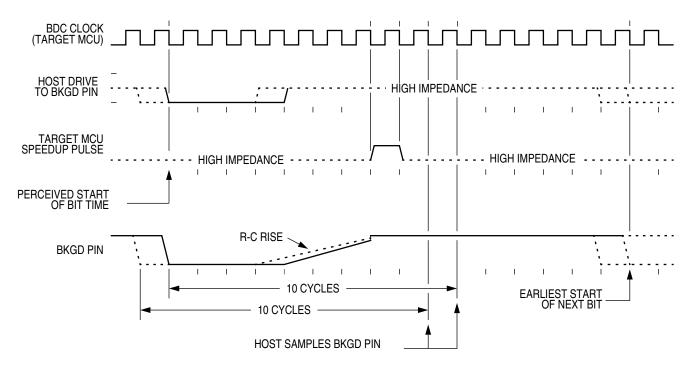

|      | 12.3.2    | Communication Details                    | 98  |

|      | 12.3.3    | SYNC and Serial Communication Timeout    | 100 |

| 12.4 | BDC Reg   | gisters and Control Bits                 | 101 |

|      | 12.4.1    | BDC Status and Control Register (BDCSCR) | 101 |

|      | 12.4.2    | BDC Breakpoint Match Register            | 102 |

| 12.5 | RS08 BD   | C Commands                               | 103 |

|      |           |                                          |     |

### Title

### Page

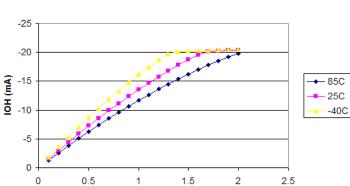

### Appendix A Electrical Characteristics

| A.1  | Introduction                                             | 107 |

|------|----------------------------------------------------------|-----|

| A.2  | Absolute Maximum Ratings                                 | 107 |

| A.3  | Thermal Characteristics                                  | 108 |

| A.4  | Electrostatic Discharge (ESD) Protection Characteristics | 109 |

|      | DC Characteristics                                       |     |

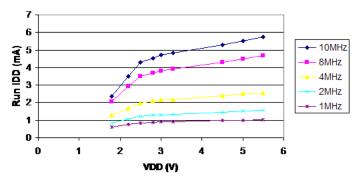

| A.6  | Supply Current Characteristics                           | 113 |

| A.7  | Analog Comparator (ACMP) Electricals                     | 115 |

| A.8  | Internal Clock Source Characteristics                    | 115 |

| A.9  | AC Characteristics                                       | 116 |

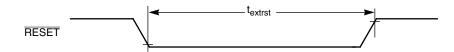

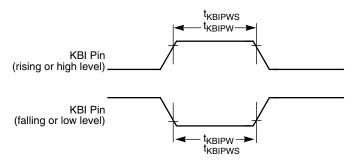

|      | A.9.1 Control Timing                                     | 116 |

| A.10 | FLASH Specifications                                     |     |

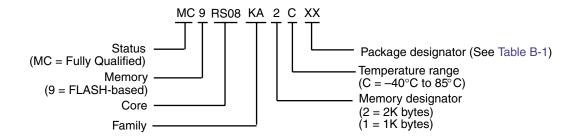

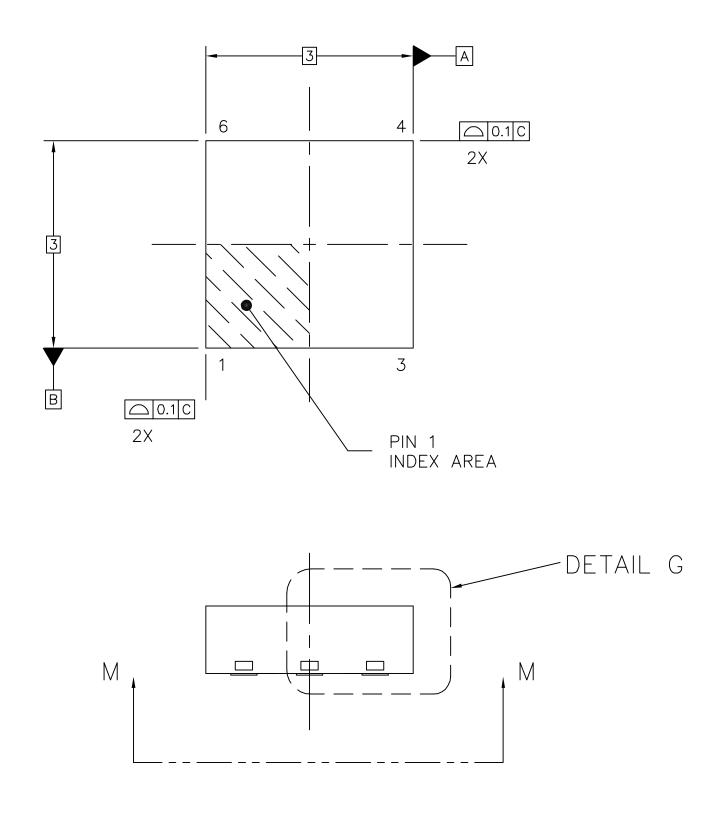

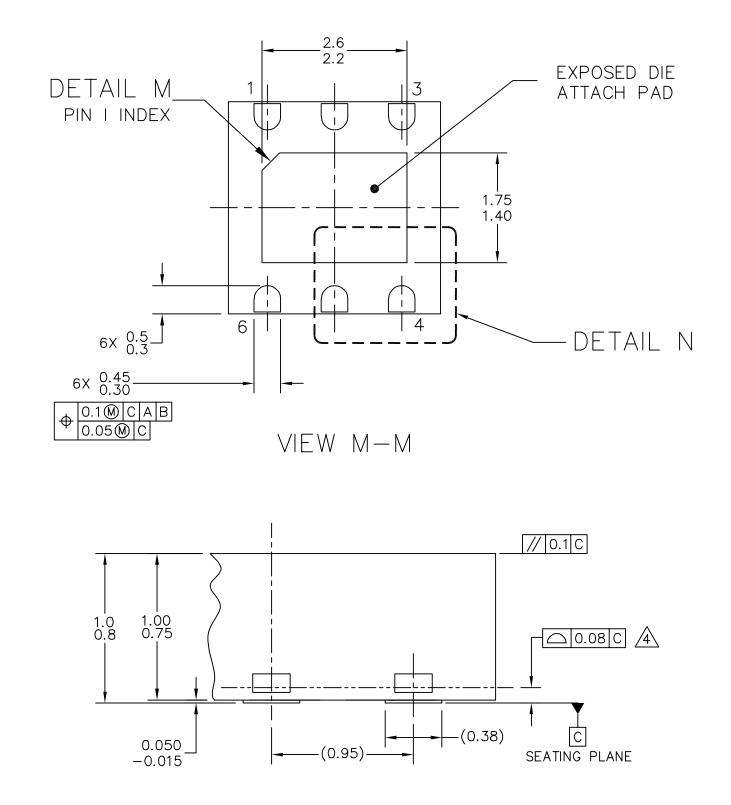

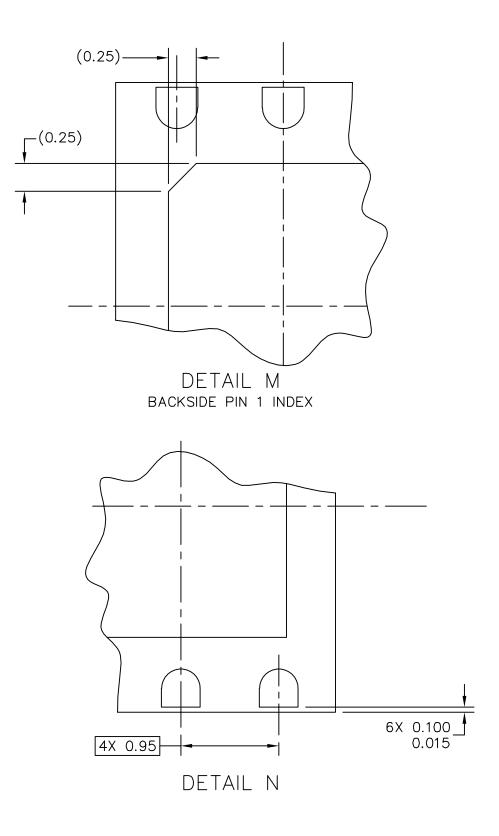

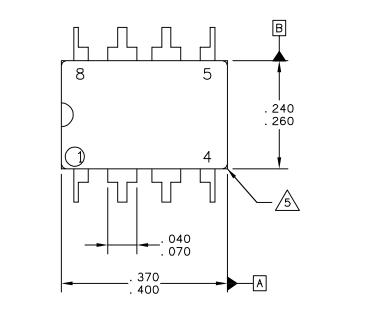

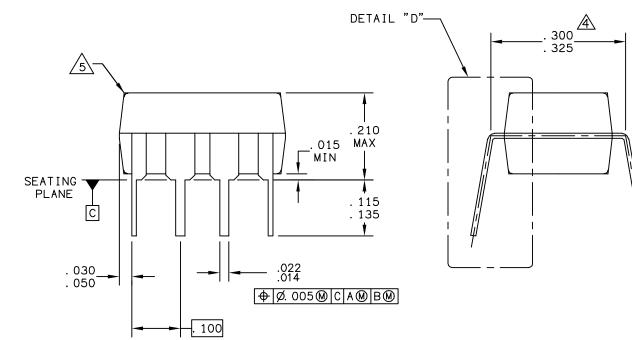

### Appendix B Ordering Information and Mechanical Drawings

| <b>B</b> .1 | Ordering Information | <br>.121 |

|-------------|----------------------|----------|

| B.2         | Mechanical Drawings  | <br>.121 |

# Chapter 1 MC9RS08KA2 Series Device Overview

### 1.1 Overview

The MC9RS08KA2 Series microcontroller unit (MCU) is an extremely low-cost, small pin count device for home appliances, toys, and small geometry applications. This device is composed of standard on-chip modules including, a very small and highly efficient RS08 CPU core, 63 bytes RAM, 2K bytes Flash, an 8-bit modulo timer, keyboard interrupt, and analog comparator. The device is available in small 6- and 8-pin packages.

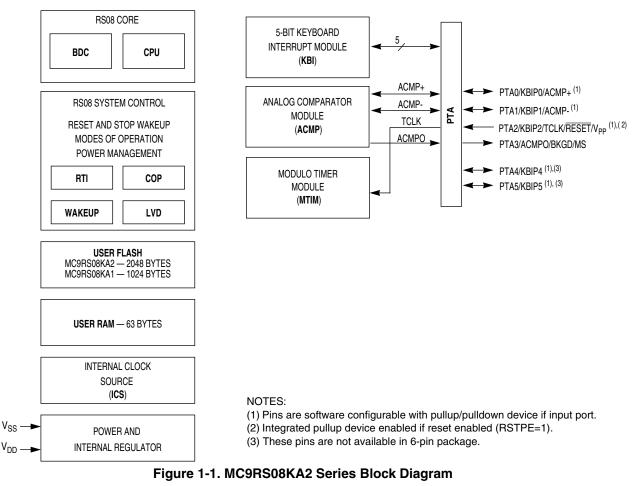

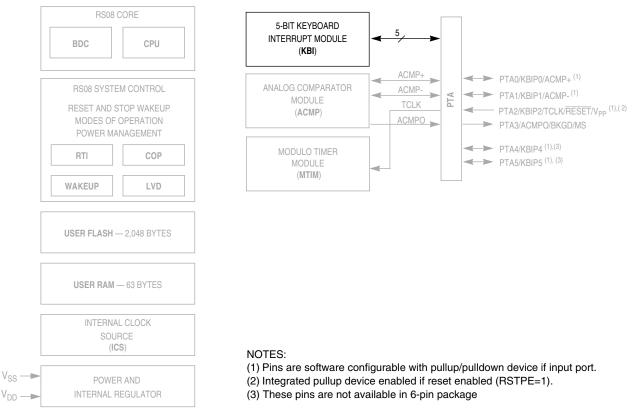

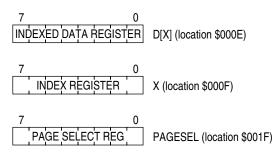

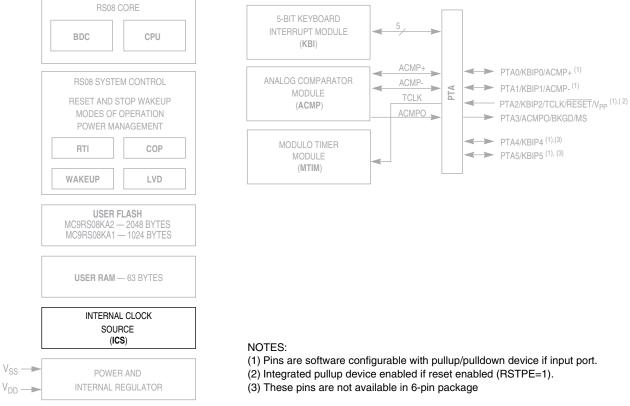

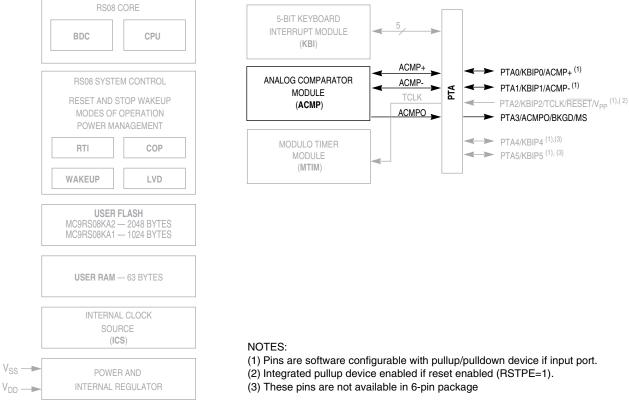

# 1.2 MCU Block Diagram

The block diagram, Figure 1-1, shows the structure of the MC9RS08KA2 Series MCU.

Table 1-1 provides the functional versions of the on-chip modules.

| Module                      | Version |

|-----------------------------|---------|

| Analog Comparator (ACMP)    | 1       |

| Keyboard Interrupt (KBI)    | 1       |

| Modulo Timer (MTIM)         | 1       |

| Internal Clock Source (ICS) | 1       |

#### Table 1-1. Block Versions

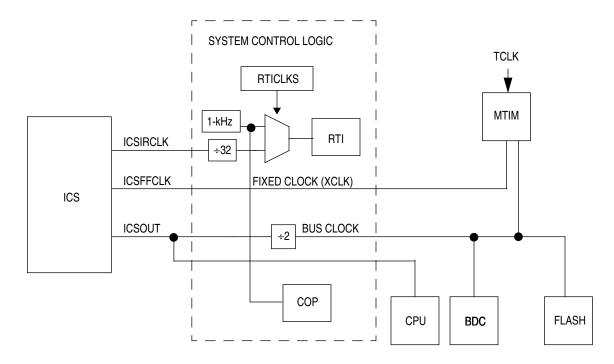

# **1.3 System Clock Distribution**

Figure 1-2 shows a simplified clock connection diagram for the MCU. The bus clock frequency is half of the ICS output frequency and is used by all of the internal modules.

# Chapter 2 Pins and Connections

# 2.1 Introduction

This chapter describes signals that connect to package pins. It includes a pinout diagram, a table of signal properties, and a detailed discussion of signals.

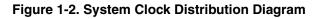

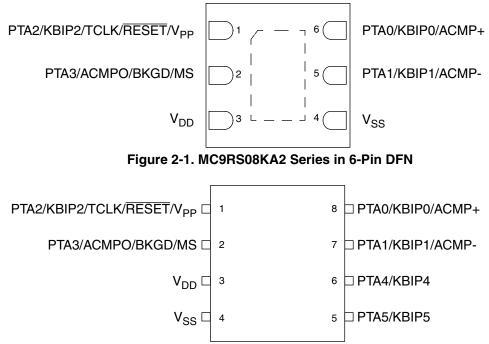

# 2.2 Device Pin Assignment

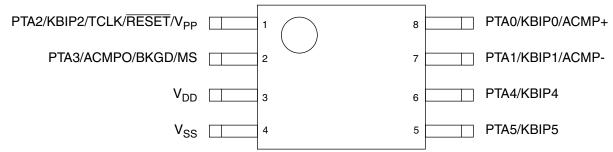

Figure 2-1 and Figure 2-3 show the pin assignments in the packages available for the MC9RS08KA2 Series.

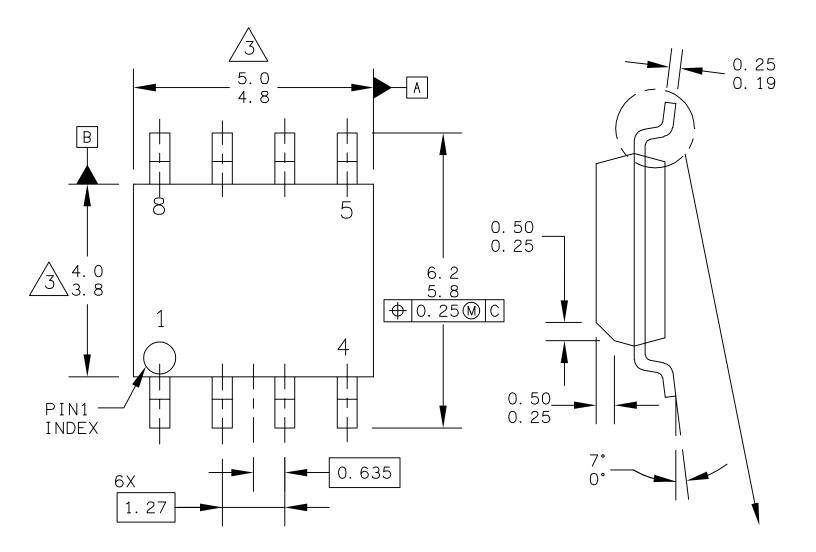

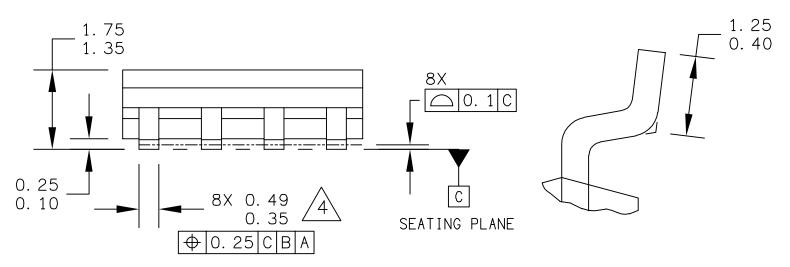

Figure 2-2. MC9RS08KA2 Series in 8-Pin PDIP

Figure 2-3. MC9RS08KA2 Series in 8-Pin Narrow Body SOIC

# 2.3 Recommended System Connections

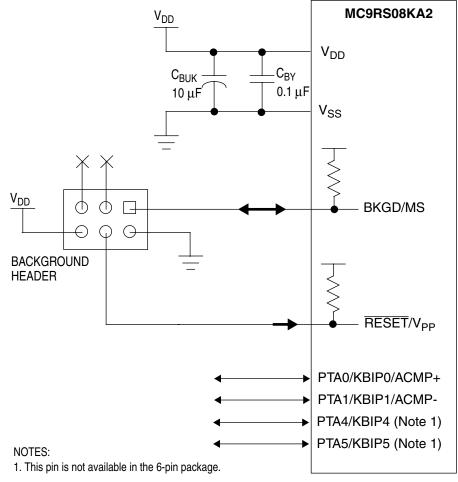

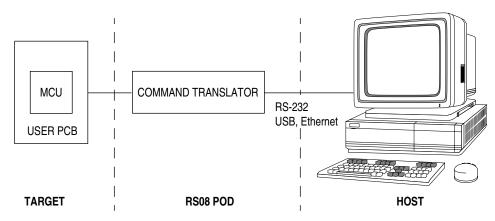

Figure 2-4 shows reference connection for background debug and Flash programming.

Figure 2-4. Reference System Connection Diagram

# 2.4 Pin Detail

This section provides a detailed description of system connections.

### 2.4.1 Power

$V_{DD}$  and  $V_{SS}$  are the primary power supply pins for the MCU. This voltage source supplies power to all I/O buffer circuitry and to an internal voltage regulator. The internal voltage regulator provides a regulated lower-voltage source to the CPU and other internal circuitry of the MCU.

Typically, application systems have two separate capacitors across the power pins: a bulk electrolytic capacitor, such as a 10- $\mu$ F tantalum capacitor, to provide bulk charge storage for the overall system, and a bypass capacitor, such as a 0.1- $\mu$ F ceramic capacitor, located as near to the MCU power pins as practical to suppress high-frequency noise.

# 2.4.2 PTA2/KBIP2/TCLK/RESET/V<sub>PP</sub>

After a power-on reset (POR) into user mode, the PTA2/KBIP2/TCLK/RESET/V<sub>PP</sub> pin defaults to a general-purpose input port pin, PTA2. Setting RSTPE in SOPT configures the pin to be the RESET input pin. After configured as RESET, the pin will remain as RESET until the next POR. The RESET pin can be used to reset the MCU from an external source when the pin is driven low. When enabled as the RESET pin (RSTPE = 1), the internal pullup device is automatically enabled.

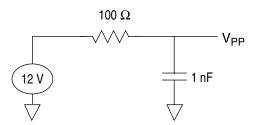

External  $V_{PP}$  voltage (typically 12 V, see Section A.10, "FLASH Specifications") is required on this pin when performing Flash programming or erasing. The  $V_{PP}$  connection is always connected to the internal Flash module regardless of the pin function. To avoid over stressing the Flash, external  $V_{PP}$  voltage must be removed and voltage higher than  $V_{DD}$  must be avoided when Flash programming or erasing is not taking place.

#### NOTE

This pin does not contain a clamp diode to  $V_{DD}$  and should not be driven above  $V_{DD}$  when Flash programming or erasing is not taking place.

### 2.4.3 PTA3/ACMPO/BKGD/MS

The background / mode select function is shared with an output-only pin on PTA3 pin and the optional analog comparator output. While in reset, the pin functions as a mode select pin. Immediately after reset rises, the pin functions as the background pin and can be used for background debug communication. While functioning as a background / mode select pin, this pin has an internal pullup device enabled. To use as an output-only port, BKGDPE in SOPT must be cleared.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD/MS low during the power-on-reset, which forces the MCU to active background mode.

The BKGD pin is used primarily for background debug controller (BDC) communications using a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock equals the bus clock rate; therefore, no significant capacitance should connected to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from

cables and the absolute value of the internal pullup device play almost no role in determining rise and fall times on the BKGD pin.

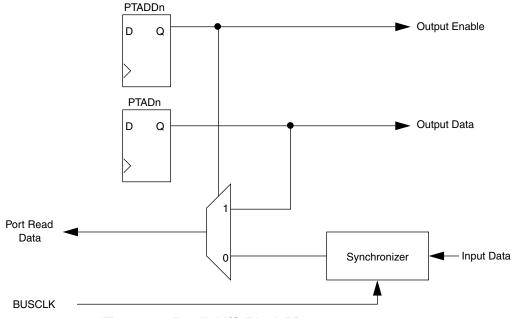

### 2.4.4 General-Purpose I/O and Peripheral Ports

The remaining pins are shared among general-purpose I/O and on-chip peripheral functions such as timers and analog comparator. Immediately after reset, all of these pins are configured as high-impedance general-purpose inputs with internal pullup/pulldown devices disabled.

#### NOTE

To avoid extra current drain from floating input pins, the reset initialization routine in the application program should either enable on-chip pullup/pulldown devices or change the direction of unused pins to outputs.

| Pin Name          | Direction        | Pullup/Pulldown <sup>1</sup> | Alternative Functions <sup>2</sup>                |                                                                                                                              |  |  |  |  |

|-------------------|------------------|------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| V <sub>DD</sub>   | _                | _                            |                                                   | Power                                                                                                                        |  |  |  |  |

| V <sub>SS</sub>   | —                | _                            |                                                   | Ground                                                                                                                       |  |  |  |  |

| PTA0              | I/O              | SWC                          | PTA0<br>KBIP0<br>ACMP+                            | General-purpose input/output (GPIO)<br>Keyboard interrupt (stop/wait wakeup only)<br>Analog comparator input                 |  |  |  |  |

| PTA1              | I/O              | SWC                          | PTA1<br>KBIP1<br>ACMP-                            | General-purpose input/output (GPIO)<br>Keyboard interrupt (stop/wait wakeup only)<br>Analog comparator input                 |  |  |  |  |

| PTA2              | I                | SWC <sup>4</sup>             | PTA2<br>KBIP2<br>TCLK<br>RESET<br>V <sub>PP</sub> | General-purpose input<br>Keyboard interrupt (stop/wait wakeup only)<br>Modulo timer clock source<br>Reset<br>V <sub>PP</sub> |  |  |  |  |

| PTA3              | I/O <sup>3</sup> | 4                            | PTA3<br>ACMPO<br>BKGD<br>MS                       | General-purpose output<br>Analog comparator output<br>Background debug data<br>Mode select                                   |  |  |  |  |

| PTA4 <sup>5</sup> | I/O              | SWC                          | PTA4<br>KBIP4                                     | General-purpose input/output (GPIO)<br>Keyboard interrupt (stop/wait wakeup only)                                            |  |  |  |  |

| PTA5 <sup>5</sup> | I/O              | SWC                          | PTA5<br>KBIP5                                     | General-purpose input/output (GPIO)<br>Keyboard interrupt (stop/wait wakeup only)                                            |  |  |  |  |

#### Table 2-1. Pin Sharing Reference

<sup>1</sup> SWC is software-controlled pullup/pulldown resistor; the register is associated with the respective port.

<sup>2</sup> Alternative functions are listed lowest priority first. For example, GPIO is the lowest priority alternative function of the PTA0 pin; ACMP+ is the highest priority alternative function of the PTA0 pin.

<sup>3</sup> Output-only when configured as PTA3 function.

- <sup>4</sup> When PTA2 or PTA3 is configured as RESET or BKGD/MS, respectively, pullup is enabled. When V<sub>PP</sub> is attached, pullup/pulldown is disabled automatically.

- <sup>5</sup> This pin is not available in 6-pin package. Enabling either the pullup or pulldown device is recommended to prevent extra current leakage from the floating input pin.

# Chapter 3 Modes of Operation

# 3.1 Introduction

This chapter describes the operating modes of the MC9RS08KA2 Series are described in this chapter. It also details entry into each mode, exit from each mode, and functionality while in each of the modes.

# 3.2 Features

- Active background mode for code development

- Wait mode:

- CPU shuts down to conserve power

- System clocks continue to run

- Full voltage regulation is maintained

- Stop mode:

- System clocks are stopped; voltage regulator in standby

- All internal circuits remain powered for fast recovery

# 3.3 Run Mode

This is the normal operating mode for the MC9RS08KA2 Series. This mode is selected when the BKGD/MS pin is high at the rising edge of reset. In this mode, the CPU executes code from internal memory with execution beginning at the address \$3FFD. A JMP instruction (opcode \$BC) with operand located at \$3FFE\_\$3FFF must be programmed for correct reset operation into the user application. The operand defines the location at which the user program will start. Instead of using the vector fetching process as in HC08/S08 families, the user program is responsible for performing a JMP instruction to relocate the program counter to the correct user program start location.

# 3.4 Active Background Mode

The active background mode functions are managed through the background debug controller (BDC) in the RS08 core. The BDC provides the means for analyzing MCU operation during software development.

Active background mode is entered in any of four ways:

- When the BKGD/MS pin is low during power-on-reset (POR) or immediately after issuing a background debug force reset (BDC\_RESET) command

- When a BACKGROUND command is received through the BKGD pin

- When a BGND instruction is executed

#### **Chapter 3 Modes of Operation**

• When a BDC breakpoint is encountered

After active background mode is entered, the CPU is held in a suspended state waiting for serial background commands rather than executing instructions from the user application program.

Background commands are of two types:

- Non-intrusive commands, defined as commands that can be issued while the user program is running, can be issued through the BKGD pin while the MCU is in run mode. Non-intrusive commands can also be executed when the MCU is in the active background mode. Non-intrusive commands include:

- Memory access commands

- Memory-access-with-status commands

- BACKGROUND command

- Active background commands, which can be executed only while the MCU is in active background mode, include commands to:

- Read or write CPU registers

- Trace one user program instruction at a time

- Leave active background mode to return to the user application program (GO)

Active background mode is used to program user application code into the Flash program memory before the MCU is operated in run mode for the first time. When the MC9RS08KA2 Series is shipped from the Freescale Semiconductor factory, the Flash program memory is usually erased so there is no program that could be executed in run mode until the Flash memory is initially programmed. The active background mode can also be used to erase and reprogram the Flash memory after it has been previously programmed.

For additional information about the active background mode, refer to the Development Support chapter of this data sheet.

### 3.5 Wait Mode

Wait mode is entered by executing a WAIT instruction. Upon execution of the WAIT instruction, the CPU enters a low-power state in which it is not clocked. The program counter (PC) is halted at the position where the WAIT instruction is executed. When an interrupt request occurs:

- 1. MCU exits wait mode and resumes processing.

- 2. PC is incremented by one and fetches the next instruction to be processed.

It is the responsibility of the user program to probe the corresponding interrupt source that woke the MCU, because no vector fetching process is involved.

While the MCU is in wait mode, not all background debug commands can be used. Only the BACKGROUND command and memory-access-with-status commands are available when the MCU is in wait mode. The memory-access-with-status commands do not allow memory access, but they report an error indicating that the MCU is in either stop or wait mode. The BACKGROUND command can be used to wake the MCU from wait mode and enter active background mode.

Table 3-1 summarizes the behavior of the MCU in wait mode.

| Mode | CPU     | Digital<br>Peripherals | ICS | ACMP          | Regulator | I/O Pins    | RTI           |

|------|---------|------------------------|-----|---------------|-----------|-------------|---------------|

| Wait | Standby | Optionally on          | On  | Optionally on | On        | States held | Optionally on |

Table 3-1. Wait Mode Behavior

# 3.6 Stop Mode

Stop mode is entered upon execution of a STOP instruction when the STOPE bit in the system option register is set. In stop mode, all internal clocks to the CPU and the modules are halted. If the STOPE bit is not set when the CPU executes a STOP instruction, the MCU will not enter stop mode and an illegal opcode reset is forced.

Table 3-2 summarizes the behavior of the MCU in stop mode.

Table 3-2. Stop Mode Behavior

| Мо  | de | CPU     | Digital<br>Peripherals | ICS <sup>1</sup> | ACMP <sup>2</sup> | Regulator | I/O Pins       | RTI <sup>3</sup> |

|-----|----|---------|------------------------|------------------|-------------------|-----------|----------------|------------------|

| Sto | р  | Standby | Standby                | Optionally<br>on | Optionally<br>on  | Standby   | States<br>held | Optionally on    |

<sup>1</sup> ICS requires IREFSTEN = 1 and LVDE and LVDSE must be set to allow operation in stop.

<sup>2</sup> If bandgap reference is required, the LVDE and LVDSE bits in the SPMSC1 must both be set before entering stop.

<sup>3</sup> If the 32-kHz trimmed clock in the ICS module is selected as the clock source for the RTI, LVDE and LVDSE bits in the SPMSC1 must both be set before entering stop.

Upon entering stop mode, all of the clocks in the MCU are halted. The ICS is turned off by default when the IREFSTEN bit is cleared and the voltage regulator is put in standby. The states of all of the internal registers and logic, as well as the RAM content, are maintained. The I/O pin states are held.

Exit from stop is done by asserting **RESET**, any asynchronous interrupt that has been enabled, or the real-time interrupt. The asynchronous interrupts are the KBI pins, LVD interrupt, or the ACMP interrupt.

If stop is exited by asserting the RESET pin, the MCU will be reset and program execution starts at location \$3FFD. If exited by means of an asynchronous interrupt or real-time interrupt, the next instruction after the location where the STOP instruction was executed will be executed accordingly. It is the responsibility of the user program to probe for the corresponding interrupt source that woke the CPU.

A separate self-clocked source ( $\approx 1 \text{ kHz}$ ) for the real-time interrupt allows a wakeup from stop mode with no external components. When RTIS = 000, the real-time interrupt function and the 1-kHz source are disabled. Power consumption is lower when the 1-kHz source is disabled, but in that case, the real-time interrupt cannot wake the MCU from stop.

The trimmed 32-kHz clock in the ICS module can also be enabled for the real-time interrupt to allow a wakeup from stop mode with no external components. The 32-kHz clock reference is enabled by setting

the IREFSTEN bit. For the ICS to run in stop, the LVDE and LVDSE bits in the SPMSC1 must both be set before entering stop.

# 3.6.1 Active BDM Enabled in Stop Mode

Entry into active background mode from run mode is enabled if the ENBDM bit in BDCSCR is set. This register is described in the Development Support chapter of this data sheet. If ENBDM is set when the CPU executes a STOP instruction, the system clocks to the background debug logic remain active when the MCU enters stop mode so background debug communication is still possible. In addition, the voltage regulator does not enter its low-power standby state; it maintains full internal regulation.

Most background commands are not available in stop mode. The memory-access-with-status commands do not allow memory access, but they report an error indicating that the MCU is in either stop or wait mode. The BACKGROUND command can be used to wake the MCU from stop and enter active background mode if the ENBDM bit is set. After active background mode is entered, all background commands are available.

Table 3-3 summarizes the behavior of the MCU in stop when entry into the active background mode is enabled.

| Mode | CPU     | Digital<br>Peripherals | ICS | АСМР             | Regulator | I/O Pins       | RTI           |

|------|---------|------------------------|-----|------------------|-----------|----------------|---------------|

| Stop | Standby | Standby                | On  | Optionally<br>on | On        | States<br>held | Optionally on |

Table 3-3. BDM Enabled Stop Mode Behavior

# 3.6.2 LVD Enabled in Stop Mode

The LVD system is capable of generating either an interrupt or a reset when the supply voltage drops below the LVD voltage. If the LVD is enabled in stop (LVDE and LVDSE bits in SPMSC1 both set) at the time the CPU executes a STOP instruction, the voltage regulator remains active.

Table 3-4 summarizes the behavior of the MCU in stop when LVD reset is enabled.

Table 3-4. LVD Enabled Stop Mode Behavior

| Mode | CPU     | Digital<br>Peripherals | ICS              | ACMP             | Regulator | I/O Pins       | RTI           |

|------|---------|------------------------|------------------|------------------|-----------|----------------|---------------|

| Stop | Standby | Standby                | Optionally<br>on | Optionally<br>on | On        | States<br>held | Optionally on |

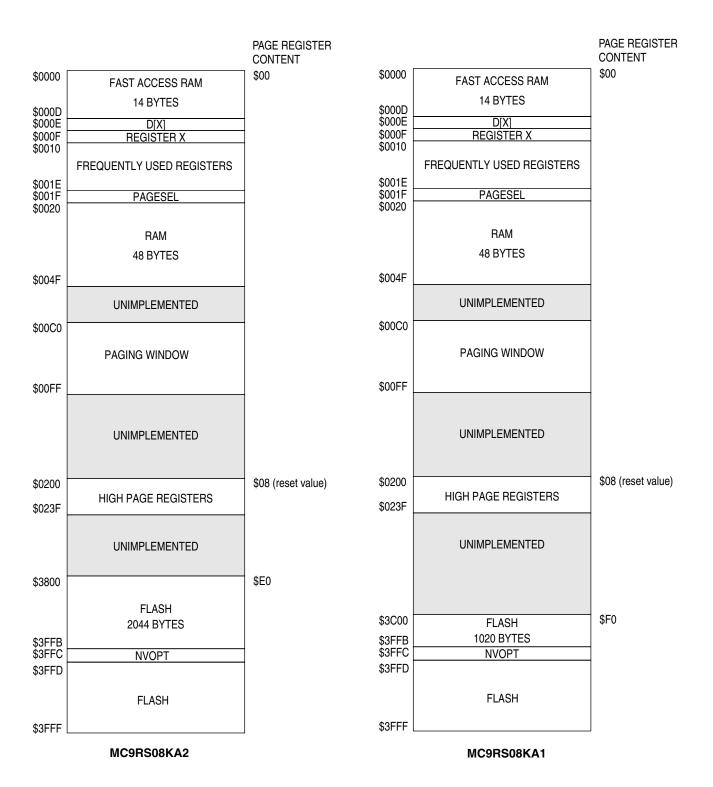

# Chapter 4 Memory

# 4.1 Memory Map

The memory map of the MCU is divided into the following groups:

- Fast access RAM using tiny and short instructions (\$0000-\$000E<sup>1</sup>)

- Indirect data access D[X] (\$000E)

- Index register X for D[X] (\$000F)

- Frequently used peripheral registers (\$0010–\$001E)

- PAGESEL register (\$001F)

- RAM (\$0020–\$004F)

- Paging window (\$00C0-\$00FF)

- Other peripheral registers (\$0200–\$023F)

- Nonvolatile memory

- MC9RS08KA2: \$3800-\$3FFF

- MC9RS08KA1: \$3C00—\$3FFF

<sup>1.</sup> Physical RAM in \$000E can be accessed through the D[X] register when the content of the index register X is \$0E.

#### **Chapter 4 Memory**

MC9RS08KA2 Series Data Sheet, Rev. 2

# 4.2 Unimplemented Memory

Attempting to access either data or an instruction at an unimplemented memory address will cause reset.

## 4.3 Indexed/Indirect Addressing

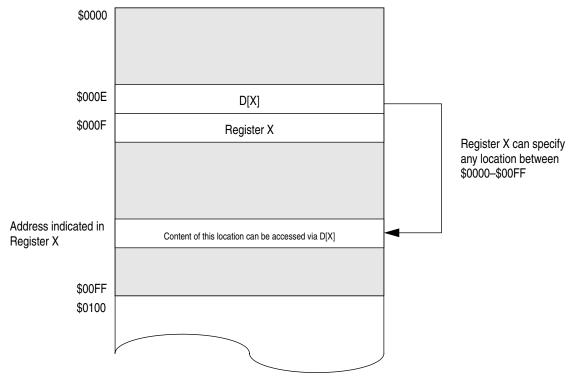

Register D[X] and register X together perform the indirect data access. Register D[X] is mapped to address \$000E. Register X is located in address \$000F. The 8-bit register X contains the address that is used when register D[X] is accessed. Register X is cleared to zero upon reset. By programming register X, any location on the first page (\$0000–\$00FF) can be read/written via register D[X]. Figure 4-2 shows the relationship between D[X] and register X. For example, in HC08/S08 syntax *lda*, *x* is comparable to *lda* D[X] in RS08 coding when register X has been programmed with the index value.

The physical location of \$000E is in RAM. Accessing the location through D[X] returns \$000E RAM content when register X contains \$0E. The physical location of \$000F is register X, itself. Reading the location through D[X] returns register X content; writing to the location modifies register X.

Figure 4-2. Indirect Addressing Registers

# 4.4 RAM and Register Addresses and Bit Assignments

The fast access RAM area can be accessed by instructions using tiny, short, and direct addressing mode instructions. For tiny addressing mode instructions, the operand is encoded along with the opcode to a single byte.

#### **Chapter 4 Memory**

Frequently used registers can make use of the short addressing mode instructions for faster load, store, and clear operations. For short addressing mode instructions, the operand is encoded along with the opcode to a single byte.

| Address           | Register Name     | Bit 7           | 6             | 5             | 4      | 3      | 2      | 1      | Bit 0    |  |

|-------------------|-------------------|-----------------|---------------|---------------|--------|--------|--------|--------|----------|--|

| \$0000-<br>\$000D |                   | Fast Access RAM |               |               |        |        |        |        |          |  |

| \$000E            | D[X] <sup>1</sup> | Bit 7           | 6             | 5             | 4      | 3      | 2      | 1      | Bit 0    |  |

| \$000F            | X                 | Bit 7           | 6             | 5             | 4      | 3      | 2      | 1      | Bit 0    |  |

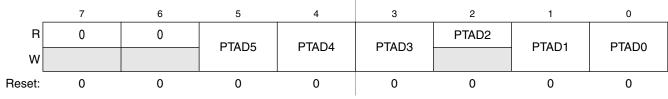

| \$00 <b>10</b>    | PTAD              | 0               | 0             | PTAD5         | PTAD4  | PTAD3  | PTAD2  | PTAD1  | PTAD0    |  |

| \$0011            | PTADD             | 0               | 0             | PTADD5        | PTADD4 | 0      | 0      | PTADD1 | PTADD0   |  |

| \$00 <b>12</b>    | Unimplemented     |                 |               | _             | _      |        |        |        | _        |  |

| \$00 <b>13</b>    | ACMPSC            | ACME            | ACBGS         | ACF           | ACIE   | ACO    | ACOPE  | ACM    | MOD      |  |

| \$00 <b>14</b>    | ICSC1             | 0               | CLKS          | 0             | 0      | 0      | 0      | 0      | IREFSTEN |  |

| \$00 <b>15</b>    | ICSC2             | BE              | DIV           | 0             | 0      | LP     | 0      | 0      | 0        |  |

| \$00 <b>16</b>    | ICSTRM            |                 |               |               | TR     | IM     |        |        |          |  |

| \$00 <b>17</b>    | ICSSC             | 0               | 0             | 0             | 0      | 0      | CLKST  | 0      | FTRIM    |  |

| \$00 <b>18</b>    | MTIMSC            | TOF             | TOIE          | TRST          | TSTP   | 0      | 0      | 0      | 0        |  |

| \$00 <b>19</b>    | MTIMCLK           | 0               | 0             | CL            | KS     |        | P      | Ś      | 1        |  |

| \$00 <b>1A</b>    | MTIMCNT           |                 | I             | 1             | COL    | JNT    |        |        |          |  |

| \$00 <b>1B</b>    | MTIMMOD           |                 |               |               | МС     | DD     |        |        |          |  |

| \$001 <b>C</b>    | KBISC             | 0               | 0             | 0             | 0      | KBF    | KBACK  | KBIE   | KBIMOD   |  |

| \$00 <b>1D</b>    | KBIPE             | _               |               | KBIPE5        | KBIPE4 | _      | KBIPE2 | KBIPE1 | KBIPE0   |  |

| \$00 <b>1E</b>    | KBIES             | _               |               | KBEDG5        | KBEDG4 | _      | KBEDG2 | KBEDG1 | KBEDG0   |  |

| \$001F            | PAGESEL           | AD13            | AD12          | AD11          | AD10   | AD9    | AD8    | AD7    | AD6      |  |

| \$0020–<br>\$004F |                   |                 |               | 1             | R      | AM     |        | 1      |          |  |

| \$0050–<br>\$00BF | Unimplemented     | _               | _             | _             | _      |        |        | _      | _        |  |

| \$00C0-<br>\$00FF |                   |                 |               |               | Paging | Window |        |        |          |  |

| \$0100–<br>\$01FF | Unimplemented     | _               | _             | _             | _      | _      | _      | _      | —        |  |

| \$0200            | SRS               | POR             | PIN           | COP           | ILOP   | ILAD   | 0      | LVD    | 0        |  |

| \$0201            | SOPT              | COPE            | COPT          | STOPE         | 0      | 0      | 0      | BKGDPE | RSTPE    |  |

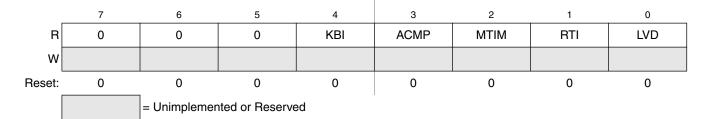

| \$0202            | SIP1              |                 | —             | —             | KBI    | ACMP   | MTIM   | RTI    | LVD      |  |

| \$0203            | Unimplemented     |                 | —             | —             | —      | _      | —      | —      | —        |  |

| \$0204            | Reserved          | —               | —             | —             | —      | _      | —      | —      | —        |  |

| \$0205            | Unimplemented     | —               | —             | —             | —      | _      |        |        | —        |  |

| \$0206            | SDIDH             | REV3            | REV2          | REV1          | REV0   |        | I      | D      |          |  |

| \$0207            | SDIDL             |                 |               |               |        | )      |        |        |          |  |

| \$0208            | SRTISC            | RTIF            | RTIACK        | RTICLKS       | RTIE   | 0      |        | RTIS   |          |  |

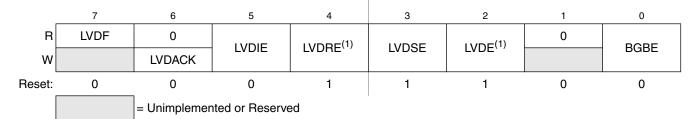

| \$0209            | SPMSC1            | LVDF            | LVDACK        | LVDIE         | LVDRE  | LVDSE  | LVDE   | 0      | BGBE     |  |

| \$020A            | Reserved          | —               | —             | —             | —      |        | —      | —      | —        |  |

| \$020B            | Reserved          |                 | —             | —             |        | —      | —      | —      | —        |  |

|                   |                   |                 | _ I Inimpleme | nted or Reser | ved    |        |        |        |          |  |

#### Table 4-1. Register Summary

= Unimplemented or Reserved

29

Chapter 4 Memory

| Address             | Register Name | Bit 7                       | 6                                      | 5       | 4        | 3      | 2       | 1       | Bit 0   |  |  |

|---------------------|---------------|-----------------------------|----------------------------------------|---------|----------|--------|---------|---------|---------|--|--|

| \$020C<br>\$020F    | Unimplemented | _                           | _                                      | _       | —        | _      | _       | _       | _       |  |  |

| \$0210              | FOPT          | 0                           | 0                                      | 0       | 0        | 0      | 0       | 0       | SECD    |  |  |

| \$0211              | FLCR          | 0                           | 0                                      | 0       | 0        | HVEN   | MASS    | 0       | PGM     |  |  |

| \$0212–<br>\$0213   | Reserved      | _                           | _                                      | _       | _        | _      | _       | _       | _       |  |  |

| \$0214-             | Unimplemented | —                           |                                        | —       | —        | _      | —       | _       | —       |  |  |

| \$021F              |               | —                           |                                        | —       | —        | —      | —       | —       | —       |  |  |

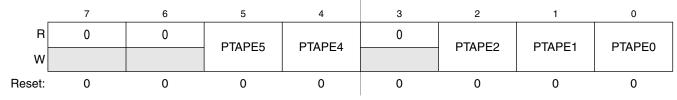

| \$0220              | PTAPE         | 0                           | 0                                      | PTAPE5  | PTAPE4   | 0      | PTAPE2  | PTAPE1  | PTAPE0  |  |  |

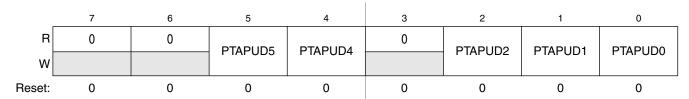

| \$0221              | PTAPUD        | 0                           | 0                                      | PTAPUD5 | PTAPUD4  | 0      | PTAPUD2 | PTAPUD1 | PTAPUD0 |  |  |

| \$0222              | PTASE         | 0                           | 0                                      | PTASE5  | PTASE4   | PTASE3 | 0       | PTASE1  | PTASE0  |  |  |

| \$0223–<br>\$023F   | Unimplemented | _                           | _                                      | _       | _        | _      | _       | _       | _       |  |  |

|                     |               |                             |                                        |         |          |        |         |         |         |  |  |

| \$3FF8              | Reserved      | —                           | _                                      | —       | —        | _      | —       |         | —       |  |  |

| \$3FF9              | Reserved      | _                           | _                                      |         | —        | _      |         | _       | —       |  |  |

| \$3FFA <sup>2</sup> | Reserved      |                             | Reserved for Room Temperature ICS Trim |         |          |        |         |         |         |  |  |

| \$3FFB <sup>2</sup> | Reserved      |                             |                                        |         | Reserved |        |         |         | FTRIM   |  |  |

| \$3FFC              | NVOPT         | 0                           | 0                                      | 0       | 0        | 0      | 0       | 0       | SECD    |  |  |

|                     |               | = Unimplemented or Reserved |                                        |         |          |        |         |         | ·       |  |  |

#### Table 4-1. Register Summary (continued)

Physical RAM in \$000E can be accessed through D[X] register when the content of the index register X is \$0E.

If using the MCU untrimmed, \$3FFA and \$3FFB may be used by applications.

# 4.5 RAM

2

The device includes two sections of static RAM. The locations from \$0000 to \$000D can be directly accessed using the more efficient tiny addressing mode instructions and short addressing mode instructions. Location \$000E RAM can either be accessed through D[X] register when register X is \$0E or through the paging window location \$00CE when PAGESEL register is \$00. The second section of RAM starts from \$0020 to \$004F, and it can be accessed using direct addressing mode instructions.

The RAM retains data when the MCU is in low-power wait and stop mode. RAM data is unaffected by any reset provided that the supply voltage does not drop below the minimum value for RAM retention.

# 4.6 Flash

The Flash memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the Flash memory after final assembly of the application product. It is possible to program the entire array through the single-wire background debug interface. Because the device does not include on-chip charge pump circuitry, external  $V_{PP}$  is required for program and erase operations.

### 4.6.1 Features

Features of the Flash memory include:

- Up to 1000 program/erase cycles at typical voltage and temperature

- Security feature for Flash

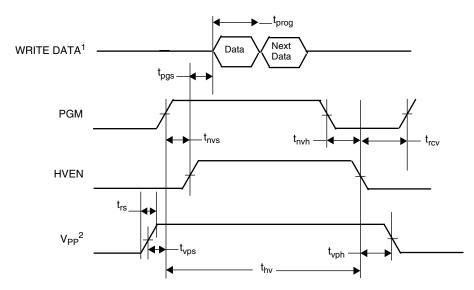

### 4.6.2 Flash Programming Procedure

Programming of Flash memory is done on a row basis. A row consists of 64 consecutive bytes starting from addresses \$3X00, \$3X40, \$3X80, or \$3XC0. Use the following procedure to program a row of Flash memory:

- 1. Apply external V<sub>PP</sub>.

- 2. Set the PGM bit. This configures the memory for program operation and enables the latching of address and data for programming.

- 3. Write any data to any Flash location, via the high page accessing window \$00C0-\$00FF, within the address range of the row to be programmed. (Prior to the data writing operation, the PAGESEL register must be configured correctly to map the high page accessing window to the corresponding Flash row).

- 4. Wait for a time,  $t_{nvs}$ .

- 5. Set the HVEN bit.

- 6. Wait for a time,  $t_{pgs}$ .

- 7. Write data to the Flash location to be programmed.

- 8. Wait for a time, t<sub>prog</sub>.

- 9. Repeat steps 7 and 8 until all bytes within the row are programmed.

- 10. Clear the PGM bit.

- 11. Wait for a time, t<sub>nvh</sub>.

- 12. Clear the HVEN bit.

- 13. After time,  $t_{rcv}$ , the memory can be accessed in read mode again.

- 14. Remove external V<sub>PP</sub>

This program sequence is repeated throughout the memory until all data is programmed.

#### NOTE

Flash memory cannot be programmed or erased by software code executed from Flash locations. To program or erase Flash, commands must be executed from RAM or BDC commands. User code should not enter wait or stop during erase or program sequence.

These operations must be performed in the order shown; other unrelated operations may occur between the steps.

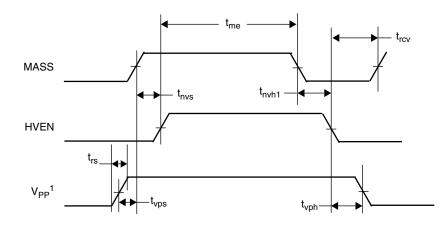

### 4.6.3 Flash Mass Erase Operation

Use the following procedure to mass erase the entire Flash memory:

- 1. Apply external V<sub>PP</sub>

- 2. Set the MASS bit in the Flash control register.

- 3. Write any data to any Flash location, via the high page accessing window \$00C0-\$00FF. (Prior to the data writing operation, the PAGESEL register must be configured correctly to map the high page accessing window to the any Flash locations).

- 4. Wait for a time,  $t_{nvs}$ .

- 5. Set the HVEN bit.

- 6. Wait for a time  $t_{me}$ .

- 7. Clear the MASS bit.

- 8. Wait for a time,  $t_{nvh1}$ .

- 9. Clear the HVEN bit.

- 10. After time,  $t_{rcv}$ , the memory can be accessed in read mode again.

- 11. Remove external V<sub>PP</sub>.

#### NOTE

Flash memory cannot be programmed or erased by software code executed from Flash locations. To program or erase Flash, commands must be executed from RAM or BDC commands. User code should not enter wait or stop during an erase or program sequence.

These operations must be performed in the order shown, but other unrelated operations may occur between the steps.

### 4.6.4 Security

The MC9RS08KA2 Series includes circuitry to help prevent unauthorized access to the contents of Flash memory. When security is engaged, Flash is considered a secure resource. The RAM, direct-page registers, and background debug controller are considered unsecured resources. Attempts to access a secure memory location through the background debug interface, or whenever BKGDPE is set, are blocked (reads return all 0s).

Security is engaged or disengaged based on the state of a nonvolatile register bit (SECD) in the FOPT register. During reset, the contents of the nonvolatile location NVOPT are copied from Flash into the working FOPT register in high-page register space. A user engages security by programming the NVOPT location, which can be done at the same time the Flash memory is programmed. Notice the erased state (SECD = 1) makes the MCU unsecure. When SECD in NVOPT is programmed (SECD = 0), next time the device is reset via POR, internal reset, or external reset, security is engaged. In order to disengage security, mass erase must be performed via BDM commands and followed by any reset.

The separate background debug controller can still be used for registers and RAM access. Flash mass erase is possible by writing to the Flash control register that follows the Flash mass erase procedure listed in Section 4.6.3, "Flash Mass Erase Operation," via BDM commands.

Security can always be disengaged through the background debug interface by following these steps:

- 1. Mass erase Flash via background BDM commands or RAM loaded program.

- 2. Perform reset and the device will boot up with security disengaged.

#### NOTE

When the device boots up to normal operating mode, where MS pin is high during reset, with SECD programmed (SECD = 0), Flash security is engaged. BKGDPE is reset to 0, and all BDM communication is blocked, and background debug is not allowed.

### 4.7 Flash Registers and Control Bits

The Flash module has a nonvolatile register, NVOPT (\$3FFC), in Flash memory which is copied into the corresponding control register, FOPT (\$0210), at reset.

# 4.7.1 Flash Options Register (FOPT and NVOPT)

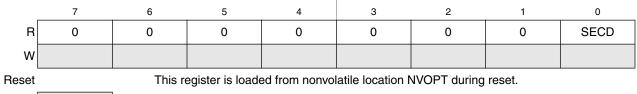

During reset, the contents of the nonvolatile location NVOPT is copied from Flash into FOPT. Bits 7 through 1 are not used and always read 0. This register may be read at any time, but writes have no meaning or effect. To change the value in this register, erase and reprogram the NVOPT location in Flash memory as usual and then issue a new MCU reset.

= Unimplemented or Reserved

#### Figure 4-3. Flash Options Register (FOPT)

| Field     | Description                                                                                                                                                                                                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>SECD | <ul> <li>Security State Code — This bit field determines the security state of the MCU. When the MCU is secured, the contents of Flash memory cannot be accessed by instructions from any unsecured source including the background debug interface; refer to Section 4.6.4, "Security".</li> <li>0 Security engaged.</li> <li>1 Security disengaged.</li> </ul> |

# 4.7.2 Flash Control Register (FLCR)

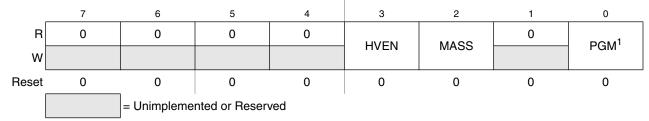

Figure 4-4. Flash Control Register (FLCR)

| Field                 | d Description                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 3<br>HVEN             | <ul> <li>High Voltage Enable — This read/write bit enables high voltages to the Flash array for program and erase operations. HVEN can be set only if either PGM = 1 or MASS = 1 and the proper sequence for program or erase is followed.</li> <li>0 High voltage disabled to array.</li> <li>1 High voltage enabled to array.</li> </ul> |  |  |  |  |  |  |

| 2<br>MASS             | Mass Erase Control Bit — This read/write bit configures the memory for mass erase operation.         0 Mass erase operation not selected.         1 Mass erase operation selected.                                                                                                                                                         |  |  |  |  |  |  |

| 0<br>PGM <sup>1</sup> | <ul> <li>Program Control Bit — This read/write bit configures the memory for program operation. PGM is interlocked with the MASS bit such that both bits cannot be equal to 1 or set to 1 at the same time.</li> <li>0 Program operation not selected.</li> <li>1 Program operation selected.</li> </ul>                                   |  |  |  |  |  |  |

<sup>1</sup> When Flash security is engaged, writing to PGM bit has no effect. As a result, Flash programming is not allowed.

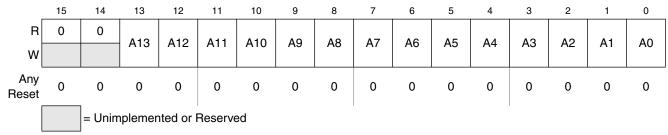

# 4.8 Page Select Register (PAGESEL)

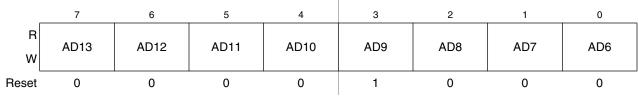

There is a 64-byte window (\$00C0-\$00FF) in the direct-page reserved for paging access. Programming the page select register determines the corresponding 64-byte block on the memory map for direct-page access. For example, when the PAGESEL register is programmed with value \$08, the high page registers (\$0200-\$023F) can be accessed through the paging window (\$00C0-\$00FF) via direct addressing mode instructions.

Figure 4-5. Page Select Register (PAGESEL)

| Table 4-4 | . PAGESEL | Field | Descriptions |

|-----------|-----------|-------|--------------|

|-----------|-----------|-------|--------------|

| Field           | Description                                                                                                                                                                                                   |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0<br>AD[13:6] | <b>Page Selector</b> — These bits define the address line bit 6 to bit 13, which determines the 64-byte block boundary of the memory block accessed via the direct page window. See Figure 4-6 and Table 4-5. |  |  |  |  |  |

#### MC9RS08KA2 Series Data Sheet, Rev. 2

|                                        |  |   | 1    | 4-b  | it m | em | ory | add | res | S |   |   |   |

|----------------------------------------|--|---|------|------|------|----|-----|-----|-----|---|---|---|---|

| Start address of memory block selected |  |   |      |      |      |    |     | 0   | 0   | 0 | 0 | 0 | 0 |

|                                        |  | A | \D[1 | 13:6 | ]    |    |     |     |     |   |   |   |   |

Figure 4-6. Memory Block Boundary Selector

Table 4-5 shows the memory block to be accessed through paging window (\$00C0–\$00FF). Table 4-5. Paging Window for \$00C0–\$00FF

| Page | Memory Address |

|------|----------------|

| \$00 | \$0000-\$003F  |

| \$01 | \$0040-\$007F  |

| \$02 | \$0080-\$00BF  |

| \$03 | \$00C0-\$00FF  |

| \$04 | \$0100-\$013F  |

|      |                |

| · .  | •              |

| \$FE | \$3F80-\$3FBF  |

| \$FF | \$3FC0-\$3FFF  |

#### NOTE

Physical location \$0000-\$000E is RAM. Physical location \$000F is register X. D[X] register is mapped to address \$000E only. The physical RAM in \$000E can be accessing through D[X] register when X register is either \$0E or \$CE with PAGESEL is \$00.

When PAGESEL register is \$00, paging window is mapped to the first page (\$00-\$3F). Paged location \$00C0-\$00CE is mapped to physical location \$0000-\$000E, i.e., RAM. Paged location \$00CF is mapped to register X. Therefore, accessing address \$CE returns the physical RAM content in \$000E, accessing address \$000E returns D[X] register content.

# Chapter 5 Resets, Interrupts, and General System Control

# 5.1 Introduction

This chapter discusses basic reset and interrupt mechanisms and the various sources of reset and interrupt in the MC9RS08KA2 Series. Some interrupt sources from peripheral modules are discussed in greater detail within other chapters of this data sheet. This chapter gathers basic information about all reset and interrupt sources in one place for easy reference. A few reset and wakeup sources, including the computer operating properly (COP) watchdog and real-time interrupt (RTI), are not part of on-chip peripheral systems with their own chapters but are part of the system control logic.

# 5.2 Features

Reset and interrupt features include:

- Multiple sources of reset for flexible system configuration and reliable operation

- System reset status register (SRS) to indicate the source of the most recent reset

- System interrupt pending register (SIP1) to indicate the status of pending system interrupts

- Analog comparator interrupt with enable

- Keyboard interrupt with enable

- Low-voltage detect interrupt with enable

- Modulo timer interrupt with enable

- Real-time interrupt with enable; available in stop with multiple rates based on a separate 1-kHz self-clocked source

# 5.3 MCU Reset

Resetting the MCU provides a way to start processing from a known set of initial conditions. During reset, most control and status registers are forced to initial values and the program counter is started from location \$3FFD. A JMP instruction (opcode \$BC) with operand located at \$3FFE-\$3FFF must be programmed into the user application for correct reset operation. The operand defines the location at which the user program will start. On-chip peripheral modules are disabled and I/O pins are initially configured as general-purpose high-impedance inputs with pullup/pulldown devices disabled.

The MC9RS08KA2 Series has seven sources for reset:

- External pin reset (PIN) enabled using RSTPE in SOPT

- Power-on reset (POR)

- Low-voltage detect (LVD)

- Computer operating properly (COP) timer

- Illegal opcode detect (ILOP)

- Illegal address detect (ILAD)

- Background debug forced reset via BDC command BDC\_RESET

Each of these sources, with the exception of the background debug forced reset, has an associated bit in the system reset status register (SRS).

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset if the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP counter periodically. If the application program gets lost and fails to reset the COP counter before it times out, a system reset is generated to force the system back to a known starting point.

After any reset, the COPE becomes set in SOPT, which enables the COP watchdog (see Section 5.8.2, "System Options Register (SOPT)," for additional information). If the COP watchdog is not used in an application, it can be disabled by clearing COPE. The COP counter is reset by writing any value to the address of SRS. This write does not affect the data in the read-only SRS. Instead, the act of writing to this address is decoded and sends a reset signal to the COP counter.

There is an associated short and long time-out controlled by COPT in SOPT. Table 5-1 summaries the control functions of the COPT bit. The COP watchdog operates from the 1-kHz clock source and defaults to the associated long time-out ( $2^8$  cycles).

| СОРТ | COP Overflow Count <sup>1</sup> |

|------|---------------------------------|

| 0    | 2 <sup>5</sup> cycles (32 ms)   |

| 1    | 2 <sup>8</sup> cycles (256 ms)  |

Table 5-1. COP Configuration Options

Values shown in this column are based on  $t_{RTI} \approx 1$  ms. See  $t_{RTI}$  in the Section A.9.1, "Control Timing," for the tolerance of this value.

Even if the application will use the reset default settings of COPE and COPT, the user should write to the write-once SOPT registers during reset initialization to lock in the settings. That way, they cannot be changed accidentally if the application program gets lost. The initial write to SOPT will reset the COP counter.

In background debug mode, the COP counter will not increment.

When the MCU enters stop mode, the COP counter is re-initialized to zero upon entry to stop mode. The COP counter begins from zero as soon as the MCU exits stop mode.

### 5.5 Interrupts

The MC9RS08KA2 Series does not include an interrupt controller with vector table lookup mechanism as used on the HC08 and HCS08 devices. However, the interrupt sources from modules such as LVD, KBI,

and ACMP are still available to wake the CPU from wait or stop mode. It is the responsibility of the user application to poll the corresponding module to determine the source of wakeup.

Each wakeup source of the module is associated with a corresponding interrupt enable bit. If the bit is disabled, the interrupt source is gated, and that particular source cannot wake the CPU from wait or stop mode. However, the corresponding interrupt flag will still be set to indicate that an external wakeup event has occurred.

The system interrupt pending register (SIP1) indicates the status of the system pending interrupt. When the read-only bit of the SIP1 is enabled, it shows there is a pending interrupt to be serviced from the indicated module. Writing to the register bit has no effect. The pending interrupt flag will be cleared automatically when the all corresponding interrupt flags from the indicated module are cleared.

# 5.6 Low-Voltage Detect (LVD) System

The MC9RS08KA2 Series includes a system to protect against low voltage conditions in order to protect memory contents and control MCU system states during supply voltage variations. The system is comprised of a power-on reset (POR) circuit and an LVD circuit with a predefined trip voltage. The LVD circuit is enabled with LVDE in SPMSC1. The LVD is disabled upon entering stop mode unless LVDSE is set in SPMSC1. If LVDSE and LVDE are both set, the current consumption in stop with the LVD enabled will be greater.

### 5.6.1 Power-On Reset Operation

When power is initially applied to the MCU, or when the supply voltage drops below the  $V_{POR}$  level, the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above the  $V_{LVD}$  level. Both the POR bit and the LVD bit in SRS are set following a POR.

### 5.6.2 LVD Reset Operation

The LVD can be configured to generate a reset upon detection of a low voltage condition by setting LVDRE to 1. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the level  $V_{LVD}$ . The LVD bit in the SRS register is set following either an LVD reset or POR.

### 5.6.3 LVD Interrupt Operation

When a low voltage condition is detected and the LVD circuit is configured using SPMSC1 for interrupt operation (LVDE set, LVDIE set, and LVDRE clear), LVDF in SPMSC1 will be set and an LVD interrupt request will occur.

# 5.7 Real-Time Interrupt (RTI)

The real-time interrupt function can be used to generate periodic interrupts. The RTI is driven from either the 1-kHz internal clock reference or the trimmed 32-kHz internal clock reference from the ICS module. The 32-kHz internal clock reference is divided by 32 by the RTI logic to produce a trimmed 1-kHz clock

for applications requiring more accurate real-time interrupts. The RTICLKS bit in SRTISC is used to select the RTI clock source. Both the1-kHz and 32-kHz clock sources for the RTI can be used when the MCU is in run, wait or stop mode. For the 32-kHz clock source to run in stop, the LVDE and LVDSE bits in the SPMSC1 must both be set before entering stop.

The SRTISC register includes a read-only status flag, a write-only acknowledge bit, and a 3-bit control value (RTIS) used to select one of seven wakeup periods or disable RTI. The RTI has a local interrupt enable, RTIE, to allow masking of the real-time interrupt. The RTI can be disabled by writing each bit of RTIS to 0s, and no interrupts will be generated. See Section 5.8.4, "System Real-Time Interrupt Status and Control Register (SRTISC)," for detailed information about this register.

### 5.8 Reset, Interrupt, and System Control Registers and Control Bits

Refer to the direct-page register summary in Chapter 4, "Memory," for the absolute address assignments for all registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

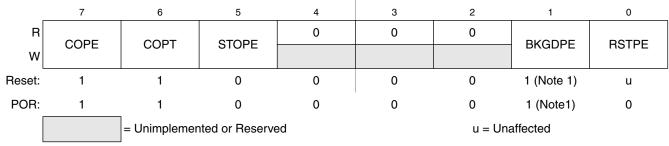

Some control bits in the SOPT register are related to modes of operation. Although brief descriptions of these bits are provided here, the related functions are discussed in greater detail in Chapter 3, "Modes of Operation".

### 5.8.1 System Reset Status Register (SRS)

This high page register includes read-only status flags to indicate the source of the most recent reset. When a debug host forces reset by the BDC\_RESET command, all of the status bits in SRS will be cleared. Writing any value to this register address clears the COP watchdog timer without affecting the contents of this register. The reset state of these bits depends on what caused the MCU to reset.

| _                   | 7   | 6      | 5               | 4             | 3             | 2              | 1    | 0 |

|---------------------|-----|--------|-----------------|---------------|---------------|----------------|------|---|