# SC4601 Low Input, High Efficiency Synchronous, Step Down Controller

# **POWER MANAGEMENT**

### Description

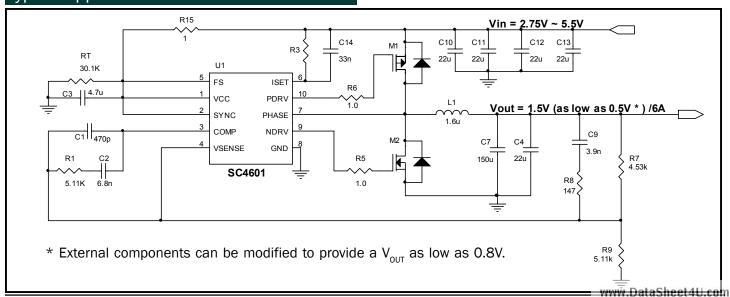

The SC4601 is a voltage mode step down (buck) regulator controller that provides accurate high efficiency power conversion from input supply range 2.75V to 5.5V. A high level of integration reduces external component count and makes it suitable for low voltage applications where cost, size and efficiency are critical.

The SC4601 drives external complementary power MOSFETs: P-channel on the high side and N-channel on the low side. The use of high side P-channel MOSFETs eliminates the need for an external charge pump and simplifies the high side gate driver. Non-overlap protection is provided for the gate drive signals to prevent shoot through of the MOSFET pair. The voltage drop across the P-channel MOSFET during its conduction is sensed for lossless short circuit current limiting.

A low power sleep mode can be achieved by forcing the SYNC/SLEEP pin below 0.8V. A synchronous mode of operation is activated as the SYNC/SLEEP pin is driven by an external clock. The quiescent supply current in sleep mode is typically lower than  $10\mu A.$  A 2.4ms soft start is internally provided to prevent output voltage overshoot during start-up. A 100% maximum duty cycle allows the SC4601 to operate as a low dropout regulator in the event of a low battery condition. Its switching frequency can be programmed up to 600KHz.

The SC4601 is an ideal choice for 3.3V, 5V or other low input supply systems. It's available in 10 pin MSOP package.

### **Features**

- Programmable switching frequency up to 600KHz

- ◆ BICMOS voltage mode PWM controller

- ◆ 2.75V to 5.5V Input voltage range

- ◆ Output voltage as low as 0.8V

- ♦ +/-1% Reference accuracy

- ◆ Sleep mode (Icc = 10µA typ)

- Lossless adjustable overcurrent protection

- Combination pulse by pulse & hiccup mode current limit

- High efficiency synchronous switching

- Up to 100% Duty cycle range

- Synchronization to external clock

- ◆ 10-Pin MSOP surface mount package. Available in Lead-free package, fully WEEE and RoHS compliant

# **Applications**

- ◆ Distributed power architecture

- Servers/workstations

- ◆ Local microprocessor core power supplies

- DSP and I/O power supplies

- Battery powered applications

- ◆ Telecommunication equipment

- Data processing applications

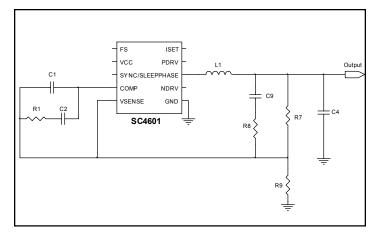

# Typical Application Circuit

# Absolute Maximum Ratings

Exceeding the specifications below may result in permanent damage to the device, or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not implied.

| Parameter                                       | Symbol            | Maximum     | Units |

|-------------------------------------------------|-------------------|-------------|-------|

| Supply Voltage (V <sub>cc</sub> )               |                   | 7           | V     |

| Output Drivers (PDRV, NDRV) Currents Continuous |                   | ±0.25       | А     |

| Inputs (VSENSE, COMP, SYNC/SLEEP, FS, ISET)     |                   | -0.3 to 7   | V     |

| Phase                                           |                   | -0.3 to 7   | V     |

| Phase Pulse tpulse < 50ns                       |                   | -2 to 7     | V     |

| Operating Ambient Temperature Range             | T <sub>A</sub>    | -40 to +85  | °C    |

| Storage Temperature Range                       | T <sub>STG</sub>  | -65 to +150 | °C    |

| Maximum Junction Temperature                    | T <sub>J</sub>    | +150        | °C    |

| Thermal Impedance Junction to Case              | $\theta_{JC}$     | 41.9        | °C/W  |

| Thermal Impedance Junction to Ambient           | $\theta_{JA}$     | 206         | °C/W  |

| Lead Temperature (Soldering) 10 Sec.            | T <sub>LEAD</sub> | +300        | °C    |

| ESD Rating (Human Body Model)                   | ESD               | 2           | kV    |

All voltages are with respect to GND. Currents are positive into, negative out of the specified terminal.

# Electrical Characteristics

Unless otherwise specified,  $V_{CC}$  = 3.3V,  $R_{T}$  = 59Kohm,  $T_{A}$  = -40°C to 85°C,  $T_{A}$  =  $T_{J.}$

| Parameter                 | Test Conditions                                      | Min   | Тур  | Max   | Unit |

|---------------------------|------------------------------------------------------|-------|------|-------|------|

| Overall                   |                                                      |       | •    |       |      |

| Supply Voltage            |                                                      | 2.75  |      | 5.5   | V    |

| Supply Current, Sleep     | V <sub>SYNC/SLEEP</sub> = 0V                         |       | 10   | 15    | μΑ   |

| Supply Current, Operating |                                                      |       | 1.5  | 3     | mA   |

| VCC Turn-on Threshold     |                                                      |       | 2.55 | 2.75  | V    |

| VCC Turn-off Hysteresis   |                                                      |       | 150  |       | mV   |

| Error Amplifier           |                                                      | ·     |      | •     |      |

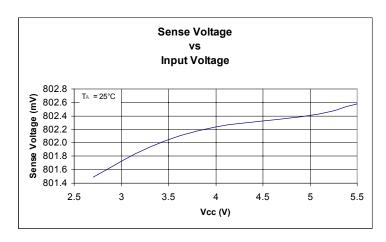

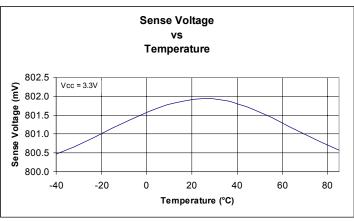

| Internal Reference        | T <sub>A</sub> = 25°C                                | 0.792 | 0.8  | 0.808 | .,   |

|                           | $V_{CC} = 2.75V \text{ to } 5.5V, T_A = 25^{\circ}C$ | 0.788 | 0.8  | 0.812 | V    |

|                           | Temperature                                          | 0.786 | 0.8  | 0.814 |      |

| VSENSE Bias Current       |                                                      |       | 25   |       | nA   |

| Open Loop Gain (1)        | $V_{COMP} = 0.4V \text{ to } 1.8V$                   | 70    | 80   |       | dB   |

| Unity Gain Bandwidth (1)  |                                                      |       | 4    |       | MHz  |

| Slew Rate (1)             |                                                      |       | 2    |       | V/µs |

# Electrical Characteristics (Cont.)

Unless otherwise specified,  $V_{CC}$  = 3.3V,  $R_T$  = 59Kohm,  $T_A$  = -40°C to 85°C,  $T_A$  =  $T_{J.}$

| Parameter                        | Test Conditions                                | Min | Тур  | Max | Unit |

|----------------------------------|------------------------------------------------|-----|------|-----|------|

| Error Amplifier (Cont.)          |                                                | 1   |      | 1   |      |

| VCOMP High                       | I <sub>COMP</sub> = -2mA                       | 2.8 | 3.1  |     | V    |

| VCOMP Low                        | I <sub>COMP</sub> = 2mA                        |     | 0.15 | 0.3 | V    |

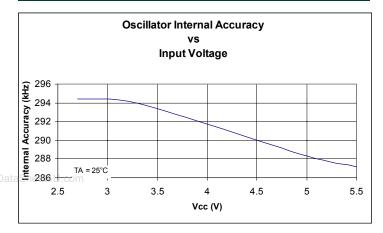

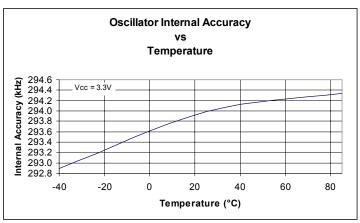

| Oscillator                       |                                                |     |      | 1   |      |

| Initial Accuracy                 | T <sub>A</sub> = 25°C, VSYNC/SLEEP = HIGH      | 260 | 300  | 340 | kHz  |

| Minimum Operation Frequency (1)  |                                                |     | 100  |     | kHz  |

| Maximum Operation Frequency (1)  |                                                |     |      | 600 | kHz  |

| SYNC/SLEEP Low Threshold         | $V_{iN} \leq 3.6V$                             |     |      | 0.8 | V    |

| SYNC/SLEEP High Threshold        | V <sub>IN</sub> ≤ 3.6V                         | 2.0 |      |     | V    |

| Ramp Peak to Valley (1)          |                                                | 1.3 | 1.5  | 1.7 | V    |

| Ramp Peak Voltage (1)            |                                                |     | 1.85 | 1.9 | V    |

| Ramp Valley Voltage (1)          |                                                | 0.3 | 0.35 |     | V    |

| Sleep, Soft Start, Current Limit |                                                |     |      |     |      |

| Sleep Input Bias Current         | VSYNC/SLEEP = 0V                               |     | -1   |     | μA   |

| Soft Start Time (1)              |                                                |     | 2.4  |     | ms   |

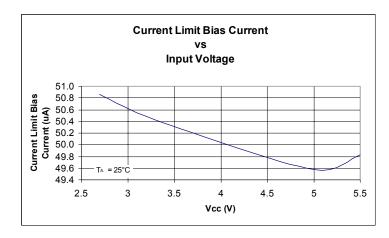

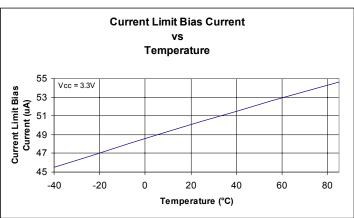

| Current Limit Threshold          | Bias Current, T <sub>J</sub> = 25°C            | -43 | -50  | -57 | μA   |

|                                  | Temperature Coefficient                        |     | 0.15 |     | %/°C |

| Current Limit Blank Time (1)     |                                                |     | 150  |     | ns   |

| N-Channel and P-Channel Drive    | r Outputs                                      |     |      |     |      |

| Pull Up Resistance (PDRV) (2)    | Vcc = 3.3V, I <sub>OUT</sub> = -100mA (source) |     |      | 3   | ohms |

| Pull Down Resistance (PDRV) (2)  | Vcc = 3.3V, I <sub>OUT</sub> = 50mA (sink)     |     |      | 3   | ohms |

| Pull Up Resistance (NDRV) (2)    | Vcc = 3.3V, I <sub>OUT</sub> = -100mA (source) |     |      | 3   | ohms |

| Pull Down Resistance (NDRV) (2)  | Vcc = 3.3V, I <sub>OUT</sub> = 100mA (sink)    |     |      | 3   | ohms |

| PDRV Output Rise Time (1)        | Vgs = 3.3V, C <sub>OUT</sub> = 1.0nF           |     | 9    |     | ns   |

| PDRV Output Fall Time (1)        | Vgs = 3.3V, C <sub>out</sub> = 1.0nF           |     | 12   |     | ns   |

# Electrical Characteristics (Cont.)

Unless otherwise specified,  $V_{CC}$  = 3.3V,  $R_T$  = 59Kohm,  $T_A$  = -40°C to 85°C,  $T_A$  =  $T_{J.}$

| Parameter                                      | Test Conditions                      | Min | Тур      | Max | Unit |

|------------------------------------------------|--------------------------------------|-----|----------|-----|------|

| N-channel and P-Channel Driver                 | Outputs (Cont.)                      |     |          |     |      |

| NDRV Output Rise Time (1)                      | Vgs = 3.3V, C <sub>OUT</sub> = 1.0nF |     | 15       |     | ns   |

| NDRV Output Fall Time (1)                      | Vgs = 3.3V, C <sub>OUT</sub> = 1.0nF |     | 15       |     | ns   |

| Deadtime Delay<br>(PDRV high to NDRV high) (1) |                                      |     | adaptive |     |      |

| Deadtime Delay (NDRV low to PDRV low) (1)      |                                      |     | 50       |     | ns   |

### Notes:

- (1) Guaranteed by design.

- (2) Guaranteed by characterization.

- (3) Dead time delay from PDRV high to NDRV high is adaptive. As the phase node voltage drops below 600mV due to PDRV high, NDRV will start to turn high.

# Marking Information Top Mark 4601 yyww Bottom Mark xxxx xxxx yyww = Datecode (Example: 0012) xxxxx = Semtech Lot # (Example: E901 xxxxx = 01-1)

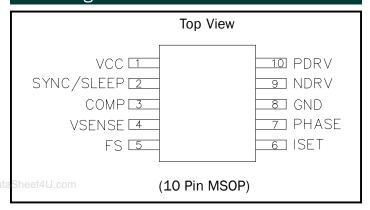

# Pin Configuration

# Pin Descriptions

**VCC:** Positive supply rail for the IC. Bypass this pin to GND with a 0.1 to  $4.7\mu F$  low ESL/ESR ceramic capacitor.

**GND:** All voltages are measured with respect to this pin. All bypass and timing capacitors connected to GND should have leads as short and direct as possible.

**FS:** An external resistor connected with FS pin sets the clock frequency.

**SYNC/SLEEP:** The oscillator frequency of SC4601 is set by FS when SYNC/SLEEP is pulled and held above 2V. Its synchronous mode operation is activated as the SYNC/SLEEP is driven by an external clock. The oscillator and PWM are designed to provide practical operation to 700kHz when synchronized with  $V_{\rm IN} \leq 3.6V$ . Sleep mode is invoked if SYNC/SLEEP is pulled and held below 0.8V which can be accomplished by an external gate or transistor. The Sleepmode supply current is  $10\mu$ A typical.

**VSENSE:** This pin is the inverting input of the voltage amplifier and serves as the output voltage feedback point for the Buck converter. It senses the output voltage through an external divider.

**COMP:** This is the output of the voltage amplifier. The voltage at this output is connected to the inverting input of the PWM comparator. A lead-lag network around the voltage amplifier compensates for the two pole LC filter characteristic inherent to voltage mode control and is required in order to optimize the dynamic performance of the voltage mode control loop.

# Ordering Information

| Part Number                 | Device <sup>(1)</sup> |

|-----------------------------|-----------------------|

| SC4601IMSTR                 | MSOP-10               |

| SC4601IMSTRT <sup>(2)</sup> | WISOP-10              |

| SC4601EVB                   | Evaluation Board      |

### Notes:

- (1) Only available in tape and reel packaging. A reel contains 2500 devices.

- (2) Lead free product. This product is fully WEEE and RoHS compliant.

PHASE, ISET: PHASE input is connected to the junction between the two external power MOSFET transistors. The voltage drop across the upper P-channel device is monitored by PHASE and ISET during PFET conduction and forms the current limit comparator and logic that sets the PWM latch and terminates the PFET output pulse once excessive voltage drop across the PFET is detected. The controller stops switching and goes through a soft start sequence once the converter output voltage drops below 68.75% its nominal voltage. This prevents excess power dissipation in the PMOSFET during a short circuit. The current limit threshold is set by the external resistor between VCC and ISET. The internal 50µA current source has a positive temperature coefficient that can compensate PMOSFET Rdson variation due to its junction temperature change.

**PDRV, NDRV:** The PWM circuitry provides complementary drive signals to the output stages. The Cross conduction of the external MOSFETs is prevented by monitoring the voltage on the P-channel and N-channel driver pins in conjunction with a time delay optimized for FET turn-off characteristics.

# Typical Characteristics

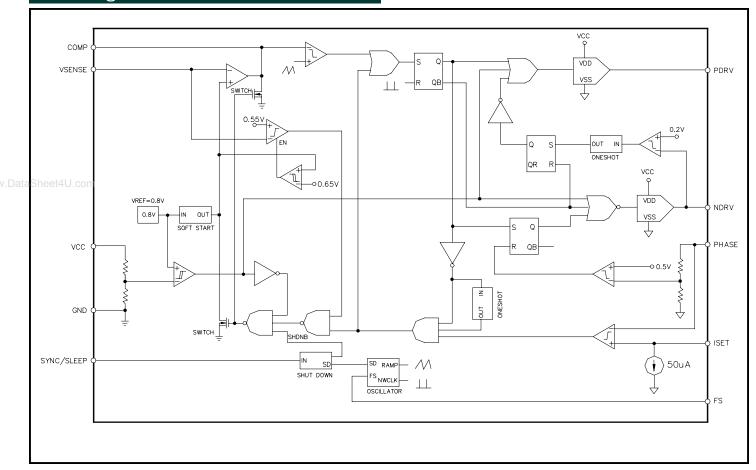

# **Block Diagram**

# **Applications Information**

### **Enable**

Pulling and holding the SYNC/SLEEP pin below 0.8V initializes the SLEEP mode of the SC4601with its typical SLEEP mode supply current of 10uA. During the SLEEP mode, the high side and low side MOSFETs are turned off and the internal soft start voltage is held low.

### **Oscillator**

The oscillator uses an external resistor to set the oscillation frequency when the SYNC/SLEEP pin is pulled and held above 2V. The ramp waveform is a triangle at the PWM frequency with a peak voltage of 1.85V and a valley voltage of 0.35V. A 100% maximum duty cycle allows the SC4601 to operate as a low dropout regulator in the event of a low battery condition. The resistor tolerance adds to the accuracy of the oscillator frequency. The external resistor connected to the FS pin, as shown below determines the approximate operating frequency:

$$f_{S} = \frac{1.66 \cdot 10^{7}}{R_{T}}$$

An external clock connected to the SYNC/SLEEP activates its synchronous mode and the frequency of the clock can be up to 700kHz with  $V_{\rm IN} \leq 3.6 {\rm V}$ .

### **UVLO**

When the SYNC/SLEEP pin is pulled and held above 2V, the voltage on the Vcc pin determines the operation of the SC4601. As Vcc increases during start up, the UVLO block senses Vcc and keeps the high side and low side MOSFETs off and the internal soft start voltage low until Vcc reaches 2.75V. If no faults are present, the SC4601 will initiate a soft start when Vcc exceeds 2.75V. A hysteresis (65mV) in the UVLO comparator provides noise immunity during its start up.

# Applications Information - (Cont.)

### **Soft Start**

The soft start function is required for step down controllers to prevent excess inrush current through the DC bus during start up. Generally this can be done by sourcing a controlled current into a timing capacitor and then using the voltage across this capacitor to slowly ramp up the error amp reference. The closed loop creates narrow width driver pulses while the output voltage is low and allows these pulses to increase to their steady state duty cycle as the output voltage reaches its regulated value. With this, the inrush current from the input side is controlled. The duration of the soft start in the SC4601 is controlled by an internal timing circuit which is used during start up and over current to set the hiccup time. The soft start time can be calculated by:

$$T_{SOFT\_START} = \frac{720}{f_s}$$

As can be seen here, the soft start time is switching frequency dependant. For example, if  $f_s$  = 400kHz,  $T_{SOFT-START}$  = 720/400k = 1.8ms. But if  $f_s$  = 600kHz,  $T_{SOFT-START}$  = 720/600k = 1.2ms.

The SC4601 implements its soft start by ramping up the error amplifier reference voltage providing a controlled slew rate of the output voltage, then preventing overshoot and limiting inrush current during its start up.

### **Over Current Protection**

Over current protection for the SC4601 is implemented by detecting the voltage drop of the high side P-MOSFET during conduction, also known as high side  $R_{\rm DS(ON)}$  detection. This loss-less detection eliminates the sense resistor and its loss. The overall efficiency is improved and the number of components and cost of the converter are reduced.  $R_{\rm DS(ON)}$  sensing is by default inaccurate and is mainly used to protect the power supply during a fault case. The over current trigger point will vary from unit to unit as the  $R_{\rm DS(ON)}$  of P-MOSFET varies. Even for the same unit, the over current trigger point will vary as the junction temperature of P-MOSFET varies. The SC4601 provides a built-in 50 $\mu$ A current source, which is combined with  $R_{\rm SET}$  (connected between  $V_{\rm CC}$  and  $I_{\rm SET}$ ) to determine the current limit threshold. The value of  $R_{\rm SET}$  can be properly selected according to the desired current limit point

$I_{_{MAX}}$  and the internal 50µA pull down current available on the  $I_{_{SFT}}$  pin based on the following expression:

$$R_{SET} = \frac{I_{MAX} \bullet R_{DS(ON)}}{50\mu A}$$

Kelvin sensing connections should be used at the drain and source of P-MOSFET. R needs to be adjusted if the input of the application changes significantly, say from 3.3V to 5V for the same load and same output voltage.

The R<sub>DS(ON)</sub> sensing used in the SC4601 has an additional feature that enhances the performance of the over current protection. Because the R<sub>DS(ON)</sub> has a positive temperature coefficient, the 50 $\mu$ A current source has a positive coefficient of about 0.15%/C° providing first order correction for current sensing vs temperature. This compensation depends on the high amount of thermal transferring that typically exists between the high side P-MOSFET and the SC4601 due to the compact layout of the power supply.

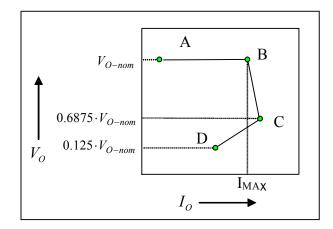

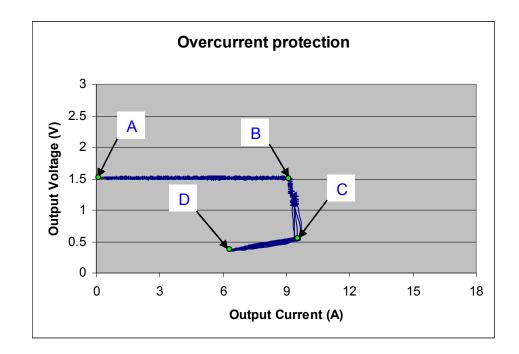

When the converter detects an over current condition (I  $> I_{MAX}$ ) as shown in Figure 1, the first action the SC4601 takes is to enter cycle by cycle protection mode (Point B to Point C), which responds to minor over current cases. Then the output voltage is monitored. If the over current and low output voltage (set at 68.75% of nominal output voltage) occur at the same time, the Hiccup mode operation (Point C to Point D) of the SC4601 is invoked and the internal soft start capacitor is discharged. This is like a typical soft start cycle.

Figure 1. Over current protection characteristic of SC4601

## Applications Information - (Cont.)

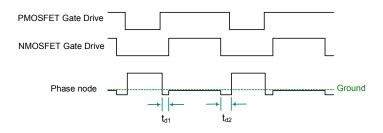

### **Power MOSFET Drivers**

The SC4601 has two drivers for external complementary power MOSFETs. The driver block consists of one high side P-MOSFET,  $4\Omega$  driver, PDRV, and one low side  $5\Omega$ , N-MOSFET driver, NDRV, which are optimized for driving external power MOSFETs in a synchronous buck converter. The output drivers also have gate drive non-overlap mechanism that gives a dead time between PDRV and NDRV transitions to avoid potential shoot through problems in the external MOSFETs. By using the proper design and the appropriate MOSFETs, a 6A converter can be achieved. As shown in Figure 2,  $t_{d1}$  the delay from the P-MOSFET off to the N-MOSFET on is adaptive by detecting the voltage of the phase node. t<sub>d2</sub>, the delay from the N-MOSFET off to the P-MOSFET on is fixed, is 50ns for the SC4601. This control scheme guarantees avoiding the cross conduction or shoot through between two MOSFETs and minimizes the conduction loss in the bottom diode for high efficiency applications.

Figure 2. Timing Waveforms for Gate Drives and Phase Node

### **Inductor Selection**

The factors for selecting the inductor include its cost, efficiency, size and EMI. For a typical SC4601 application, the inductor selection is mainly based on its value, saturation current and DC resistance. Increasing the inductor value will decrease the ripple level of the output voltage while the output transient response will be degraded. Low value inductors offer small size and fast transient responses while they cause large ripple currents, poor efficiencies and more output capacitance to smooth out the large ripple currents. The inductor should be able to handle the peak current without saturating and its copper resistance in the winding should be as low as possible to minimize its resistive power loss. A good tradeoff among its size, loss and cost is to set the inductor

ripple current to be within 15% to 30% of the maximum output current.

The inductor value can be determined according to its operating point and the switching frequency as follows:

$$L = \frac{V_{O} \cdot (V_{I} - V_{O})}{V_{I} \cdot f_{s} \cdot \Delta I \cdot I_{OMAX}}$$

Where:

f = switching frequency and

$\Delta I$  = ratio of the peak to peak inductor current to the maximum output load current.

The peak to peak inductor current is:

$$I_{p-p} = \Delta I \bullet I_{OMAX}$$

After the required inductor value is selected, the proper selection of the core material is based on the peak inductor current and efficiency requirements. The core must be able to handle the peak inductor current  $I_{\text{PEAK}}$  without saturation and produce low core loss during the high frequency operation.

$$I_{PEAK} = I_{OMAX} + \frac{I_{p-p}}{2}$$

The power loss for the inductor includes its core loss and copper loss. If possible, the winding resistance should be minimized to reduce inductor's copper loss. The core loss can be found in the manufacturer's datasheet. The inductor' copper loss can be estimated as follows:

$$P_{COPPER} = I^2_{LRMS} \cdot R_{WINDING}$$

Where:

$\rm I_{\rm LRMS}$  is the RMS current in the inductor. This current can be calculated as follows:

$$I_{LRMS} = I_{OMAX} \cdot \sqrt{1 + \frac{1}{3} \cdot \Delta I^2}$$

### **Output Capacitor Selection**

Basically there are two major factors to consider in selecting the type and quantity of the output capacitors. The first one is the required ESR (Equivalent Series Resistance) which should be low enough to reduce the voltage deviation from its nominal one during its load changes. The second one is the required capacitance, which should be high enough to hold up the output voltage. Before the SC4601 regulates the inductor current to a new value

# Applications Information - (Cont.)

during a load transient, the output capacitor delivers all the additional current needed by the load. The ESR and ESL of the output capacitor, the loop parasitic inductance between the output capacitor and the load combined with inductor ripple current are all major contributors to the output voltage ripple. Surface mount speciality polymer aluminum electrolytic chip capacitors in UE series from Panasonic provide low ESR and reduce the total capacitance required for a fast transient response. POSCAP from Sanyo is a solid electrolytic chip capacitor which has a low ESR and good performance for high frequency with a low profile and high capacitance. Above mentioned capacitors are recommended to use in SC4601 applications.

### **Input Capacitor Selection**

The input capacitor selection is based on its ripple current level, required capacitance and voltage rating. This capacitor must be able to provide the ripple current by the switching actions. For the continuous conduction mode, the RMS value of the input capacitor can be calculated from:

$$I_{\text{CIN}(\text{RMS})} = I_{\text{OMAX}} \cdot \sqrt{\frac{V_{\text{O}} \cdot (V_{\text{I}} - V_{\text{O}})}{V_{\text{I}}^2}}$$

This current gives the capacitor's power loss as follows:

$$P_{CIN} = I^2_{CIN(RMS)} \cdot R_{CIN(ESR)}$$

This capacitor's RMS loss can be a significant part of the total loss in the converter and reduce the overall converter efficiency. The input ripple voltage mainly depends on the input capacitor's ESR and its capacitance for a given load, input voltage and output voltage. Assuming that the input current of the converter is constant, the required input capacitance for a given voltage ripple can be calculated by:

$$C_{IN} = I_{OMAX} \cdot \frac{D \cdot (1-D)}{fs \cdot (\Delta V_I - I_{OMAX} \cdot R_{CIN(ESR)})}$$

Where:

D =  $V_0/V_1$ , duty ratio and  $\Delta V_1$  = the given input voltage ripple.

Because the input capacitor is exposed to the large surge current, attention is needed for the input capacitor. If tantalum capacitors are used at the input side of the converter, one needs to ensure that the RMS and surge ratings are not exceeded. For generic tantalum capacitors, it is wise to derate their voltage ratings at a ratio of 2 to protect these input capacitors.

### **Power MOSFET Selection**

The SC4601 can drive a P-MOSFET at the high side and an N-MOSFET synchronous rectifier at the low side. The use of the high side P-MOSFET eliminates the need for an external charge pump and simplifies the high side gate driver circuit.

For the top MOSFET, its total power loss includes its conduction loss, switching loss, gate charge loss, output capacitance loss and the loss related to the reverse recovery of the bottom diode, shown as follows:

$$\begin{split} P_{\text{TOP\_TOTAL}} = I^2_{\text{TOP\_RMS}} \cdot R_{\text{TOP\_ON}} + \frac{I_{\text{TOP\_PEAK}} \cdot V_I \cdot f_s}{V_{\text{GATE}}} \cdot \\ (Q_{\text{GD}} + Q_{\text{GS2}}) + Q_{\text{GT}} \cdot V_{\text{GATE}} \cdot f_s + (Q_{\text{OSS}} + Q_{\text{IT}}) \cdot V_I \cdot f_s \end{split}$$

### Where:

R<sub>e</sub> = gate drive resistor,

$Q_{\rm GD}$  = the gate to drain charge of the top MOSFET,  $Q_{\rm GS2}$  = the gate to source charge of the top MOSFET,  $Q_{\rm GT}$  = the total gate charge of the top MOSFET,  $Q_{\rm OSS}$  = the output charge of the top MOSFET, and  $Q_{\rm rr}$  = the reverse recovery charge of the bottom diode.

For the top MOSFET, it experiences high current and high voltage overlap during each on/off transition. But for the bottom MOSFET, its switching voltage is the bottom diode's forward drop during its on/off transition. So the switching loss for the bottom MOSFET is negligible. Its total power loss can be determined by:

$$P_{\text{BOT\_TOTAL}} = I^2_{\text{BOT\_RMS}} \cdot R_{\text{BOT\_ON}} + Q_{\text{GB}} \cdot V_{\text{GATE}} \cdot f_s + I_{\text{D\_AVG}} \cdot V_{\text{F}}$$

### Where:

$Q_{\rm GB}$  = the total gate charge of the bottom MOSFET and  $V_{\rm E}$  = the forward voltage drop of the bottom diode.

# Applications Information - (Cont.)

For a low voltage and high output current application such as the 3.3V/1.5V@6A case, the conduction loss is often dominant and selecting low  $R_{DS(ON)}$  MOSFETs will noticeably improve the efficiency of the converter even though they give higher switching losses.

The gate charge loss portion of the top/bottom MOSFET's total power loss is derived from the SC4601. This gate charge loss is based on certain operating conditions ( $f_s$ ,  $V_{care}$  and  $I_o$ ).

The thermal estimations have to be done for both MOSFETs to make sure that their junction temperatures do not exceed their thermal ratings according to their total power losses  $P_{\text{TOTAL}}$ , ambient temperature  $T_{a}$  and their thermal resistances  $R\theta_{ia}$  as follows:

$$T_{j(max)} < T_a + \frac{P_{TOTAL}}{R_{\theta ja}}$$

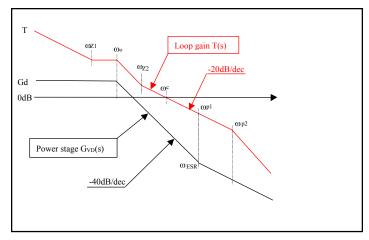

### **Loop Compensation Design:**

For a DC/DC converter, it is usually required that the converter has a loop gain of a high cross-over frequency for fast load response, high DC and low frequency gain for low steady state error, and enough phase margin for its operating stability. Often one can not have all these properties at the same time. The purpose of the loop compensation is to arrange the poles and zeros of the compensation network to meet the requirements for a specific application.

The SC4601 has an internal error amplifier and requires the compensation network to connect among the COMP pin and VSENSE pin, GND, and the output as shown in Figure 3. The compensation network includes C1, C2, R1, R7, R8 and C9. R9 is used to program the output voltage according to:

$$V_{OUT} = 0.8 \cdot (1 + \frac{R_7}{R_9})$$

Figure 3. Compensation network provides 3 poles and 2 zeros.

For voltage mode step down applications as shown in Figure 3, the power stage transfer function is:

$$G_{VD}(s) = V_{I} \frac{1 + \frac{s}{1}}{R_{C} \cdot C_{4}} + \frac{1}{1 + s \frac{L_{1}}{R} + s^{2}L_{1}C_{4}}$$

Where:

R = load resistance and

$$R_c = C_a$$

's ESR.

The compensation network will have the characteristic as follows:

$$G_{COMP}(s) = \frac{\omega_l}{s} \cdot \frac{1 + \frac{s}{\omega_{Z1}}}{1 + \frac{s}{\omega_{D2}}} \cdot \frac{1 + \frac{s}{\omega_{Z2}}}{1 + \frac{s}{\omega_{D2}}}$$

Where:

$$\omega_{1} = \frac{1}{R_{7} \cdot (C_{1} + C_{2})}$$

$$\omega_{Z1} = \frac{1}{R_{1} \cdot C_{2}}$$

$$\omega_{Z2} = \frac{1}{(R_{7} + R_{8}) \cdot C_{9}}$$

$$\omega_{P1} = \frac{C_{1} + C_{2}}{R_{1} \cdot C_{1} \cdot C_{2}}$$

# Applications Information - (Cont.)

After the compensation, the converter will have the following loop gain:

$$\begin{split} T(s) &= G_{\text{PWM}} \cdot G_{\text{COMP}}(s) \cdot G_{\text{VD}}(s) = \\ &\frac{1}{V_{\text{M}}} \cdot \omega_{\text{I}} \cdot V_{\text{I}} \cdot \frac{1 + \frac{s}{\omega_{\text{Z1}}}}{1 + \frac{s}{\omega_{\text{P2}}}} \cdot \frac{1 + \frac{s}{\omega_{\text{Z2}}}}{1 + \frac{s}{R} + s^2 LC} \end{split}$$

Where:

$G_{PWM}$  = PWM gain and

$V_{M}$  = 1.5V, ramp peak to valley voltage of SC4601.

The design guidelines for the SC4601 applications are as following:

- 1. Set the loop gain crossover corner frequency  $\omega_c$  for given switching corner frequency  $\omega_s = 2 \pi f_c$ ,

- 2. Place an integrator at the origin to increase DC and low frequency gains.

- 3. Select  $\omega_{z_1}$  and  $\omega_{z_2}$  such that they are placed near  $\omega_o$  to damp the peaking and the loop gain has a -20dB/dec rate to go across the 0dB line for obtaining a wide bandwidth.

- 4. Cancel the zero from  $C_4$ 's ESR by a compensator pole  $\omega_{P1}$  ( $\omega_{P1} = \omega_{ESR} = 1/(R_cC_4)$ ),

- 5. Place a high frequency compensator pole  $\omega p_2$  ( $\omega p_2 = \pi f_s$ ) to get the maximum attenuation of the switching ripple and high frequency noise with the adequate phase lag at  $\omega_c$ .

The compensated loop gain will be as given in Figure 4:

Figure 4. Asymptotic diagrams of power stage and its loop gain.

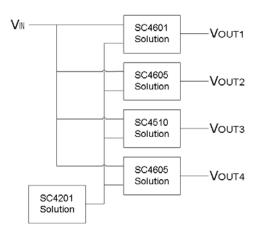

### Synchronous & Multi-phase Operation

The SC4601 has a SYNC/SLEEP pin, which can be used to synchronize the controller to a faster external clock. The SC4601 can be also used in conjunction with Semtech's multi-phase link (SC4201), to synchronize and multi-phase several controllers. Feeding outputs A/B/C/D of SC4201 to the SYNC inputs of several SC46xx controllers, it is easy to displace the controllers by 2, 3 or 4 phases. Additionally the SC4201 can be synchronized to an external clock so that everything runs under one frequency. This synchronizing operation avoids frequency beating among different controllers, simplifies noise filtering. This multi-phasing control displaces the controllers by 90°/120°/180° degrees, and simplifies tremendously the input filtering requirements for the system. Figure 5 shows one possible application.

Figure 5. Breakthrough, innovative solution to meet the next generation of networking and industrial power requirements.

# Applications Information - (Cont.)

### **Layout Guideline**

In order to achieve optimal electrical, thermal and noise performance for high frequency converters, special attention must be paid to the PCB layouts. The goal of layout optimization is to identify the high di/dt loops and minimize them. The following guideline should be used to ensure proper functions of the converters.

- 1. A ground plane is recommended to minimize noises and copper losses, and maximize heat dissipation.

- Start the PCB layout by placing the power components first. Arrange the power circuit to achieve a clean power flow route. Put all the connections on one side of the PCB with wide copper filled areas if possible.

- 3. The Vcc bypass capacitor should be placed next to the Vcc and GND pins.

- The trace connecting the feedback resistors to the output should be short, direct and far away from the noise sources such as switching node and switching components.

- Minimize the traces between PDRV/NDRV and the gates of the MOSFETs to reduce their impedance to drive the MOSFETs.

- Minimize the loop including input capacitors, top/bottom MOSFETs. This loop passes high di/dt current. Make sure the trace width is wide enough to reduce copper losses in this loop.

- 7. ISET and PHASE connections to P-MOSFET for current sensing must use Kelvin connections.

- 8. Maximize the trace width of the loop connecting the inductor, bottom MOSFET and the output capacitors.

- Connect the ground of the feedback divider and the compensation components directly to the GND pin of the SC4601 by using a separate ground trace. Then connect this pin to the ground of the output capacitor as close as possible.

# Applications Information - (Cont.)

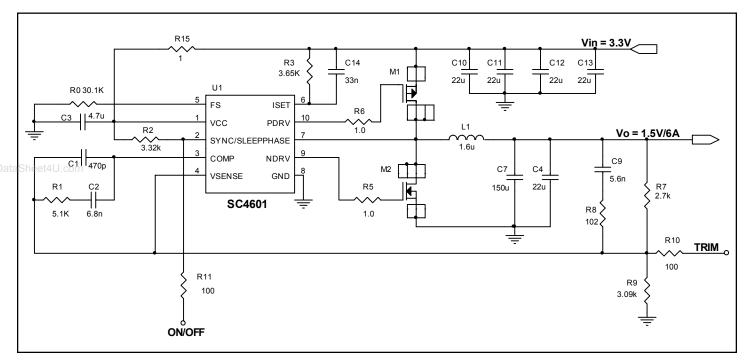

Figure 6. Schematic for 3.3V/1.5V @ 6A application

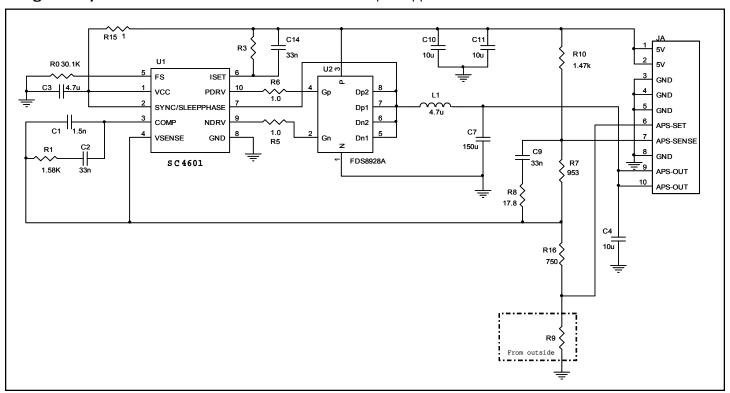

### **Design Example 2:** 5V to 0.8V ~ 1.8V @ 0.4A ~ 1.8A Xenpak application with SC4601.

Figure 7. Schematic for Xenpak application with SC4601

# Typical Characteristic (Cont.)

### Over current protection characteristic of SC4601 for 3.3V to1.5V @6A application:

The over current protection curve below is obtained by applying a gradually increased load while the load current and the output voltage are monitored and measured. When the load current is increased from 0 to 9A (over current trigger point), the output voltage is 1.5V, corresponding from Point A to Point B. As the load current increases further from 9A to 9.6A, the output voltage drops significantly from 1.5V (Point B) to 0.54V (Point C). Because an over current and a lower output voltage (0.54V < 68.75%\*1.5V = 1.03V) are present at Point C, the SC46O1 enters its HICCUP mode. Then the locus of the output current and the output voltage follows Line CD as shown in the curve. Due to the over current applied, the HICCUP protection will go back and forth on Line CD. This prevents excess power dissipation in the P-MOSFET during a short output condition.

# Bill of Materials - 3.3V to 1.5V @ 6A

| ltem             | Qty | Reference             | Value                                                       | Part No./Manufacturer            |

|------------------|-----|-----------------------|-------------------------------------------------------------|----------------------------------|

| 1                | 1   | C1                    | 470pF                                                       |                                  |

| 2                | 1   | C2                    | 6.8nF                                                       |                                  |

| 3                | 1   | C3                    | 4.7uF                                                       |                                  |

| 4                | 5   | C4,C10, C11, C12, C13 | 22uF, 1210                                                  | TDK P/N: C3225X5R0J226M          |

| 5                | 1   | C7                    | 150uF                                                       | Sanyo P/N: 6TPB150ML             |

| Sheet4U.cor<br>6 | 1   | C9                    | 5.6nF                                                       |                                  |

| 7                | 1   | C14                   | 33nF                                                        |                                  |

| 8                | 1   | L1                    | SMT power inductor,<br>1.6uH +/- 30%, 12.2Arms<br>min. Sat. | Panasonic. P/N:<br>ETQP6F1R6SFA, |

| 9                | 1   | M1                    | MOSFET P, S0-8                                              | Fairchild P/N: FDS 6375          |

| 10               | 1   | M1                    | MOSFET N, S0-8                                              | Fairchild P/N: FDS 6680A         |

| 11               | 1   | R0                    | 30.1K                                                       |                                  |

| 12               | 1   | R1                    | 5.1K                                                        |                                  |

| 13               | 1   | R2                    | 3.32K                                                       |                                  |

| 14               | 2   | R5, R6                | 1                                                           |                                  |

| 15               | 1   | R7                    | 2.7K                                                        |                                  |

| 16               | 1   | R8                    | 102                                                         |                                  |

| 17               | 1   | R9                    | 3.09K                                                       |                                  |

| 18               | 2   | R10, R11              | 100                                                         |                                  |

| 19               | 1   | R15                   | 1                                                           |                                  |

| 20               | 1   | R3                    | 3.65K                                                       |                                  |

| 21               | 1   | U1                    | SC4601                                                      | Semtech P/N: SC4601IMSTR         |

| Voy components:  |     |                       |                                                             |                                  |

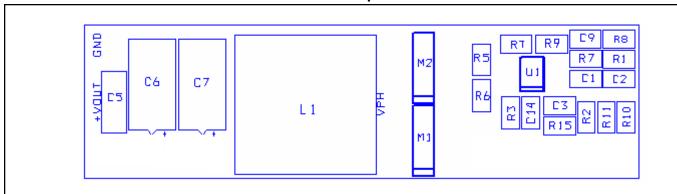

### Key components:

U1: SC4601, Semtech

M1: FDS 6375, SO-8, Fairchild M2: FDS 6680A, SO-8, Fairchild

C7: 6TPB150ML, Sanyo

L1: SMT power inductor, 1.6uH +/- 30%, 12.2Arms min. Sat, ETQP6F1R6SFA, Panasonic.

Unless specified, all resistors and capacitors are in SMD 0603 package.

Resistors are +/-1% and all capacitors are +/-20%

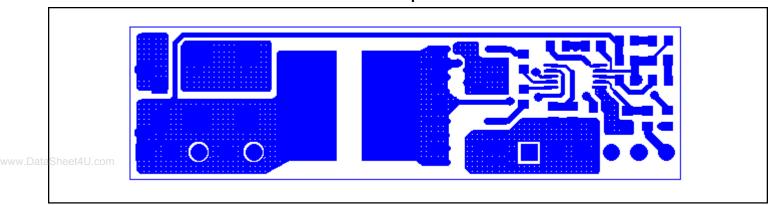

# PCB Layout - 3.3V to 1.5V @ 6A

Top

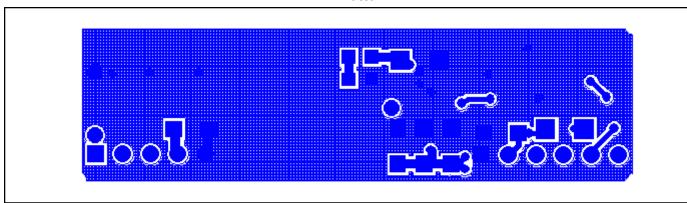

### **Bottom**

### Top

### **Bottom**

www.DataSheet4U.com

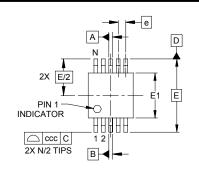

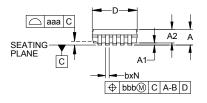

# Outline Drawing - MSOP-10

DIMENSIONS INCHES MILLIMETERS MIN NOM MAX MIN NOM MAX .043 .006 A2 .030 .037 0.75 b .007 c .003 D .114 .011 0.17

.003

.009

0.08

0.23

.114

.118

.122

2.90

3.00

3.10

.114 .122 2.90 3.00 4.90 BS L L1 N θ1 aaa 10 10 bbb .003 0.08 0.25

### NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. DATUMS -A- AND -B- TO BE DETERMINED AT DATUM PLANE -H-

- 3. DIMENSIONS "E1" AND "D" DO NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 4. REFERENCE JEDEC STD MO-187, VARIATION BA.

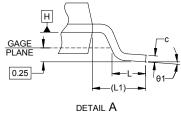

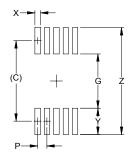

# Land Pattern - MSOP-10

| DIMENSIONS |        |             |  |  |  |

|------------|--------|-------------|--|--|--|

| DIM        | INCHES | MILLIMETERS |  |  |  |

| С          | (.161) | (4.10)      |  |  |  |

| Ŋ          | .098   | 2.50        |  |  |  |

| Р          | .020   | 0.50        |  |  |  |

| Χ          | .011   | 0.30        |  |  |  |

| Υ          | .063   | 1.60        |  |  |  |

| Z          | .224   | 5.70        |  |  |  |

### NOTES

THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY.

CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR

COMPANY'S MANUFACTURING GUIDELINES ARE MET.

# Contact Information

Semtech Corporation

Power Management Products Division

200 Flynn Road, Camarillo, CA 93012

Phone: (805)498-2111 FAX (805)498-3804