synchronous logic attributes name: 8-bit micropregram Controller seguences A High-Performance 8-Bit Slice Microprogram Sequencer

ADVANCED INFORMATION

1001 dummy 5262 000015

#### **DISTINCTIVE CHARACTERISTICS**

- Expandable

- 8-bit Slice, cascadable up to 16-bits

- Deep stack

- A 33 deep on-chip stack is used for subroutine linkage, interrupt handling and loop control.

- Hold feature

- A hold pin facilitates multiple sequencer implementations

- Interruptible at the microprogram level Two kinds of interrupts: maskable and unmaskable.

- Powerful loop control

When cascaded, two counters can act as a single 16-bit counter or two independent 8-bit counters.

Powerful addressing modes Features direct, multiway, multiway relative and program counter relative addressing.

## **GENERAL DESCRIPTION**

The Am29112 is a high performance interruptible microprogram sequencer intended for use in very high speed microprogrammed machines and optimized for the new state-of-the-art ALU's and other processing components.

The Am29112 is designed to operate in 10MHz microprogrammed systems.

It has an instruction set featuring relative and multiway branching, a rich variety of looping constructs, and provision for loading and unloading the on-chip stack.

Interrupts are accepted at the microcycle level and serviced in a manner completely transparent to the interrupted microcode.

#### APPLICATION NOTES REFERENCE

- Microprogrammed CPU using Am29116

- An intelligent fast disk controller

- Am29116 architecture speeds pixel manipulation in interactive bit-mapped graphics

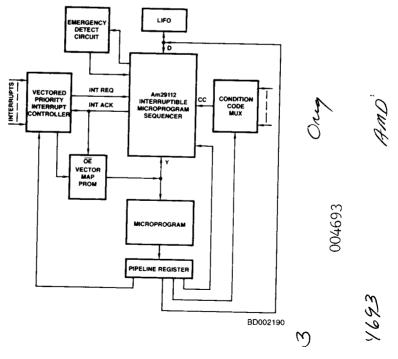

#### **BLOCK DIAGRAM**

Figure 1. Am29112 in a Single Pipelined System.

January 1985

# **RELATED PRODUCTS**

| Part No.            | Description                              |  |  |  |

|---------------------|------------------------------------------|--|--|--|

| Am29116             | A 16-Bit Bipolar Microprocessor          |  |  |  |

| Am2904              | Status and Shift Control Unit            |  |  |  |

| Am2910A             | Microprogram Controller                  |  |  |  |

| Am29114             | Vectored Priority Interrupt Controller   |  |  |  |

| Am2925              | System Clock Generator and Driver        |  |  |  |

| Am2940              | DMA Address Generator                    |  |  |  |

| Am2942              | Programmable Timer/Counter/DMA           |  |  |  |

| Am2950/<br>51/52/53 | 8-Bit Bidirectional I/O Port             |  |  |  |

| Am29118             | 8-Bit Bidirectional I/O Port/Accumulator |  |  |  |

# PIN DESCRIPTION

| Pin No.                                                                                                                  | Name                           | 1/0                                                                                                                                         | Description                                                                                                                                                                        |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                                                          | D <sub>0</sub> -D <sub>7</sub> | 1/0                                                                                                                                         | Bidirectional data input for direct input to address multiplexer, counter and other control registers and stack output.                                                            |  |  |  |  |

|                                                                                                                          | Y <sub>0</sub> -Y <sub>7</sub> | 1/0                                                                                                                                         | Bidirectional microprogram address bus outputs microprogram address and inputs interrupt vector.                                                                                   |  |  |  |  |

|                                                                                                                          | M <sub>0</sub> -M <sub>3</sub> | 1                                                                                                                                           | Multiway input pins for up to 16-way branches.                                                                                                                                     |  |  |  |  |

|                                                                                                                          | HOLD                           | 1                                                                                                                                           | When this signal is high, the Y bus is three-stated and the carry-in to the program counter incrementer is forced low. Also, the CMUX output is selected at the incrementer input. |  |  |  |  |

|                                                                                                                          | CC                             | 1                                                                                                                                           | Test input for the sequencer. (See Table 2.)                                                                                                                                       |  |  |  |  |

|                                                                                                                          | CCEN                           | 1                                                                                                                                           | Test enable for the sequencer. (See Table 2.)                                                                                                                                      |  |  |  |  |

|                                                                                                                          | POL                            | 1                                                                                                                                           | Polarity input for test. (See Table 2.)                                                                                                                                            |  |  |  |  |

|                                                                                                                          | 10-14                          | 1                                                                                                                                           | Instruction input.                                                                                                                                                                 |  |  |  |  |

|                                                                                                                          | 15-16                          | I                                                                                                                                           | Mode control input. Select one of three modes: normal, extended or forced continue. (See Table 1.)                                                                                 |  |  |  |  |

|                                                                                                                          | STKERR                         | 0                                                                                                                                           | Indicates stack overflow or underflow.                                                                                                                                             |  |  |  |  |

|                                                                                                                          | UINTR                          | I                                                                                                                                           | Unmaskable interrupt request input.                                                                                                                                                |  |  |  |  |

|                                                                                                                          | MINTR                          | R I Maskable interrupt request input.                                                                                                       |                                                                                                                                                                                    |  |  |  |  |

| INTD I                                                                                                                   |                                | i                                                                                                                                           | Disable for maskable interrupts.                                                                                                                                                   |  |  |  |  |

|                                                                                                                          |                                | 0                                                                                                                                           | Maskable interrupt acknowledge.                                                                                                                                                    |  |  |  |  |

|                                                                                                                          | LSS                            |                                                                                                                                             | Programs the least significant chip when high, most significant chip when low.                                                                                                     |  |  |  |  |

| RST I Reset input. Selects zero as the next microprogram address, resets the stack pointer and intermaskable interrupts. |                                | Reset input. Selects zero as the next microprogram address, resets the stack pointer and interrupt logic, and disables maskable interrupts. |                                                                                                                                                                                    |  |  |  |  |

|                                                                                                                          | СР                             | 1                                                                                                                                           | Clock input.                                                                                                                                                                       |  |  |  |  |

|                                                                                                                          | ACIO                           | 1/0                                                                                                                                         | Bidirectional adder I/O line for cascaded Am29112s.                                                                                                                                |  |  |  |  |

|                                                                                                                          | PCIO                           | 1/0                                                                                                                                         | Bidirectional program counter I/O line for cascaded Am29112s.                                                                                                                      |  |  |  |  |

|                                                                                                                          | CIO                            | 1/0                                                                                                                                         | Bidirectional counter I/O line for cascaded Am29112s.                                                                                                                              |  |  |  |  |

| ,                                                                                                                        | CZIO                           | 1/0                                                                                                                                         | Bidirectional counter zero I/O line for cascaded Am29112s.                                                                                                                         |  |  |  |  |

#### PRODUCT OVERVIEW

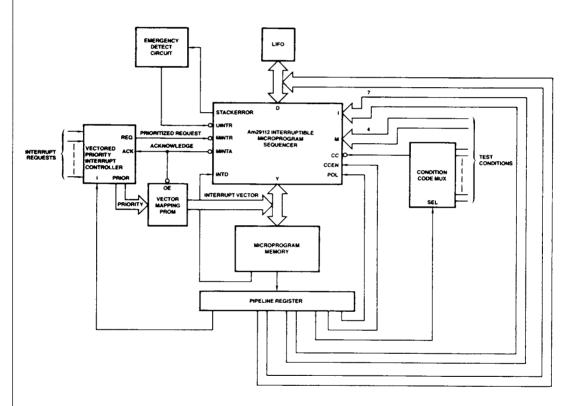

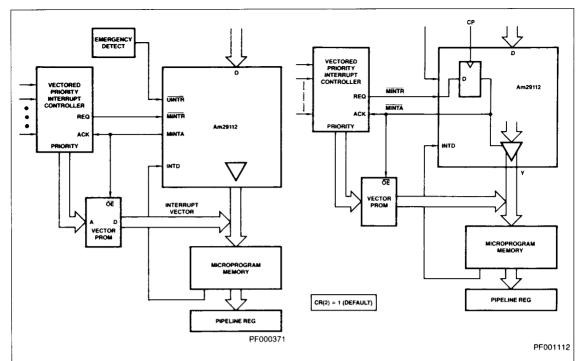

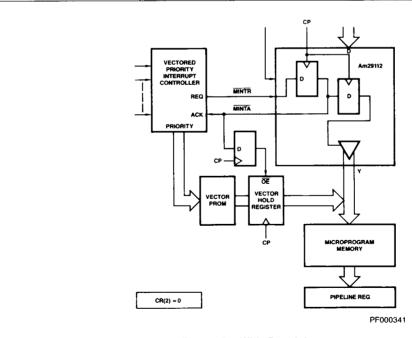

The Am29112 is designed for use in single-level pipelined systems. A typical configuration is shown in Figure 2.

Branch addresses, constants for the various registers, and stack pointer values are supplied to the Am29112 through the D port which is bidirectional to allow the stack to be unloaded onto an external LIFO. The next address generated by the sequencer is output on the Y port and directly drives the microprogram memory. A single register at the output of the microprogram memory contains the microinstruction being executed, while the next is being fetched. External conditions are applied to the  $\overline{\rm CC}$  input of the Am29112 via the condition code MUX and also to the multiway inputs.

A vectored priority interrupt controller generates a prioritized interrupt request (MINTR) to the Am29112, which acknowl-

edges the request via the MINTA pin. Upon receiving the acknowledge, the priority interrupt control puts out the encoded priority of the interrupt, which is translated to a vector by the vector mapping PROM. The MINTA output of the Am29112 turns on the PROM output and simultaneously turns off the Y port, enabling the interrupt vector onto the microprogram address bus. In the Am29112, internal states are automatically saved on the stack while the interrupt vector is transmitted through the Y port and incremented to form the next microprogram address.

The emergency detect circuit generates an unmaskable interrupt request upon power failure or stack error. On receiving an unmaskable interrupt, the sequencer branches to the unmaskable interrupt routine; the address of this routine is stored on the Am29112 in the INTVECT register. Detailed interrupt handling is discussed in a later section.

BD001921

Figure 2. Control Path in a Single Pipelined System Using the Am29112.

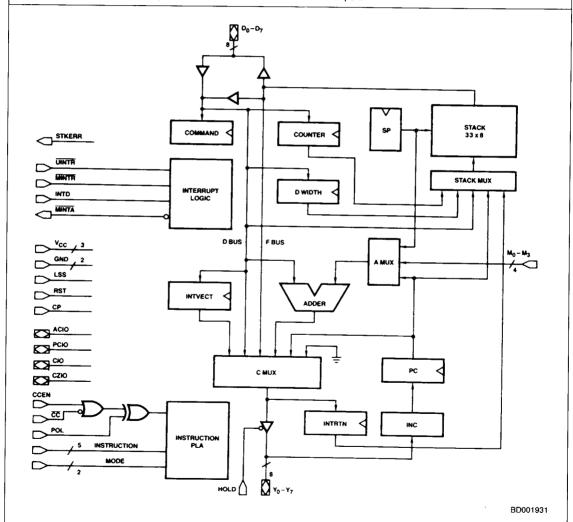

## ARCHITECTURE OF THE Am29112

The internal organization of the Am29112 is shown in Figure 3. The most important control loop inside the sequencer consists of the CMUX, incrementer, and PC register. The CMUX selects the next microprogram address based on the instruction and condition code inputs. The next microprogram address is selected from the PC register for a continue, the D port for a branch, the adder for relative and multiway branches, the interrupt register for unmaskable interrupts, the stack for subroutine returns or loop repeats, or all zeros for the JUMP ZERO instruction.

The Am29112 has many registers other than the PC register and the interrupt register. There is an 8-bit counter used for loop control; the DWIDTH register is a 4-bit register which programs the number of least significant bits of the D port that are added to the PC in relative addressing modes; the stack pointer is a 6-bit counter/register that points to the top of stack element; the 3-bit command register is used to program the chip on power-up for compatibility with the external hardware

configuration; finally, there is the INTRTN register which is used for saving the CMUX output on the stack when an interrupt occurs.

With the exception of the INTRTN register and the stack pointer, each of the above registers can be loaded directly from the D port of the Am29112.

The Am29112 features a high speed adder with full carry lookahead across 8-bits. The adder is used for PC relative addressing (branch address is PC + D), multiway relative addressing (branch address is D + M, where M is the 4-bit multiway input), and for testing the stack pointer against the D bus. In cascaded configurations, carry ripples from the LSS adder to the MSS adder over the CIO line.

The on-chip stack is 33 deep, and the Am29112 has instructions to save the D inputs, counter, multiway register, and PC-register on the stack. The stack output bus is connected via three-state buffers to the D port. It is possible to pop the stack to the D port.

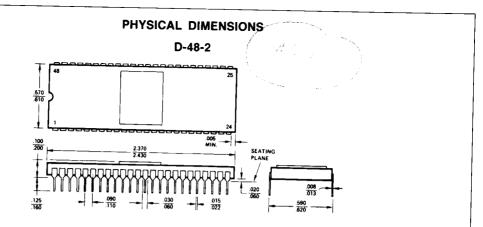

Figure 3. Am29112 48-Pin Package.

# INSTRUCTION SET OF THE Am29112 MODE BITS (I6 5)

The Am29112 is controlled by 5 instruction inputs, two mode inputs, and the condition code. In typical applications it is expected that the instruction inputs are driven directly from the pipeline, whereas the mode inputs are either permanently wired high or low to select the desired operating mode, or driven indirectly via external logic. (In some applications it might be justifiable to drive the mode bits directly from the pipeline.) The two mode bits select among three operating modes: normal (00), extended (01) and forced continue (10 and 11). In the normal mode, the entire instruction set of the Am29112 applies.

TABLE 1. MODE CONTROLS

| 16,5 | Mode     | Description                                                            |  |  |

|------|----------|------------------------------------------------------------------------|--|--|

| 00   | Normal   | For cascaded Am29112s, two independent 8-bit counters                  |  |  |

| 01   | Extended | For cascaded Am29112s, one 16-bit counter                              |  |  |

| 10   | Forced   | The Am29112 executes a continue instruction regardless of instruction, |  |  |

| 11   | Continue | condition code, and multiway inputs.                                   |  |  |

#### **EXTENDED MODE**

The instruction set includes instructions that differentiate between upper and lower counters (when there are two cascaded Am29112s). In the normal mode, the two counters on cascaded Am29112s function independently, and it is possible to set up a doubly nested loop without having to save and restore counter values on the stack. In the extended mode, however, the counters on cascaded Am29112s behave like one 16-bit counter and instructions that differentiate between the counters degenerate into identical instructions. Hence in a system with only one Am29112 there is no use for the extended mode.

#### FORCED CONTINUE MODE

In the forced continue mode the Am29112 executes a continue in every cycle regardless of the instruction bits, condition code, and multiway inputs. The simplest application (if mode bits are driven directly from the pipeline) is to use forced continue for straight-line segments of code thereby permitting most of the sequencer control fields of the pipeline to be shared. The forced continue also has an important application in systems with a writeable control store where it is

necessary to step through the addresses sequentially while loading the WCS.

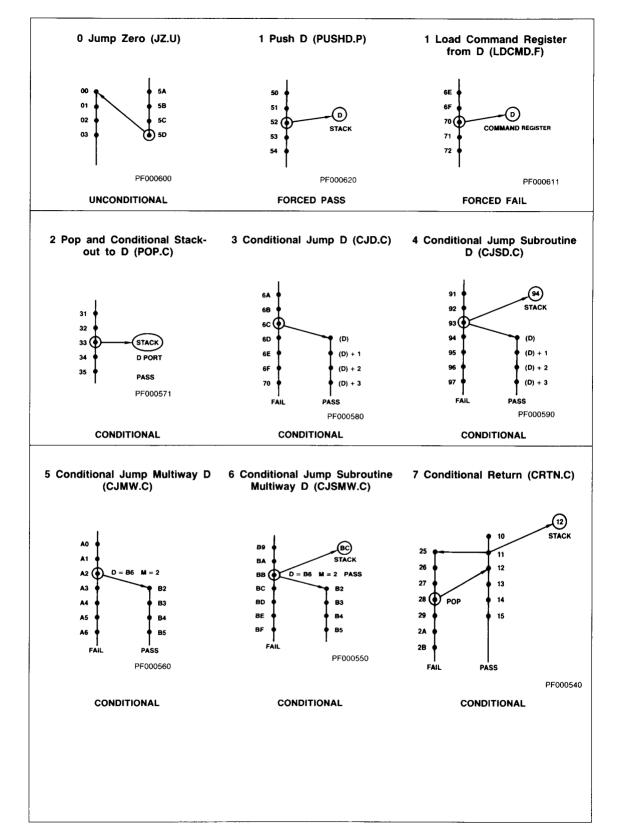

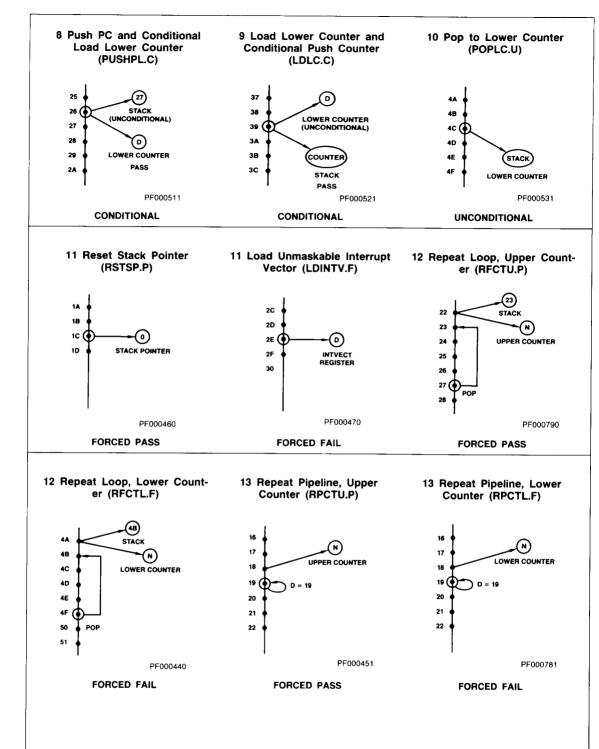

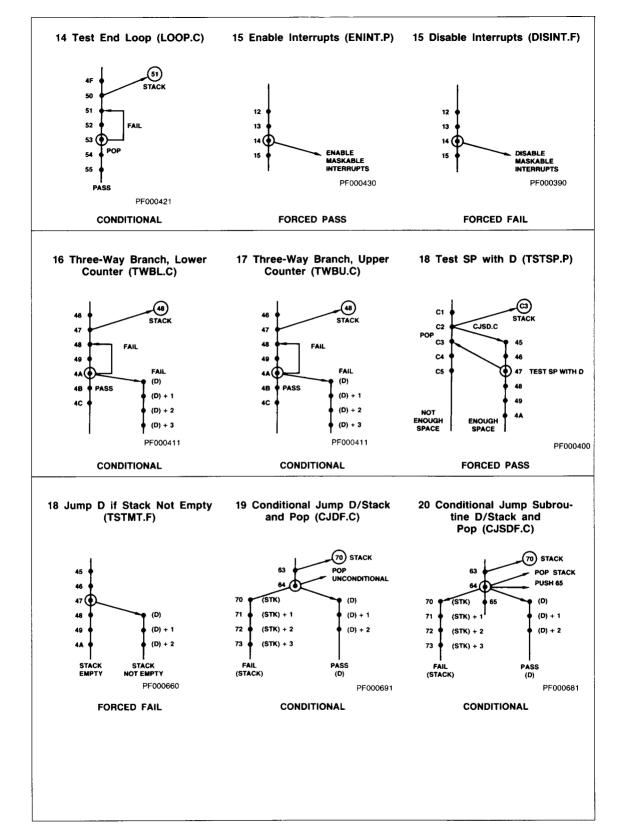

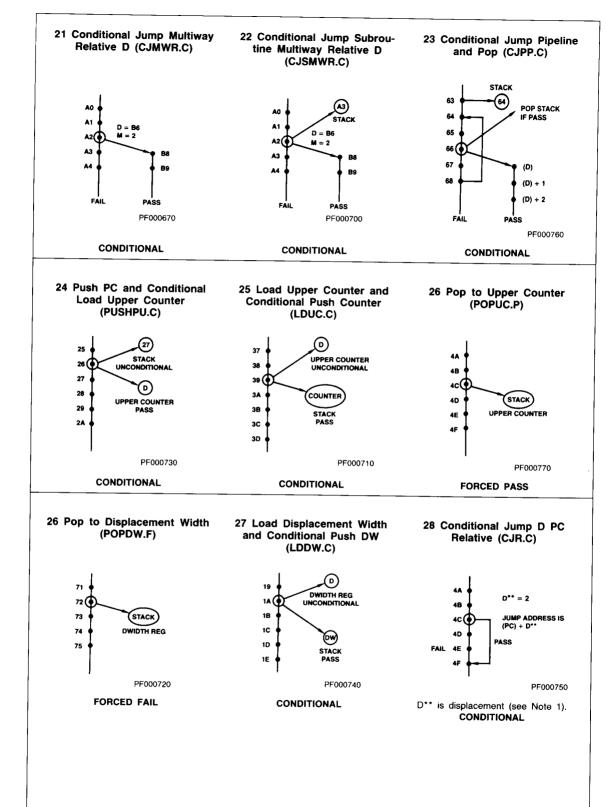

The instructions of the Am29112 are classified into four groups:

- Branching and subroutine linkage

- Looping

- Stack and register

- Interrupt

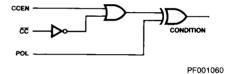

The sequencer has an instruction repertoire of altogether 40 different instructions. In order to encode these instructions with only 5 instruction lines, the condition code is used in some cases to differentiate between two distinct instructions sharing the same opcode. This way of encoding is used for the stack and register, and interrupt groups of instructions. For these instructions, therefore, the condition code multiplexer is not used to select an external condition. However it is required to force the condition code to unconditional Pass or Fail. The condition code enable and polarity logic has been designed with this in mind. Using the enable and polarity, it is possible to generate both unconditional Pass and unconditional Fail (regardless of the condition code input). Hence the condition code for these instructions is like a sixth instruction line, and the condition code multiplexer field of the pipeline can be shared for these instructions (see Figure 4 and Table 2).

Figure 4. Condition Code Circuit.

TABLE 2. CONDITION CODE TABLE

| СС  | EN | CC | POL | Condition |

|-----|----|----|-----|-----------|

|     | )  | 0  | 0   | PASS      |

| (   | )  | 1  | 0   | FAIL      |

| (   | )  | 0  | 1   | FAIL      |

| (   | )  | 1  | 1   | PASS      |

| 1 1 | 1  | 0  | 0   | PASS      |

| 1   | 1  | 1  | 0   | PASS      |

| 1 1 | 1  | 0  | 1   | FAIL      |

|     | 1  | 1  | 1   | FAIL      |

| Opcode (I40)         Condition         Mnemonic         Description           0         X         J2.U         UNCONDITIONAL JUMP ZERO           1         PASS         PUSH D, P         PUSH D, P           1         FAIL         LDCMDF         LOAD COMMAND REGISTER FROM D (FAIL)           2         COND         COND         CODE           3         COND         CJD.C         CONDITIONAL JUMP SUBROUTINE D           5         COND         CJMW.C         CONDITIONAL JUMP SUBROUTINE D           6         COND         CJSMW.C         CONDITIONAL JUMP SUBROUTINE MULTIWAY D           7         COND         CATN.C         CONDITIONAL JUMP SUBROUTINE MULTIWAY D           8         COND         COND         CONDITIONAL JUMP SUBROUTINE MULTIWAY D           9         COND         CONDITIONAL JUMP SUBROUTINE MULTIWAY D           10         COND         CONDITIONAL JUMP SUBROUTINE MULTIWAY D           11         COND         CATN.C         CONDITIONAL JUMP SUBROUTINE MULTIWAY D           12         COND         COND         CONDITIONAL JUMP SUBROUTINE MULTIWAY D           11         COND         COND         CONDITIONAL JUMP SUBROUTINE MULTIWAY D           12         COND         LDCL         CONDITIONAL JUMP SUB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Am29112 Instruction Set             |      |          |                                        |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------|----------|----------------------------------------|--|--|

| PASS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Opcode (I <sub>40</sub> ) Condition |      | Mnemonic | Description                            |  |  |

| FAIL   LDCMD.F   LOAD COMMAND REGISTER FROM D (FAIL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                   | X    | JZ.U     | UNCONDITIONAL JUMP ZERO                |  |  |

| 2 COND POP.C POP. CONDITIONAL STACKOUT TO D 3 COND CJD.C CONDITIONAL JUMP D 4 COND CJS.C CONDITIONAL JUMP SUBROUTINE D 5 COND CJSMW.C CONDITIONAL JUMP MULTIWAY D 6 COND CJSMW.C CONDITIONAL JUMP SUBROUTINE MULTIWAY D 7 COND CRTN.C CONDITIONAL BETURN 8 COND PUSHPL.C PUSH PC; COND LOAD LOWER COUNTER 9 COND LDLC.C LOAD LOWER COUNTER 10 X POPLC.U POP TO LOWER COUNTER 11 PASS RSTSP.P RESET STACK POINTER (PASS) 11 FAIL LDINTY.F LOAD UNMASKABLE INTERRUPT VECTOR (FAIL) 12 PASS RFCTU.P REPEAT LOOP, LOWER COUNTER = 0 (PASS) 12 FAIL RFCTL.F REPEAT PIPELINE, UPPER COUNTER = 0 (FAIL) 13 PASS RPCTU.P REPEAT PIPELINE, UPPER COUNTER = 0 (FAIL) 13 PASS ENINT.P ENABLE INTERRUPTS (PASS) 15 PASS ENINT.P ENABLE INTERRUPTS (PASS) 16 PASS ENINT.P ENABLE INTERRUPTS (PASS) 16 PASS ENINT.P ENABLE INTERRUPTS (PASS) 17 FAIL DISINT.F LOAD UNDER COUNTER = 0 (FAIL) 18 PASS TSTSP.P TEST END LOOP 16 PASS ENIT.P ENABLE INTERRUPTS (PASS) 17 FAIL DISINT.F LOAD UNDER COUNTER TO (FAIL) 18 PASS TSTSP.P TEST SP WITH D (PASS) 19 COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17 COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 18 PASS TSTSP.P TEST SP WITH D (PASS) 19 COND CJSD.C COND JUMP SUBROUTINE DISTACK AND POP 20 COND CJSD.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 21 COND CJSWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 22 COND CJSWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJSWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 24 COND PUSHPU.C PUSH PC; COND LOAD UPPER COUNTER 25 COND LDUC.C LOAD UPPER COUNTER (PASS) 26 FAIL POPDW.F POP TO DISPLACEMENT WIDTH (FAIL) 27 COND CJRN.C COND JUMP D PC REL NEGATIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                   | PASS | PUSHD.P  | PUSH D (PASS)                          |  |  |

| COND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                   | FAIL | LDCMD.F  |                                        |  |  |

| GOND COND CUBC. CONDITIONAL JUMP DUBROUTINE D COND COND COMW.C CONDITIONAL JUMP MULTIWAY D COND COND COND COND COND COND COND CON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                   | COND | POP.C    |                                        |  |  |

| COND CJMW.C CONDITIONAL JUMP MULTIWAY D COND CJSMW.C CONDITIONAL JUMP SUBROUTINE MULTIWAY D COND CATIN.C CONDITIONAL AUMP SUBROUTINE MULTIWAY D COND PUSHPL.C PUSH PC; COND LOAD LOWER COUNTER COND LOLC.C LOAD LOWER COUNTER; COND PUSH COUNTER DO COND LOLC.C LOAD LOWER COUNTER; COND PUSH COUNTER TO X POPLC.U POP TO LOWER COUNTER; COND PUSH COUNTER THE PASS RSTSP.P PESST STACK POINTER (PASS) THE PASS RECTU.P REPEAT LOOP, LOWER COUNTER = 0 (PASS) THE PASS RPCTU.P REPEAT LOOP, LOWER COUNTER = 0 (PASS) THE PASS RPCTU.P REPEAT LOOP, LOWER COUNTER = 0 (PASS) THE PASS RESTER PORTULE TO THE PASS PASS ENINT.P ENABLE INTERRUPTS (PASS) THE PASS ENINT.P DISABLE INTERRUPTS (PASS) THE E-WAY BRANCH, LOPER COUNTER TEST SP WITH D (PASS) THE E-WAY BRANCH, LOPER COUNTER TEST SP WITH D (PASS) THE TOWN DO THE TEST SP WITH D (PASS) THE TOWN DO THE TEST SP WITH D (PASS) THE TOWN DO THE TEST SP WITH D (PASS) THE TOWN DO THE TEST SP WITH D (PASS) TOWN DO THE TEST STACK AND POP TOWN DO THE TEST SP WITH D (PASS) TOWN D | 3                                   | COND | CJD.C    |                                        |  |  |

| 6 COND CJSMW.C CONDITIONAL JUMP SUBROUTINE MULTIWAY D 7 COND CRTN.C CONDITIONAL RETURN PUSHPL.C PUSH PC; COND LOAD LOWER COUNTER 8 COND LOLC.C LOAD LOWER COUNTER 9 COND LOLC.C LOAD LOWER COUNTER; COND PUSH COUNTER 10 X POPLC.U POP TO LOWER COUNTER; COND PUSH COUNTER 11 PASS RSTSP.P RESET STACK POINTER (PASS) 11 FAIL LDINTV.F LOAD UNMASKABLE INTERRUPT VECTOR (FAIL) 12* PASS RFCTU.P REPEAT LOOP, LOWER COUNTER = 0 (PASS) 12* FAIL RFCTL.F REPEAT LOOP, LOWER COUNTER = 0 (FAIL) 13** PASS RPCTU.P REPEAT PIPELINE, LOWER COUNTER = 0 (FAIL) 13** FAIL RPCTL.F REPEAT PIPELINE, LOWER COUNTER = 0 (FAIL) 14 COND LOOP.C TEST END LOOP 15 PASS ENINT.P ENABLE INTERRUPTS (FAIL) 16*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBL.C THREE-WAY BRANCH, UPPER COUNTER 18 PASS TSTSP.P TEST SP WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJSDF.C COND JUMP SUBROUTINE D/STACK AND POP 20 COND CJSDF.C COND JUMP SUBROUTINE D/STACK AND POP 21 COND CJSWR.C COND JUMP MULTIWAY RELATIVE D 22 COND CJSWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJSWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 24 COND CJSWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 25 COND CJSWR.C COND JUMP PIPELINE AND POP 26 PASS POPUC.P POP TO DISPLACEMENT WIDTH; COND PUSH COUNTER 26 PASS POPUC.P POP TO DISPLACEMENT WIDTH; COND PUSH DW 28 COND CJR.C COND JUMP D PC REL 29 COND JUMP D PC REL 29 COND CJRN.C COND JUMP D PC REL 29 COND JUMP D PC REL 29 COND JUMP D PC REL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4                                   | COND | CJSD.C   |                                        |  |  |

| 7 COND CRTN.C CONDITIONAL RETURN 8 COND PUSHPL.C PUSH PC; COND LOAD LOWER COUNTER 9 COND LDLC.C LOAD LOWER COUNTER; COND PUSH COUNTER 10 X POPLC.U POP TO LOWER COUNTER; COND PUSH COUNTER 11 PASS RSTSP.P RESET STACK POINTER (PASS) 11 FAIL LDINTV.F LOAD UNMASKABLE INTERRUPT VECTOR (FAIL) 12 PASS RFCTU.P REPEAT LOOP, LOWER COUNTER = 0 (PASS) 12 FAIL RPCTL.F REPEAT LOOP, LOWER COUNTER = 0 (PASS) 13 PASS RPCTU.P REPEAT PIPELINE, UPPER COUNTER = 0 (FAIL) 14 COND LOOP.C TEST END LOOP 15 PASS ENINT.P ENABLE INTERRUPTS (PASS) 15 FAIL DISINT.F DISABLE INTERRUPTS (PASS) 16 FAIL DISINT.F DISABLE INTERRUPTS (PASS) 16 FAIL TSTMT.F DISABLE INTERRUPTS (PASS) 18 FAIL TSTMT.F JUMP DIF STACK NOT EMPTY 19 COND CJDF.C COND JUMP POSTACK AND POP 20 COND CJDF.C COND JUMP SUBROUTINE DISTACK AND POP 21 COND CJDF.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 22 COND CJPP.C COND JUMP PIPELINE AND POP 24 COND PUSHPU.C PUSH PC; COND LOAD UPPER COUNTER 25 COND LDUC.C LOAD UPPER COUNTER 26 PASS POPUC.P POP TO DISPLACEMENT WIDTH; COND PUSH DW 28 COND CJR.C COND JUMP PIPELINE AND POP 29 TO DISPLACEMENT WIDTH; COND PUSH DW 29 COND CJR.C COND JUMP D POR REL NEGATIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5                                   | COND | CJMW.C   | CONDITIONAL JUMP MULTIWAY D            |  |  |

| 7 COND CRTN.C CONDITIONAL RETURN PUSH P.C. COND LOAD LOWER COUNTER COND LOCAL LOWER COUNTER COND LOAD LOWER COUNTER COND LOAD LOWER COUNTER COND PUSH COUNTER DOP TO LOWER COUNTER COND PUSH COUNTER POP TO LOWER COUNTER COND PUSH COUNTER POP TO LOWER COUNTER COND PUSH COUNTER COND PUSH COUNTER COND PUSH COUNTER COND PUSH COUNTER COUNTER COND PUSH COUNTER COU | 6                                   | COND | CJSMW.C  | CONDITIONAL JUMP SUBROUTINE MULTIWAY D |  |  |

| 8 COND PUSHPL.C LDLC.C LOAD LOWER COUNTER 9 COND LDLC.C LOAD LOWER COUNTER; COND PUSH COUNTER 10 X POPLC.U POP TO LOWER COUNTER 11 PASS RSTSP.P RESET STACK POINTER (PASS) 11 FAIL LDINTV.F LOAD UNMASKABLE INTERRUPT VECTOR (FAIL) 12* PASS RFCTU.P REPEAT LOOP, UPPER COUNTER = 0 (PASS) 12* FAIL RFCTL.F REPEAT LOOP, LOWER COUNTER = 0 (PASS) 13** FAIL RPCTL.F REPEAT PIPELINE, UPPER COUNTER = 0 (FAIL) 14 COND LOOP.C TEST END LOOP 15 PASS ENINT.P ENABLE INTERRUPTS (FAIL) 16*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBL.C THREE-WAY BRANCH, UPPER COUNTER 18 PASS TSTSP.P TEST SY WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJSDF.C COND JUMP DISTACK AND POP 20 COND CJSDF.C COND JUMP SUBROUTINE DISTACK AND POP 21 COND CJSDF.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 22 COND CJSMWR.C COND JUMP PRECOUNTER 24 COND CJSP.C COND JUMP PIPELINE AND POP 25 COND CJSP.C COND JUMP PIPELINE AND POP 26 PASS POPUC.P POP TO UPPER COUNTER 27 COND LDDW.C LOAD USPPER COUNTER (PASS) 28 COND CJR.C COND JUMP DO PCREL NEGATIVE 29 COND JUMP D PC REL NEGATIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                   | COND | CRTN.C   |                                        |  |  |

| 9 COND X POPUC.U POP TO LOWER COUNTER; COND PUSH COUNTER 10 X POPUC.U POP TO LOWER COUNTER; COND PUSH COUNTER 11 PASS RSTSP.P RESET STACK POINTER (PASS) 11 FAIL LDINTV.F LOAD UNMASKABLE INTERRUPT VECTOR (FAIL) 12* PASS RFCTU.P REPEAT LOOP, UPPER COUNTER = 0 (PASS) 12* FAIL RFCTL.F REPEAT LOOP, LOWER COUNTER = 0 (FAIL) 13** PASS RPCTU.P REPEAT PIPELINE, LOWER COUNTER = 0 (FAIL) 14* COND LOOP.C TEST END LOOP 15 PASS ENINT.P ENABLE INTERRUPTS (PASS) 15* FAIL DISINT.F DISABLE INTERRUPTS (FAIL) 16*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBL.C THREE-WAY BRANCH, UPPER COUNTER 18* PASS TSTSP.P TEST SP WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJSDF.C COND JUMP D/STACK AND POP 20 COND CJSDF.C COND JUMP MULTIWAY RELATIVE D 22 COND CJSMWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJSMWR.C COND JUMP PIPELINE AND POP 24 COND PUSHPU.C PUSH PC; COND UPPER COUNTER 25 COND LDUC.C LOAD UPPER COUNTER; COND PUSH COUNTER 26 PASS POPUC.P POP TO UPPER COUNTER; COND PUSH COUNTER 27 COND LDDW.C LOAD UPPER COUNTER; COND PUSH DW 28 COND CJRN.C COND JUMP D PC REL 29 COND LJRN.C COND JUMP D PC REL NEGATIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8                                   | COND |          |                                        |  |  |

| 10 X POPLC.U POP TO LOWER COUNTER 11 PASS RSTSP.P RESET STACK POINTER (PASS) 11 FAIL LDINTV.F LOAD UNMASKABLE INTERRUPT VECTOR (FAIL) 12* PASS RFCTU.P REPEAT LOOP, UPPER COUNTER = 0 (PASS) 12* FAIL RFCTL.F REPEAT LOOP, LOWER COUNTER = 0 (FAIL) 13** PASS RPCTU.P REPEAT PIPELINE, UPPER COUNTER = 0 (FAIL) 13** FAIL RPCTL.F REPEAT PIPELINE, UPPER COUNTER = 0 (FAIL) 14 COND LOOP.C TEST END LOOP 15 PASS ENINT.P ENABLE INTERRUPTS (PASS) 15* FAIL DISINT.F DISABLE INTERRUPTS (FAIL) 16*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBL.C THREE-WAY BRANCH, UPPER COUNTER 18 PASS TSTSP.P TEST SP WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJSDF.C COND JUMP DISTACK AND POP 20 COND CJSDF.C COND JUMP SUBROUTINE DISTACK AND POP 21 COND CJSWR.C COND JUMP MULTIWAY RELATIVE D 22 COND CJSWR.C COND JUMP PUBLINE AND POP 24 COND PUSHPU.C PUSH PC; COND UPPER COUNTER 25 COND LDUC.C LOAD UPPER COUNTER 26 PASS POPUC.P POP TO DISPLACEMENT WIDTH (FAIL) 27 COND CJR.C COND JUMP D PC REL NEGATIVE 28 COND CJRN.C COND JUMP D PC REL NEGATIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                   | COND | LDLC.C   |                                        |  |  |

| 11 PASS RSTSP.P RESET STACK POINTER (PASS) 11 FAIL LDINTV.F LOAD UNMASKABLE INTERRUPT VECTOR (FAIL) 12* PASS RFCTU.P REPEAT LOOP, UPPER COUNTER = 0 (PASS) 12* FAIL RFCTL.F REPEAT LOOP, LOWER COUNTER = 0 (FAIL) 13** PASS RPCTU.P REPEAT PIPELINE, UPPER COUNTER = 0 (FAIL) 13** FAIL RPCTL.F REPEAT PIPELINE, LOWER COUNTER = 0 (FAIL) 14 COND LOOP.C TEST END LOOP 15 PASS ENINT.P ENABLE INTERRUPTS (PASS) 15 FAIL DISINT.F DISABLE INTERRUPTS (FAIL) 16*** COND TWBU.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBU.C THREE-WAY BRANCH, UPPER COUNTER 18 PASS TSTSP.P TEST SP WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJDF.C COND JUMP SUBROUTINE D/STACK AND POP 20 COND CJSDF.C COND JUMP SUBROUTINE D/STACK AND POP 21 COND CJMWR.C COND JUMP SUBROUTINE D/STACK AND POP 22 COND CJSWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJPP.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 24 COND PUSHPU.C PUSH PC; COND LOAD UPPER COUNTER 25 COND LDUC.C LOAD UPPER COUNTER; COND PUSH COUNTER 26 PASS POPUC.P POP TO UPPER COUNTER (PASS) 26 FAIL POPDW.F POP TO DISPLACEMENT WIDTH; COND PUSH DW 28 COND CJR.C COND JUMP D PC REL 29 COND LDDW.C COND JUMP D PC REL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10                                  | X    | POPLC.U  |                                        |  |  |

| 11 FAIL DINTV.F REPEAT LOOP, UPPER COUNTER = 0 (PASS) 12* FAIL RFCTL.F REPEAT LOOP, UPPER COUNTER = 0 (PASS) 13** PASS RPCTU.P REPEAT LOOP, UPPER COUNTER = 0 (PASS) 13** FAIL RPCTL.F REPEAT PIPELINE, UPPER COUNTER = 0 (FAIL) 14 COND LOOP.C TEST END LOOP 15 PASS ENINT.P ENABLE INTERRUPTS (PASS) 15 FAIL DISINT.F DISABLE INTERRUPTS (FAIL) 16*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBL.C THREE-WAY BRANCH, UPPER COUNTER 18 PASS TSTSP.P TEST SP WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJDF.C COND JUMP D/STACK AND POP 20 COND CJDF.C COND JUMP SUBROUTINE D/STACK AND POP 21 COND CJSWR.C COND JUMP SUBROUTINE D/STACK AND POP 22 COND CJSWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJPP.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 24 COND LDUC.C COND JUMP PIPELINE AND POP 25 COND LDUC.C LOAD UPPER COUNTER 26 PASS POPUC.P PUSH PC; COND LOAD UPPER COUNTER 26 PASS POPUC.P POP TO UPPER COUNTER; COND PUSH COUNTER 27 COND LDW.C LOAD DISPLACEMENT WIDTH (FAIL) 28 COND CJR.C COND JUMP D PC REL 29 COND JUMP D PC REL NEGATIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11                                  |      | 1        |                                        |  |  |

| 12* PASS RFCTU.P REPEAT LOOP, UPPER COUNTER = 0 (PASS) 12* FAIL RFCTL.F REPEAT LOOP, LOWER COUNTER = 0 (FAIL) 13** PASS RPCTU.P REPEAT PIPELINE, UPPER COUNTER = 0 (FAIL) 13** FAIL RPCTL.F REPEAT PIPELINE, LOWER COUNTER = 0 (FAIL) 14 COND LOOP.C TEST END LOOP 15 PASS ENINT.P ENABLE INTERRUPTS (PASS) 15 FAIL DISINT.F DISABLE INTERRUPTS (FAIL) 16*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 18 PASS TSTSP.P TEST SP WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJDF.C COND JUMP D/STACK AND POP 20 COND CJSDF.C COND JUMP SUBROUTINE D/STACK AND POP 21 COND CJMWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 22 COND CJSMWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJPP.C COND JUMP PIPELINE AND POP 24 COND PUSHPU.C PUSH PC; COND LOAD UPPER COUNTER 25 COND LDUC.C LOAD UPPER COUNTER; COND PUSH COUNTER 26 PASS POPUC.P POP TO UPPER COUNTER; COND PUSH COUNTER 26 FAIL POPDW.F POP TO DISPLACEMENT WIDTH; COND PUSH DW 28 COND CJR.C COND JUMP D PC REL 29 COND JUMP D PC REL NEGATIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                  |      |          |                                        |  |  |

| 12* FAIL RFCTL.F REPEAT LOOP, LOWER COUNTER = 0 (FAIL) 13** PASS RPCTU.P REPEAT PIPELINE, UPPER COUNTER = 0 (PASS) 13** FAIL RPCTL.F REPEAT PIPELINE, LOWER COUNTER = 0 (FAIL) 14 COND LOOP.C TEST END LOOP 15 PASS ENINT.P ENABLE INTERRUPTS (PASS) 15 FAIL DISINT.F DISABLE INTERRUPTS (FAIL) 16*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBL.C THREE-WAY BRANCH, UPPER COUNTER 18 PASS TSTSP.P TEST SP WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJDF.C COND JUMP D/STACK AND POP 20 COND CJSDF.C COND JUMP SUBROUTINE D/STACK AND POP 21 COND CJMWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 22 COND CJSMWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJPP.C COND JUMP PIPELINE AND POP 24 COND PUSHPU.C PUSH PC; COND LOAD UPPER COUNTER 25 COND LDUC.C LOAD UPPER COUNTER; COND PUSH COUNTER 26 PASS POPUC.P POP TO UPPER COUNTER; COND PUSH COUNTER 26 FAIL POPDW.F POP TO DISPLACEMENT WIDTH; COND PUSH DW 28 COND CJR.C COND JUMP D PC REL NEGATIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12*                                 |      |          |                                        |  |  |

| 13** PASS RPCTU.P REPEAT PIPELINE, UPPER COUNTER = 0 (PASS) 13** FAIL RPCTL.F REPEAT PIPELINE, LOWER COUNTER = 0 (FAIL) 14 COND LOOP.C TEST END LOOP 15 PASS ENINT.P ENABLE INTERRUPTS (PASS) 15 FAIL DISINT.F DISABLE INTERRUPTS (FAIL) 16*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBU.C THREE-WAY BRANCH, UPPER COUNTER 18 PASS TSTSP.P TEST SP WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJDF.C COND JUMP D/STACK AND POP 20 COND CJSDF.C COND JUMP SUBROUTINE D/STACK AND POP 21 COND CJSWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 22 COND CJSWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJPP.C COND JUMP PIPELINE AND POP 24 COND PUSHPU.C PUSH PC; COND LOAD UPPER COUNTER 25 COND LDUC.C LOAD UPPER COUNTER; COND PUSH COUNTER 26 PASS POPUC.P POP TO UPPER COUNTER (PASS) 26 FAIL POPDW.F POP TO DISPLACEMENT WIDTH (FAIL) 27 COND CJR.C COND JUMP D PC REL NEGATIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                     |      | -        |                                        |  |  |

| 13** FAIL COND LOOP.C TEST END LOOP 15 PASS ENINT.P ENABLE INTERRUPTS (PASS) 15 FAIL DISINT.F DISABLE INTERRUPTS (FAIL) 16*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBU.C THREE-WAY BRANCH, UPPER COUNTER 17*** 18 PASS TSTSP.P TEST SP WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJDF.C COND JUMP SUBROUTINE D/STACK AND POP 20 COND CJSWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJSWWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 24 COND CJP.C COND JUMP PIPELINE AND POP 25 COND COND PUSHPU.C PUSH PC; COND LOAD UPPER COUNTER 26 PASS POPUC.P POP TO UPPER COUNTER; COND PUSH COUNTER 26 FAIL POPDW.F POP TO DISPLACEMENT WIDTH (FAIL) 27 COND CJR.C COND JUMP D PC REL 29 COND JUMP D PC REL COND PUSH DPC COND JUMP D PC REL COND TEST END CEAL TEST END LOOP TEST END TEST |                                     |      |          |                                        |  |  |

| 14 COND LOOP.C TEST END LOOP 15 PASS ENINT.P ENABLE INTERRUPTS (PASS) 16 FAIL DISINT.F DISABLE INTERRUPTS (FAIL) 16*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBU.C THREE-WAY BRANCH, UPPER COUNTER 18 PASS TSTSP.P TEST SP WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJDF.C COND JUMP D/STACK AND POP 20 COND CJSDF.C COND JUMP SUBROUTINE D/STACK AND POP 21 COND CJMWR.C COND JUMP SUBROUTINE D/STACK AND POP 22 COND CJSWWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJP.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 24 COND PUSHPU.C COND JUMP PIPELINE AND POP 25 COND LDUC.C LOAD UPPER COUNTER 26 PASS POPUC.P PUSH PC; COND LOAD UPPER COUNTER 26 PASS POPUC.P POP TO UPPER COUNTER (PASS) 26 FAIL POPDW.F POP TO DISPLACEMENT WIDTH (FAIL) 27 COND LDDW.C LOAD DISPLACEMENT WIDTH; COND PUSH DW 28 COND CJR.C COND JUMP D PC REL NEGATIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                     |      |          |                                        |  |  |

| 15 PASS ENINT.P ENABLE INTERRUPTS (PASS) 15 FAIL DISINT.F DISABLE INTERRUPTS (FAIL) 16*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBU.C THREE-WAY BRANCH, LOWER COUNTER 18 PASS TSTSP.P TEST SP WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJDF.C COND JUMP D/STACK AND POP 20 COND CJSDF.C COND JUMP SUBROUTINE D/STACK AND POP 21 COND CJMWR.C COND JUMP MULTIWAY RELATIVE D 22 COND CJSWWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJPP.C COND JUMP PIPELINE AND POP 24 COND PUSHPU.C PUSH PC; COND LOAD UPPER COUNTER 25 COND LDUC.C LOAD UPPER COUNTER; COND PUSH COUNTER 26 PASS POPUC.P POP TO UPPER COUNTER (PASS) 26 FAIL POPDW.F POP TO DISPLACEMENT WIDTH (FAIL) 27 COND LDDW.C LOAD DISPLACEMENT WIDTH; COND PUSH DW 28 COND CJR.C COND JUMP D PC REL NEGATIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14                                  |      |          |                                        |  |  |

| 15 FAIL DISINT.F DISABLE INTERRUPTS (FAIL) 16*** COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER 17*** COND TWBU.C THREE-WAY BRANCH, LOPER COUNTER 18 PASS TSTSP.P TEST SP WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJDF.C COND JUMP D/STACK AND POP 20 COND CJSDF.C COND JUMP SUBROUTINE D/STACK AND POP 21 COND CJMWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 22 COND CJSMWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJSMWR.C COND JUMP PIPELINE AND POP 24 COND PUSHPU.C PUSH PC; COND LOAD UPPER COUNTER 25 COND LDUC.C LOAD UPPER COUNTER; COND PUSH COUNTER 26 PASS POPUC.P POP TO UPPER COUNTER (PASS) 26 FAIL POPDW.F POP TO DISPLACEMENT WIDTH; COND PUSH DW 28 COND CJR.C COND JUMP D PC REL 29 COND CJR.C COND JUMP D PC REL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                     |      |          |                                        |  |  |

| 16***  COND TWBL.C THREE-WAY BRANCH, LOWER COUNTER TOWN TWBU.C THREE-WAY BRANCH, UPPER COUNTER THREE-WAY BRANCH, UPPER COUNTER THREE-WAY BRANCH, UPPER COUNTER TEST SP WITH D (PASS) TEST SP WITH D (P |                                     |      |          |                                        |  |  |

| 17*** COND TWBU.C THREE-WAY BRANCH, UPPER COUNTER 18 PASS TSTSP.P TEST SP WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJDF.C COND JUMP D/STACK AND POP 20 COND CJSDF.C COND JUMP SUBROUTINE D/STACK AND POP 21 COND CJMWR.C COND JUMP MULTIWAY RELATIVE D 22 COND CJSWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJPP.C COND JUMP PIPELINE AND POP 24 COND PUSHPU.C PUSH PC; COND LOAD UPPER COUNTER 25 COND LDUC.C LOAD UPPER COUNTER; COND PUSH COUNTER 26 PASS POPUC.P POP TO UPPER COUNTER (PASS) 26 FAIL POPDW.F POP TO DISPLACEMENT WIDTH (FAIL) 27 COND LDDW.C LOAD DISPLACEMENT WIDTH; COND PUSH DW 28 COND CJR.C COND JUMP D PC REL NEGATIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                     |      |          |                                        |  |  |

| 18 PASS TSTSP.P TEST SP WITH D (PASS) 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJDF.C COND JUMP D/STACK AND POP 20 COND CJSMWR.C COND JUMP SUBROUTINE D/STACK AND POP 21 COND CJSWWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 22 COND CJPP.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJPP.C COND JUMP PIPELINE AND POP 24 COND PUSHPU.C PUSH PC; COND LOAD UPPER COUNTER 25 COND LDUC.C LOAD UPPER COUNTER; COND PUSH COUNTER 26 PASS POPUC.P POP TO UPPER COUNTER (PASS) 26 FAIL POPDW.F POP TO DISPLACEMENT WIDTH (FAIL) 27 COND LDDW.C LOAD DISPLACEMENT WIDTH; COND PUSH DW 28 COND CJR.C COND JUMP D PC REL 29 COND CJRN.C COND JUMP D PC REL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                     |      | 1        |                                        |  |  |

| 18 FAIL TSTMT.F JUMP D IF STACK NOT EMPTY 19 COND CJDF.C COND JUMP D/STACK AND POP 20 COND CJSDF.C COND JUMP SUBROUTINE D/STACK AND POP 21 COND CJMWR.C COND JUMP MULTIWAY RELATIVE D 22 COND CJPC. COND JUMP PIPELINE AND POP 24 COND PUSHPU.C COND JUMP PIPELINE AND POP 25 COND LDUC.C LOAD UPPER COUNTER 26 PASS POPUC.P POP TO UPPER COUNTER (PASS) 26 FAIL POPDW.F POP TO DISPLACEMENT WIDTH (FAIL) 27 COND LDDW.C LOAD DISPLACEMENT WIDTH; COND PUSH DW 28 COND CJR.C COND JUMP D PC REL 29 COND CJRN.C COND JUMP D PC REL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                     |      |          |                                        |  |  |

| 19 COND CJDF.C COND JUMP D/STACK AND POP 20 COND CJSDF.C COND JUMP SUBROUTINE D/STACK AND POP 21 COND CJMWR.C COND JUMP MULTIWAY RELATIVE D 22 COND CJSWWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D 23 COND CJPP.C COND JUMP PIPELINE AND POP 24 COND PUSHPU.C PUSH PC; COND LOAD UPPER COUNTER 25 COND LDUC.C LOAD UPPER COUNTER; COND PUSH COUNTER 26 PASS POPUC.P POP TO UPPER COUNTER (PASS) 26 FAIL POPDW.F POP TO DISPLACEMENT WIDTH (FAIL) 27 COND LDDW.C LOAD DISPLACEMENT WIDTH; COND PUSH DW 28 COND CJR.C COND JUMP D PC REL 29 COND CJRN.C COND JUMP D PC REL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                     |      | 1 - 1    | , ,                                    |  |  |

| COND CJSDF.C COND JUMP SUBROUTINE D/STACK AND POP COND CJMWR.C COND JUMP MULTIWAY RELATIVE D COND CJSMWR.C COND JUMP SUBROUTINE MULTIWAY RELATIVE D COND JUMP SUBROUTINE MULTIWAY RELATIVE D COND JUMP PIPELINE AND POP COND JUMP PIPELINE AND POP COND LDUC.C LOAD UPPER COUNTER COND LDUC.C LOAD UPPER COUNTER (PASS) POPUC.P POP TO UPPER COUNTER (PASS) FAIL POPDW.F POP TO DISPLACEMENT WIDTH (FAIL) COND LDDW.C LOAD DISPLACEMENT WIDTH; COND PUSH DW COND CJR.C COND JUMP D PC REL COND CJRN.C COND JUMP D PC REL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                     |      |          |                                        |  |  |