# Photodiode array with amplifier \$8865 series

### Photodiode array combined with signal processing circuit chip

- Large element pitch: 2 types available S8865-64: 0.8 mm pitch × 64 ch S8865-128: 0.4 mm pitch × 128 ch

- 5 V power supply operation

- Simultaneous integration by using a charge amplifier array

- Sequential readout with a shift register (Data rate: 1 MHz Max.)

- Low dark current due to zero-bias photodiode operation

- Integrated clamp circuit allows low noise and wide dynamic range

- Integrated timing generator allows operation at two different pulse timings

- Types with phosphor screen affixed on the active area are available for X-ray detection: S8865-64G/S8865-128G

#### Applications

- Long line sensors

- Line sensors for X-ray detection

#### ■ Mechanical specifications

| Parameter               | Symbol *1 | S8865-64 | S8865-128 | Unit |

|-------------------------|-----------|----------|-----------|------|

| Element pitch           | Р         | 0.8      | 0.4       | mm   |

| Element diffusion width | W         | 0.7      | 0.3       | mm   |

| Element height          | Н         | 0.8      | 0.6       | mm   |

| Number of elements      | -         | 64       | 128       | -    |

| Active area length      | -         | 51.2     | 51.2      | mm   |

<sup>\*1:</sup> Refer to following figure.

#### ■ Enlarged view of active area

KMPDC0072EA

# Photodiode array with amplifier S8865 series

#### ■ Absolute maximum ratings

| Parameter                       | Symbol    | Rated value | Unit |

|---------------------------------|-----------|-------------|------|

| Supply voltage                  | Vdd       | -0.3 to +6  | V    |

| Reference voltage               | Vref      | -0.3 to +6  | V    |

| Photodiode voltage              | Vpd       | -0.3 to +6  | V    |

| Gain selection terminal voltage | Vgain     | -0.3 to +6  | V    |

| Master/slave selection voltage  | Vms       | -0.3 to +6  | V    |

| Clock pulse voltage             | V (CLK)   | -0.3 to +6  | V    |

| Reset pulse voltage             | V (RESET) | -0.3 to +6  | V    |

| External start pulse voltage    | V (EXTST) | -0.3 to +6  | V    |

| Operating temperature *2        | Topr      | -5 to +60   | °C   |

| Storage temperature             | Tstg      | -10 to +70  | °C   |

<sup>\*2 :</sup> No condensation

#### ■ Recommended terminal voltage

| Parameter               |               | Symbol     | Min.     | Тур. | Max.     | Unit |

|-------------------------|---------------|------------|----------|------|----------|------|

| Supply voltage          |               | Vdd        | 4.75     | 5    | 5.25     | V    |

| Reference voltage       |               | Vref       | 4        | 4.5  | Vdd      | V    |

| Photodiode voltage      |               | Vpd        | -        | Vref | -        | V    |

| Gain selection terminal | High gain     | Vacin      | Vdd-0.25 | Vdd  | Vdd+0.25 | V    |

| voltage                 | Low gain      | Vgain      | 0        | -    | 0.4      | V    |

| Master/slave selection  | High level *3 | Vms        | Vdd-0.25 | Vdd  | Vdd+0.25 | V    |

| voltage                 | Low level *4  | VIIIS      | 0        | -    | 0.4      | V    |

| Clask pulse veltage     | High level    |            | Vdd-0.25 | Vdd  | Vdd+0.25 | V    |

| Clock pulse voltage     | Low level     | V (CLK)    | 0        | -    | 0.4      | V    |

| Deact mules valters     | High level    | V (DECET)  | Vdd-0.25 | Vdd  | Vdd+0.25 | V    |

| Reset pulse voltage     | Low level     | V (RESET)  | 0        | -    | 0.4      | V    |

| External start pulse    | High level    | \/ (EVECD) | Vdd-0.25 | Vdd  | Vdd+0.25 | V    |

| voltage                 | Low level     | V (EXESP)  | 0        | -    | 0.4      | V    |

<sup>\*3 :</sup> Parallel

#### ■ Electrical characteristics [Ta=25 °C, Vdd=5 V, V (CLK)=V (RESET)=5 V]

| Parameter                |           | Cymahal | S8865-64 |      | S8865-128 |      |      | Unit |       |

|--------------------------|-----------|---------|----------|------|-----------|------|------|------|-------|

|                          |           | Symbol  | Min.     | Тур. | Max.      | Min. | Тур. | Max. | Ullit |

| Clock pulse frequency *5 |           | f (CLK) | 40       | -    | 4000      | 40   | -    | 4000 | kHz   |

| Output impedance         |           | Zo      | -        | 3    | -         | •    | 3    | -    | kΩ    |

| Power consumption        |           | Р       | -        | 100  | -         | ı    | 180  | -    | mW    |

| Charge amp feedback      | High gain | gain    |          | 0.5  | -         | 1    | 0.5  | -    |       |

| capacitance              | Low gain  | Ci      | -        | 1    | -         | 1    | 1    | -    | pF    |

<sup>\* 5:</sup> Video data rate is 1/4 of clock pulse frequency f (CLK).

<sup>\*4 :</sup> Serial at 2nd or later stages

# Photodiode array with amplifier S8865 series

#### ■ Electrical/optical characteristics [Ta=25 °C, Vdd=5 V, V (CLK)=V (RESET)=5 V, Vgain=5 V (High gain), 0 V (Low gain)]

| Parameter        |                     | Currente ed | S8865-64 S8865-128 |             |      | I I to id |       |      |                  |

|------------------|---------------------|-------------|--------------------|-------------|------|-----------|-------|------|------------------|

|                  |                     | Symbol      | Min.               | Тур.        | Max. | Min.      | Тур.  | Max. | Unit             |

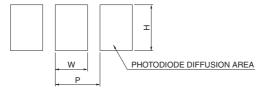

| Spectral respon  | nse range           | λ           |                    | 200 to 1000 |      |           |       |      | nm               |

| Peak sensitivity | y wavelength        | λр          | •                  | 720         | -    | -         | 720   | -    | nm               |

| Dark output      | High gain           | Vd          | ı                  | 0.02        | 0.2  | ·         | 0.01  | 0.1  |                  |

| voltage *6       | Low gain            | vu          | •                  | 0.01        | 0.1  | -         | 0.005 | 0.05 | mV               |

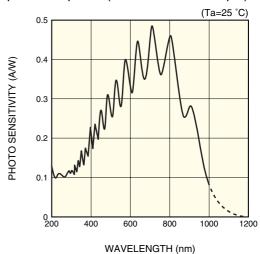

| Saturation outp  | out voltage         | Vsat        | •                  | 3.5         | -    | -         | 3.5   | -    | V                |

| Saturation       | High gain           | Esat        | •                  | 0.8         | -    | -         | 2.4   | -    | m1o              |

| exposure *7      | Low gain            | ⊏Sat        | •                  | 1.6         | -    | -         | 4.8   | -    | mlx·s            |

| Photo            | High gain           | S           | -                  | 4400        | -    | -         | 1500  | -    | V/ <i>lx</i> ⋅ s |

| sensitivity      | Low gain            | 3           | •                  | 2200        | -    | -         | 750   | -    | V/lx·S           |

| Photo response   | e non-uniformity *8 | PRNU        | •                  | -           | ±10  | -         | -     | ±10  | %                |

| Noise *9         | High gain           |             | -                  | 1           | -    | -         | 1     | -    | mVrms            |

|                  | Low gain            | N           | -                  | 0.6         | -    | -         | 0.6   | -    | IIIvrms          |

| Output offset v  | oltage *10          | Vos         | -                  | Vref        | -    | -         | Vref  | -    | V                |

<sup>\*6:</sup> Integration time ts=1 ms

PRNU =  $\Delta X/X \times 100$  (%)

where X is the average output of all elements and  $\Delta X$  is the difference between the maximum and minimum outputs.

#### ■ Output waveform of one element

# OUTPUT OFFSET VOLTAGE Vref=4.5 V Typ. SATURATION OUTPUT VOLTAGE Vsat=3.5 V Typ. 1 V Typ. SATURATION STATE KMPDC0152EA

#### ■ Spectral response (measurement example)

#### ■ Block diagram

EXTSP Vms Vdd GND 6 RESET TIMING GENERATOR TRIG 3 CLK SHIFT REGISTER EOS HOLD CIRCUIT Video Vref CHARGE AMP ARRAY Vgain Ν 5 N-1 Vpd (12 PHOTODIODE ARRAY KMPDC0153EA KMPDB0220E

<sup>\*7:</sup> Measured with a 2856 K tungsten lamp.

<sup>\*8:</sup> When the photodiode array is exposed to uniform light which is 50 % of the saturation exposure, the Photo Response Non-Uniformity (PRNU) is defined as follows:

<sup>\*9:</sup> Measured with a video data rate of 50 kHz and Ts=1 ms in dark state.

<sup>\*10:</sup> Video output is negative-going output with respect to the output offset voltage.

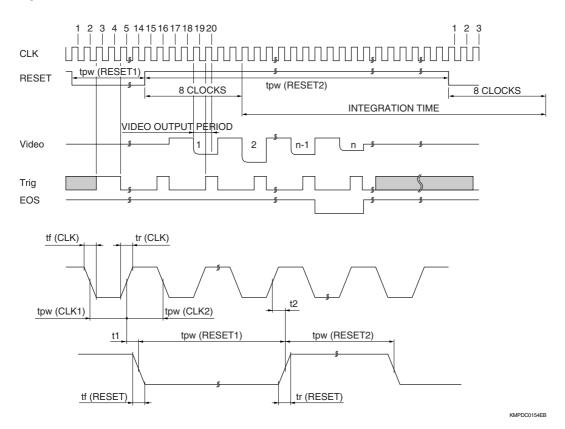

#### ■ Timing chart

| Parameter                        | Symbol                 | Min. | Тур. | Max.  | Unit |

|----------------------------------|------------------------|------|------|-------|------|

| Clock pulse width                | tpw (CLK1), tpw (CLK2) | 125  | ı    | 12500 | ns   |

| Clock pulse rise/fall times      | tr (CLK), tf (CLK)     | 0    | 20   | 30    | ns   |

| Reset pulse width 1              | tpw (RESET1)           | 10   | 1    | -     | μs   |

| Reset pulse width 2              | tpw (RESET2)           | 20   | ı    | -     | μs   |

| Reset pulse rise/fall times      | tr (RESET), tf (RESET) | 0    | 20   | 30    | ns   |

| Clock pulse-reset pulse timing 1 | t1                     | -20  | 0    | 20    | ns   |

| Clock pulse-reset pulse timing 2 | t2                     | -20  | 0    | 20    | ns   |

- 1. The internal timing circuit starts operation at a fall of CLK immediately after a RESET pulse sets to Low.

- 2. When a fall of CLK is counted as "1 clock", the video signal at the 1st channel appears between "18.5 clocks and 20 clocks". Then a video signal appears every 4 clocks.

- 3. Signal charge integration time equals the High period of a RESET pulse. However, the charge integration does not start at the rise of a RESET pulse but starts at the 8th clock after the rise of the RESET pulse and ends at the 8th clock after the fall of the RESET pulse. Signals integrated within this period are sequentially read out as time-series signals by the shift register operation when the RESET pulse next changes from High to Low. The rise and fall of a RESET pulse must be synchronized with the fall of a CLK pulse, but the rise of a RESET pulse must be set outside the video output period. One cycle of RESET pulses cannot be set shorter than the time equal to "(video signal readout period 16.5 + 4) × N (number of pixels)" clocks.

# Photodiode array with amplifier S8865 series

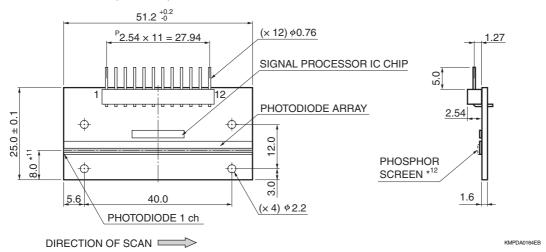

#### ■ Dimensional outline (unit: mm)

\*11: Distance from the bottom of the board to the center of active area

Board: G10 glass epoxy

Connector: PRECI-DIP DURTAL 800-10-012-20-001

\*12:Photodiode array with phosphor screen: S8865-64G/-128G only

· Material Gd2O2S: Tb

· Phosphor thickness 300 µm Typ.

· Detectable energy range 30k to 100 keV

#### ■ Pin connection

| F III COIIII | COLIOIT |                                       |                                            |

|--------------|---------|---------------------------------------|--------------------------------------------|

| Pin No.      | Symbol  | Name                                  | Note                                       |

| 1            | RESET   | Reset pulse                           | Pulse input                                |

| 2            | CLK     | Clock pulse                           | Pulse input                                |

| 3            | Trig    | Trigger pulse                         | Positive-going pulse output                |

| 4            | EXTSP   | External start pulse                  | Pulse input                                |

| 5            | Vms     | Master/slave selection supply voltage | Voltage input                              |

| 6            | Vdd     | Supply voltage                        | Voltage input                              |

| 7            | GND     | Ground                                |                                            |

| 8            | EOS     | End of scan                           | Negative-going pulse output                |

| 9            | Video   | Video output                          | Negative-going output with respect to Vref |

| 10           | Vref    | Reference voltage                     | Voltage input                              |

| 11           | Vgain   | Gain selection terminal voltage       | Voltage input                              |

| 12           | Vpd     | Photodiode voltage                    | Voltage input                              |

#### ■ Gain selection terminal voltage setting

Vdd: High gain (Cf: 0.5 pF) GND: Low gain (Cf: 1 pF)

#### ■ Master/slave selection voltage Vms and external start pulse EXTSP settings

Set to A in the table below in most cases.

To sequentially read out signals from two or more sensors linearly connected, set the 1st sensor to A and the 2nd or later sensors to B. The CLK and RESET pulses should be shared with each sensor and the video output terminal of each sensor connected together.

|   |                                                | Vms | EXTSP                                |

|---|------------------------------------------------|-----|--------------------------------------|

| Α | Parallel readout, serial readout at 1st sensor | Vdd | Vdd                                  |

| В | Serial readout at 2nd and later sensors        | GND | Preceding sensor EOS should be input |

#### ■ Readout circuit

Check that pulse signals meet the required pulse conditions before supplying them to the input terminals. Video output should be amplified by an operational amplifier that is connected close to the sensor.

## Photodiode array with amplifier \$8865 series

#### ■ Cautions during use

- (1) The signal processing circuit chips of S8865 series are protected against static electricity. However, in order to prevent possible damage to the chip, implement electrostatic countermeasures such as grounding of the operator, work table and tools. Furthermore, the devices must be protected against surge voltages from external equipment.

- (2) Since the photodiode array chip is not protected, handle it carefully so it will not become contaminated or scratched. Photodiode array performance may deteriorate if operated at high temperatures and humidity, so the housing should be designed to be airtight. The signal processing circuit chip and its wire bonding are covered with a resin coating for protection, but never touch these portions. In addition, take care when installing the board so that it does not warp.

- (3) S8865-64G, -128G Signal processing IC chip performance will drop if subjected to X-rays. Protect the IC chip from X-rays by installing a lead shield.

Information furnished by HAMAMATSU is believed to be reliable. However, no responsibility is assumed for possible inaccuracies or omissions.

Specifications are subject to change without notice. No patent rights are granted to any of the circuits described herein. ©2004 Hamamatsu Photonics K.K.

HAMAMATSU PHOTONICS K.K., Solid State Division