# MSM66591/ML66592

User's Manual

**CMOS 16-bit microcontroller**

Issue Date: Mar. 4, 2002

#### **Preface**

This document describes the hardware of the 16-bit microcontrollers MSM66591/ML66592 that employ Oki-original CPU core nX-8/500S. Shown below are the related manuals. Refer to them as required.

- nX-8/500S Core Instruction Manual

- Description of nX-8/500S core instruction set

- Description of addressing modes

- MAC66K Assembler Package User's Manual

- · Package overview

- Description of RAS66K [relocatable assembler] operation

- Description of RAS66K assembly language

- Description of RL66K [linker] operation

- Description of LIB66K [librarian] operation

- Description of OH66K [object converter] operation

- Macroprocessor (MP) User's Manual

- Description of MP operation

- · Description of macro processing language

This document is subject to change without notice.

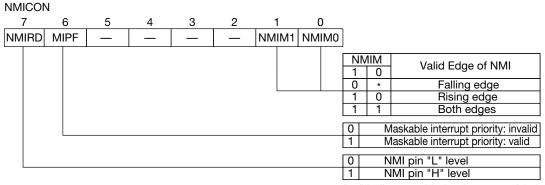

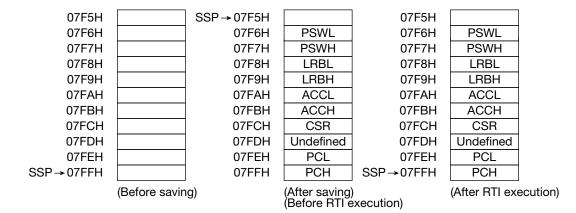

#### **Notation**

| Classification  | Notation                                                                                    | Description                                                                                                                                                                                                                                                                                        |

|-----------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ■ Numeric value | xxH<br>xxb                                                                                  | Represents a hexadecimal number<br>Represents a binary number                                                                                                                                                                                                                                      |

| ■ Unit          | Word, W byte, B nibble, N mega-, M kilo-, K kilo-, k milli-, m micro-, µ nano-, n second, s | 1 word = 16 bits<br>1 byte = 2 nibbles = 8 bits<br>1 nibble = 4 bits<br>106<br>2 <sup>10</sup> = 1024<br>10 <sup>3</sup> = 1000<br>10 <sup>-3</sup><br>10 <sup>-6</sup><br>10 <sup>-9</sup><br>second                                                                                              |

| ■ Terminology   | "H" level<br>"L" level                                                                      | The signal level of the high side of the voltage; indicates the voltage level of $V_{IH}$ and $V_{OH}$ described in the electrical characteristics. The signal level of the low side of the voltage; indicates voltage level of $V_{IL}$ and $V_{OL}$ described in the electrical characteristics. |

|                 | Opcode trap                                                                                 | Operation code trap. Occurs when an empty area that has not been assigned an instruction is fetched, or when an instruction code combination that does not contain an instruction is addressed.                                                                                                    |

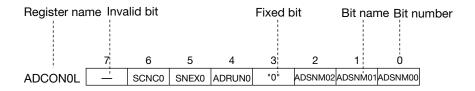

### ■ Register description

Invalid bit Indicates that the bit does not exist. Writing into this bit is invalid. Fixed bit

When writing, always write the specified value. If read, the specified

value will be read. Values of fixed bits are specified as "0" or "1".

# **Contents**

| Chapter | 1 Overview                        |      |

|---------|-----------------------------------|------|

| 1.1     | Features                          | 1-2  |

| 1.2     | Block Diagram                     | 1-4  |

| 1.3     | Pin Configuration                 | 1-5  |

| 1.4     | Basic Operation Timing            | 1-6  |

| Chapter | 2 Description of Pins             |      |

| 2.1     | P0_0-P0_7: Input/Output Pins      | 2-1  |

| 2.2     | P1_0-P1_7: Input/Output Pins      | 2-1  |

| 2.3     | P2_0-P2_7: Input/Output Pins      | 2-1  |

| 2.4     | P3_0-P3_7: Input/Output Pins      | 2-2  |

| 2.5     | P4_0-P4_7: Input/Output Pins      | 2-3  |

| 2.6     | P5_0-P5_7: Input/Output Pins      | 2-3  |

| 2.7     | P6_0-P6_7: Input/Output Pins      | 2-4  |

| 2.8     | P7_0-P7_7: Input/Output Pins      | 2-5  |

| 2.9     | P8_0-P8_7: Input/Output Pins      | 2-6  |

| 2.10    | P9_0-P9_7: Input/Output Pins      | 2-6  |

| 2.11    | P10_0-P10_7: Input/Output Pins    | 2-7  |

| 2.12    | P11_0-P11_7: Input/Output Pins    | 2-8  |

| 2.13    | P12_0, P12_1: Input/Output Pins   | 2-9  |

| 2.14    | AI0-AI23: Input Pins              | 2-9  |

| 2.15    | AV <sub>DD</sub> : Input Pin      | 2-9  |

| 2.16    | V <sub>REF</sub> : Input Pin      | 2-9  |

| 2.17    | AGND: Input Pin                   | 2-9  |

| 2.18    | OSC0, OSC1: Input Pin, Output Pin | 2-9  |

| 2.19    | OE: Input Pin                     | 2-9  |

| 2.20    | NMI: Input Pin                    | 2-9  |

| 2.21    | RES: Input Pin                    | 2-9  |

| 2.22    | EA: Input Pin                     | 2-10 |

| 2.23    | TEST: Input Pin                   | 2-10 |

| 2.24    | V <sub>DD</sub> : Input Pin       | 2-10 |

| 2.25    | GND: Input Pin                    | 2-10 |

| 2.26    | Structure of Pins                 | 2-10 |

| 2 27    | Handling of Unused Pins           | 2-12 |

## **Chapter 3 CPU Architecture**

| 3.1 N | Memory Space                                           | 3-1  |

|-------|--------------------------------------------------------|------|

| 3.1.1 | Memory Space Expansion                                 | 3-1  |

| 3.1.2 | Program Memory Space                                   | 3-2  |

| [1]   | Accessing Program Memory Space                         | 3-4  |

| [2]   | Vector Table Area                                      | 3-4  |

| [3]   | VCAL Table Area                                        | 3-6  |

| [4]   | ACAL Area                                              | 3-7  |

| 3.1.3 | Data Memory Space                                      | 3-8  |

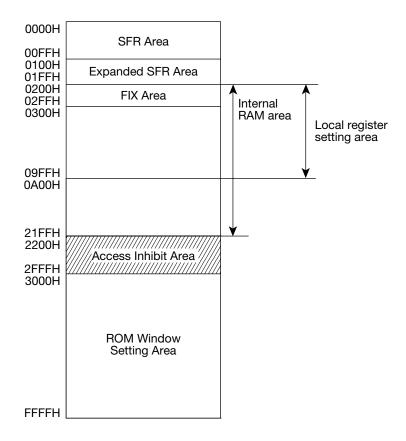

| [1]   | Special Function Register (SFR) Area                   | 3-9  |

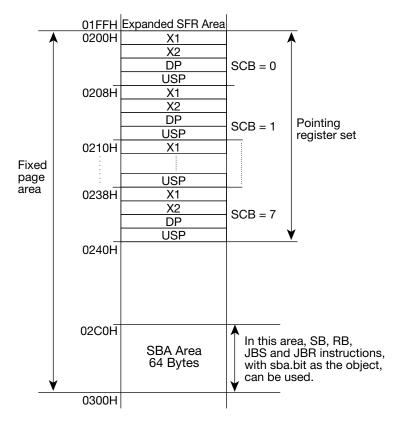

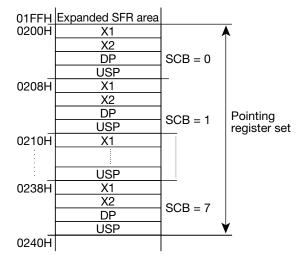

| [2]   | Expanded Special Function Register (Expanded SFR) Area | 3-9  |

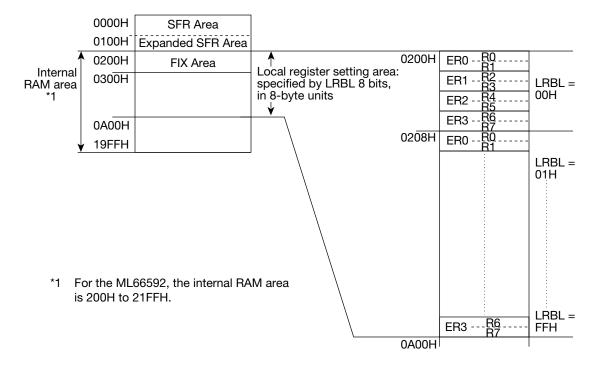

| [3]   | Internal RAM Area                                      | 3-9  |

| [4]   | Fixed Page (FIX) Area                                  | 3-10 |

| [5]   | Local Register Setting Area                            | 3-11 |

| [6]   | ROM Window Setting Area                                | 3-11 |

| 3.1.4 | Data Memory Access                                     | 3-12 |

| [1]   | Byte Operation                                         | 3-12 |

| [2]   | Word Operation                                         | 3-12 |

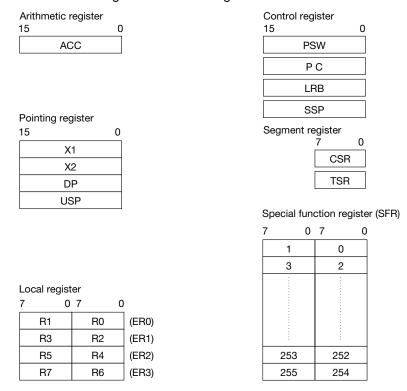

| 3.2 F | Registers                                              | 3-13 |

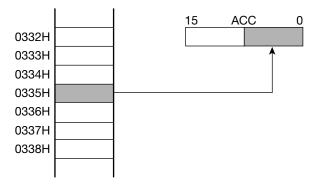

| 3.2.1 | Arithmetic Register (ACC)                              | 3-13 |

| 3.2.2 | Control Register                                       | 3-14 |

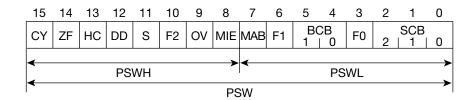

| [1]   | Program Status Word (PSW)                              | 3-14 |

| [2]   | Program Counter (PC)                                   | 3-17 |

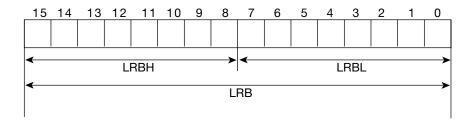

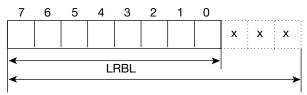

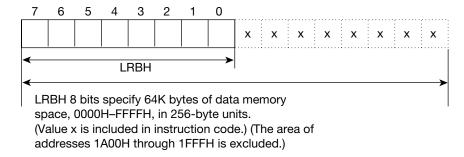

| [3]   | Local Register Base (LRB)                              | 3-17 |

| [4]   | System Stack Pointer (SSP)                             | 3-18 |

| 3.2.3 | Pointing Register (PR)                                 | 3-19 |

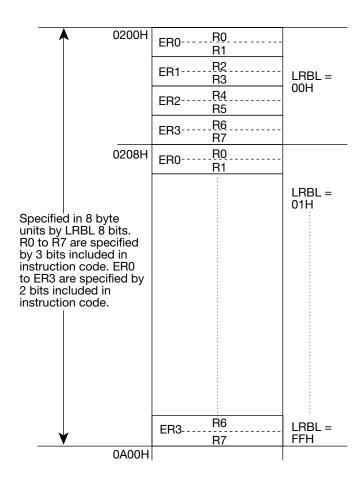

| 3.2.4 | Local Registers (R, ER)                                | 3-20 |

| 3.2.5 | Segment Register                                       | 3-21 |

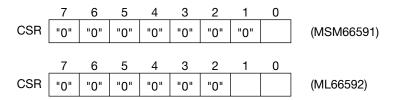

| [1]   | Code Segment Register (CSR)                            | 3-21 |

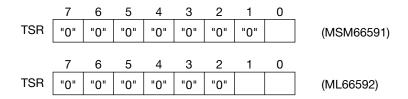

| [2]   | Table Segment Register (TSR)                           | 3-22 |

| 3.2.6 | Special Function Register (SFR)                        | 3-23 |

| 3.3 A | Addressing Mode                                        | 3-37 |

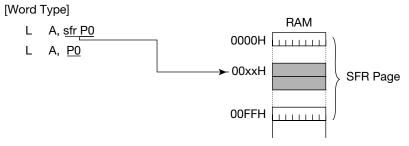

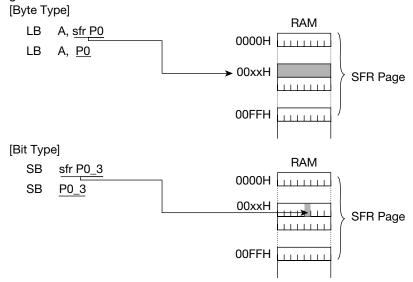

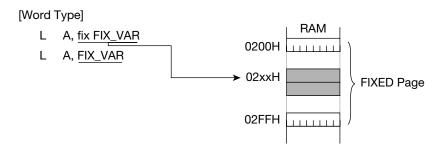

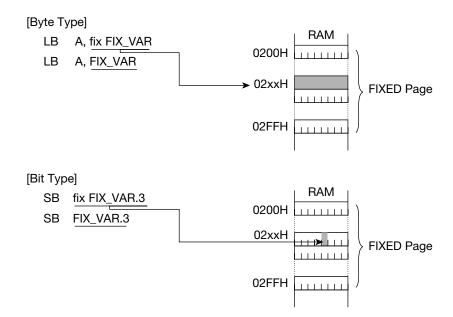

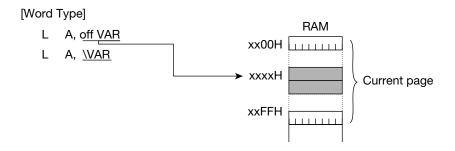

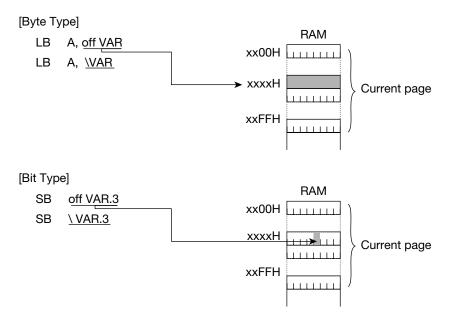

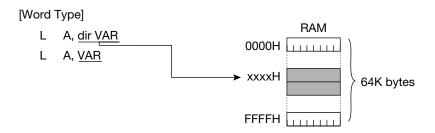

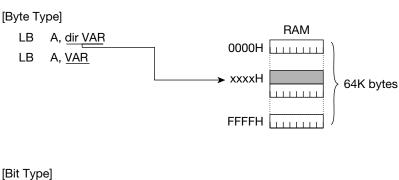

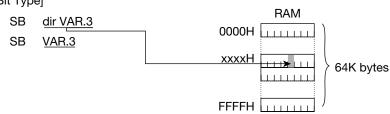

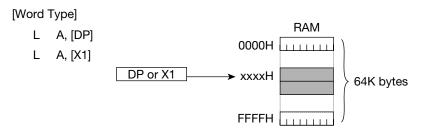

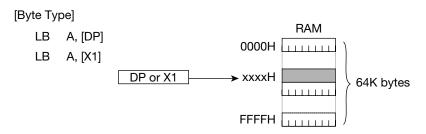

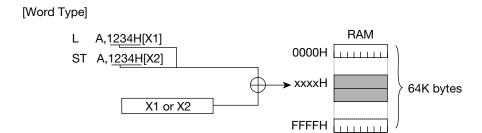

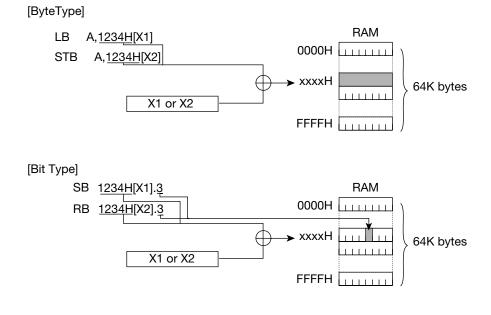

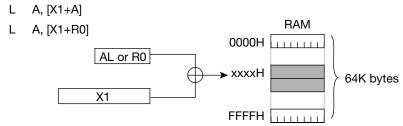

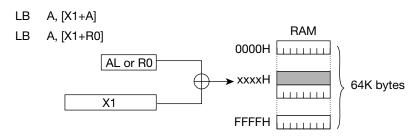

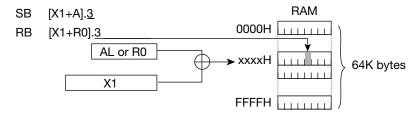

| 3.3.1 | RAM Addressing                                         | 3-37 |

| [1]   | Register Addressing                                    | 3-37 |

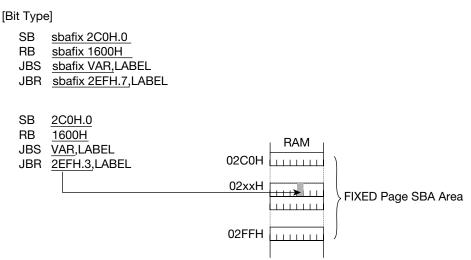

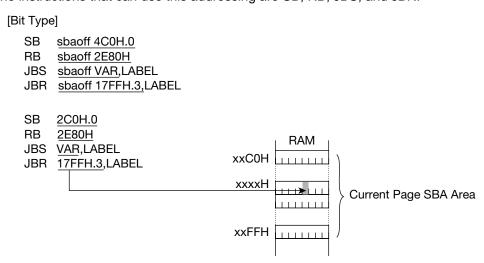

| [2]   | Page Addressing                                        | 3-40 |

| [3]   | Direct Data Addressing                                 | 3-43 |

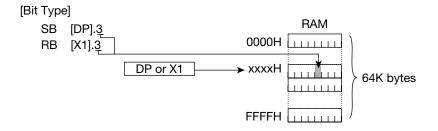

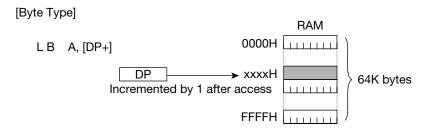

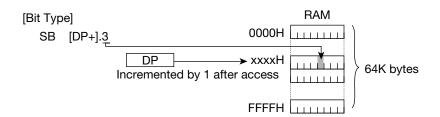

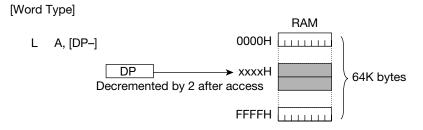

| [4]   | Pointing Register Indirect Addressing                  | 3-44 |

| [5]   | Special Bit Area Addressing                            | 3-50 |

| 3.3.2     | ROM Addressing                                            | 3-51   |

|-----------|-----------------------------------------------------------|--------|

| [1]       | Immediate Addressing                                      | 3-51   |

| [2]       | Table Data Addressing                                     | 3-51   |

| [3]       | Program Code Addressing                                   | 3-53   |

| [4]       | ROM Window Addressing                                     | 3-55   |

| Chapter 4 | CPU Control Functions                                     |        |

| 4.1       | Standby Function                                          | 4-1    |

| 4.1.1     | Standby Control Register (SBYCON)                         | 4-3    |

| 4.1.2     | Operation in Each Standby Mode                            | 4-4    |

| [1]       | HALT Mode                                                 | 4-4    |

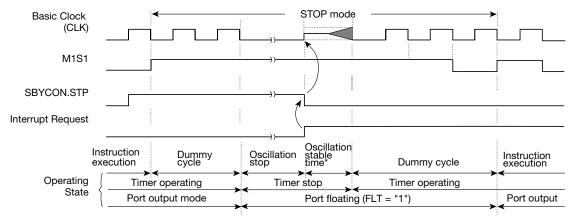

| [2]       | STOP Mode                                                 | 4-5    |

| 4.2 F     | Reset Function                                            | 4-6    |

| Chapter 5 | Memory Control Functions                                  |        |

| 5.1 F     | ROM Window Function                                       | 5-1    |

| 5.2 F     | READY Function                                            | 5-3    |

| Chapter 6 | Port Functions                                            |        |

| 6.1 H     | Hardware Configuration of Each Port                       | 6-1    |

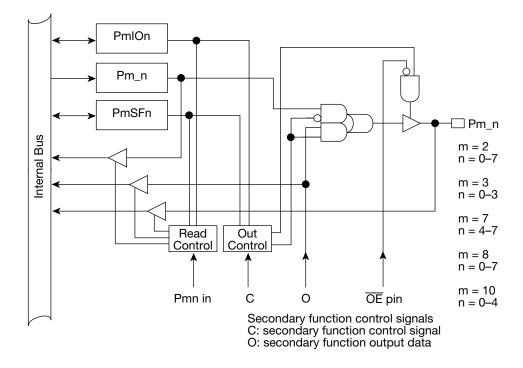

| 6.1.1     | Configuration of Type A (P0_0-P0_7, P1_0-P1_7, P12_0)     | 6-4    |

| 6.1.2     | Configuration of Type B                                   |        |

|           | (P2_0-P2_7, P3_0-P3_3, P7_4-P7_7, P8_0-P8_7, P10_0-P10    | 4) 6-5 |

| 6.1.3     | Configuration of Type C                                   |        |

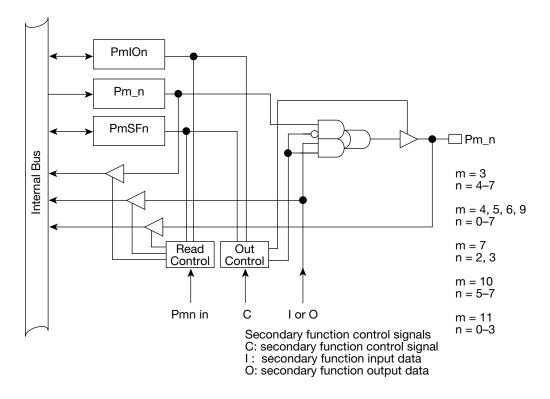

|           | (P3_4-P3_7, P4_0-P4_7, P5_0-P5_7, P6_0-P6_7, P7_2, P7_3,  |        |

|           | P9_0-P9_7, P10_5-P10_7, P11_0-P11_3)                      | 6-6    |

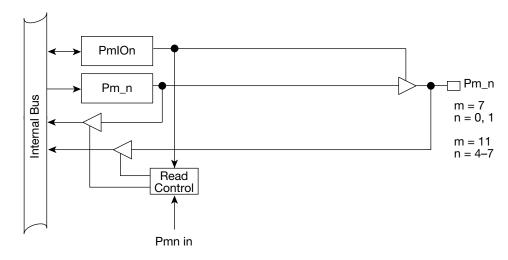

| 6.1.4     | Configuration of Type D (P7_0, P7_1, P11_4–P11_7)         | 6-7    |

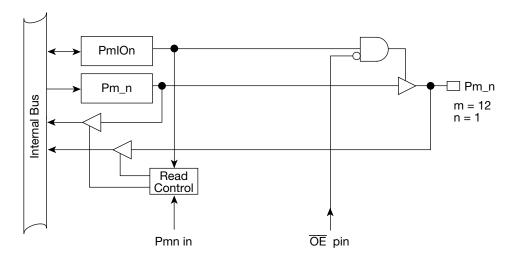

| 6.1.5     | Configuration of Type E (P12_1)                           | 6-7    |

| 6.2 F     | Port Control Registers                                    | 6-8    |

| 6.2.1     | Port Data Register (Pn: n = 0-12)                         | 6-8    |

| 6.2.2     | Port Mode Register (PnIO: n = 0–12)                       | 6-8    |

| 6.2.3     | Port Secondary Function Control Register (PnSF: n = 2–10) | 6-8    |

| 6.3 F     | Port 0 (P0)                                               | 6-11   |

| 6.4 F     | Port 1 (P1)                                               | 6-12   |

| 6.5 F     | Port 2 (P2)                                               | 6-13   |

| 6.6 F     | Port 3 (P3)                                               | 6-15   |

| 6.7 F     | Port 4 (P4)                                               | 6-17   |

| 6.8     | Port 5 (P5)                                               | 6-19  |

|---------|-----------------------------------------------------------|-------|

| 6.9     | Port 6 (P6)                                               | 6-21  |

| 6.10    | Port 7 (P7)                                               | 6-23  |

| 6.11    | Port 8 (P8)                                               | 6-25  |

| 6.12    | Port 9 (P9)                                               | 6-27  |

| 6.13    | Port 10 (P10)                                             | 6-29  |

| 6.14    | Port 11 (P11)                                             | 6-31  |

| 6.15    | Port 12 (P12)                                             | 6-32  |

| Chapter | 7 Output Pin Control Pin (OE)                             |       |

| Chapter | 8 Clock Generation Circuit                                |       |

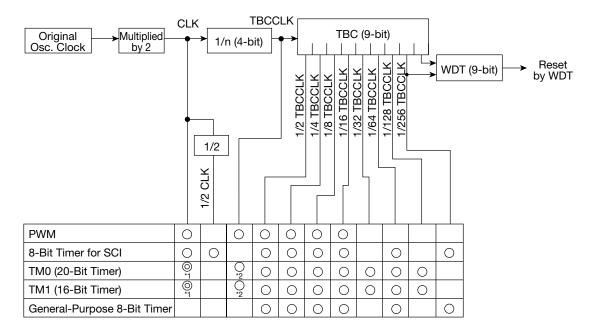

| Chapter | 9 Time Base Counter (TBC)                                 |       |

| 9.1     | 1/n Counter                                               | 9-2   |

| Chapter | 10 Watchdog Timer (WDT)                                   |       |

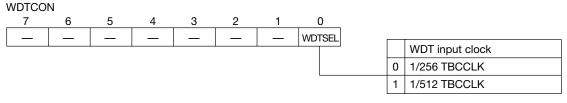

| 10.1    | WDT Control Register (WDTCON)                             | 10-1  |

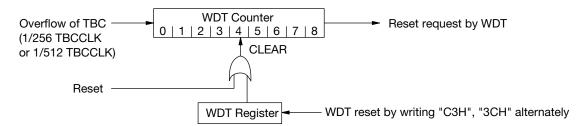

| 10.2    | Operation of WDT                                          |       |

| 10.3    | Time until Overflow of WDT                                | 10-2  |

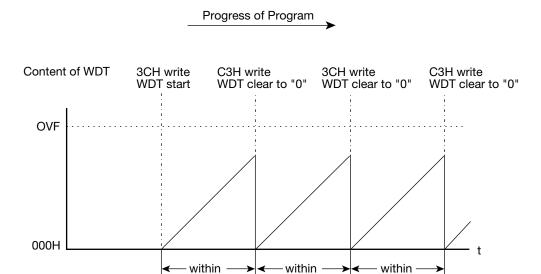

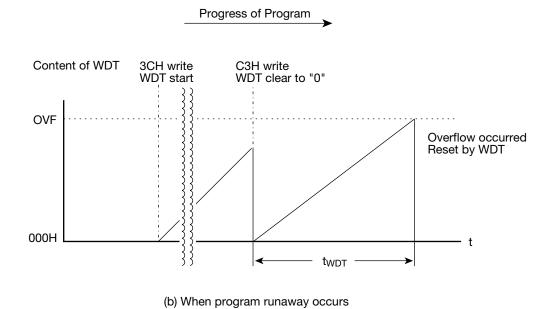

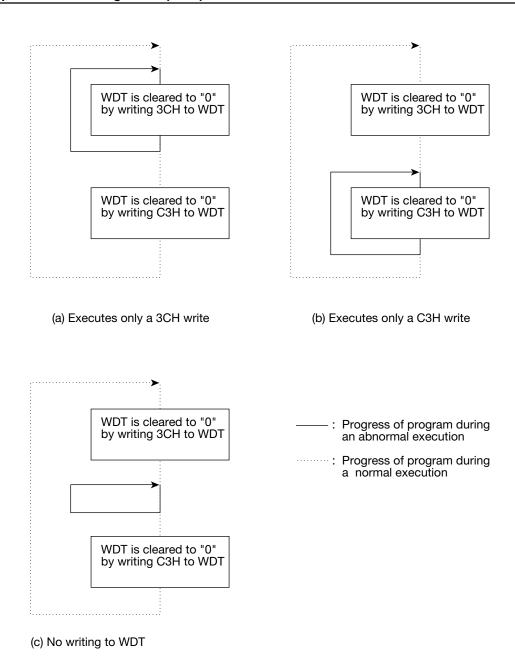

| 10.4    | Program Runaway Detection Timing Diagram                  | 10-2  |

| Chapter | 11 Flexible Timer (FTM)                                   |       |

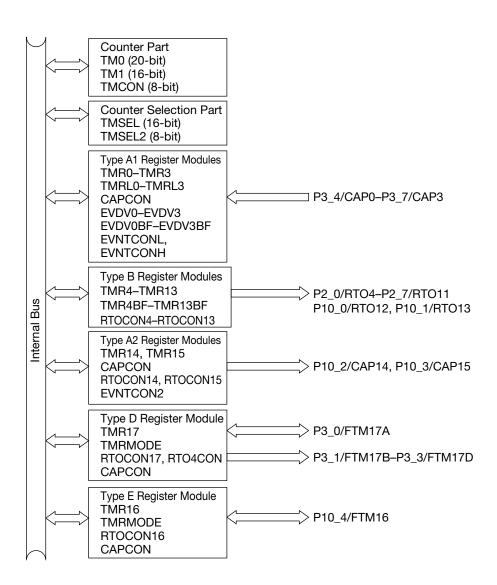

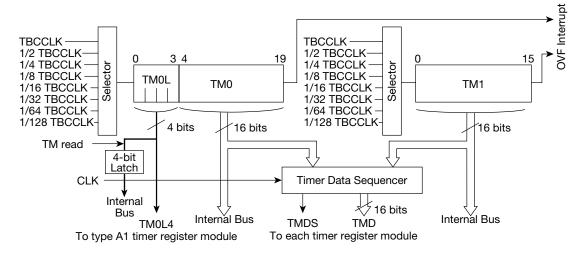

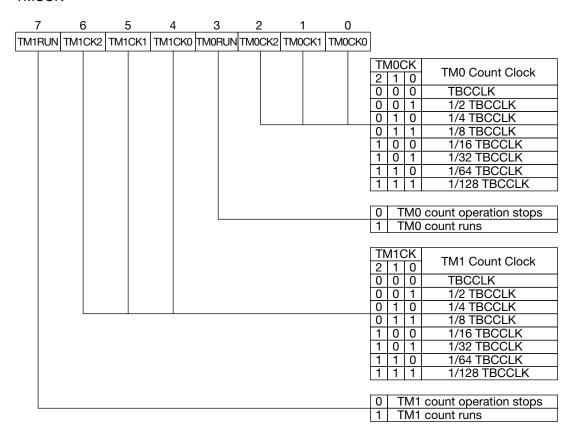

| 11.1    | Configuration of Counter Part                             | 11-6  |

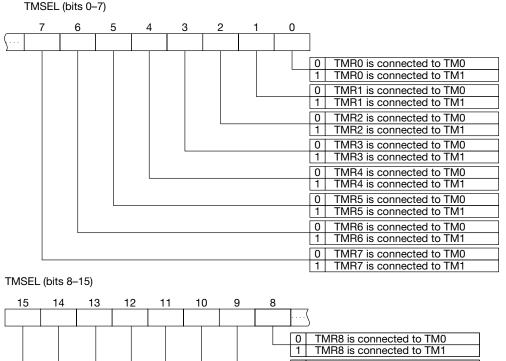

| 11.2    | Counter Selection Part                                    |       |

|         | Type A1 Register Modules (TMR0–TMR3)                      |       |

|         | 3.1 Configuration of Type A1 Register Modules (TMR0–TMR3) |       |

| [´      | I] Timer Registers (TMR0, TMR0L–TMR3, TMR3L)              |       |

| [2      | - , , , , , , , , , , , , , , , , , , ,                   |       |

| [3      | ,                                                         |       |

| [4      |                                                           |       |

| -       | 5] EVDV0–EVDV3 Buffer Registers (EVDV0BF–EVDV3BF)         |       |

| 11.3    | , , ,                                                     |       |

| 11.3    |                                                           |       |

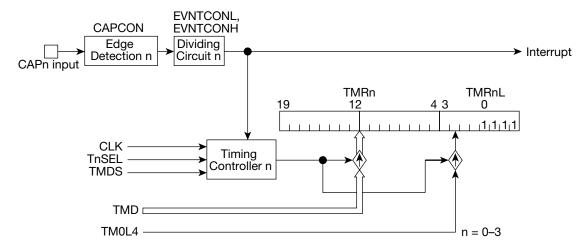

| -       | I] Configuration of Dividing Circuit                      |       |

| -       | 2] Operation of Dividing Circuit                          |       |

| [3      | B] Operation to Switch Dividing Ratio                     | 11-16 |

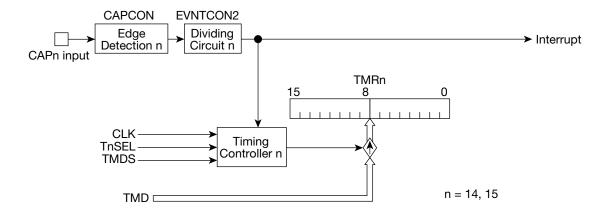

| 11.4 Type A2 Register Modules (TMR14, TMR15)                      | 11-17 |

|-------------------------------------------------------------------|-------|

| 11.4.1 Configuration of Type A2 Register Modules (TMR14, TMR15)   | 11-17 |

| [1] Timer Registers (TMR14, TMR15)                                | 11-17 |

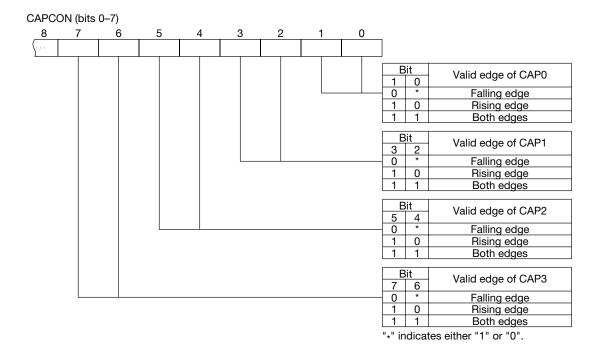

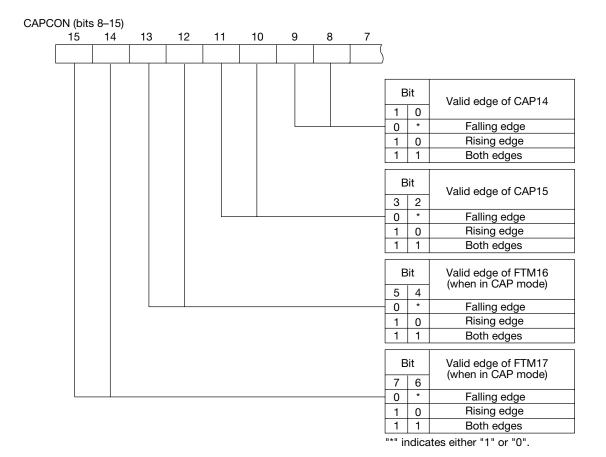

| [2] Capture Control Register (CAPCON)                             | 11-18 |

| [3] Event Control Register 2 (EVNTCON2)                           | 11-19 |

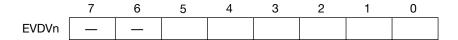

| [4] Event Dividing Counters 14, 15 (EVDV14, EVDV15)               | 11-20 |

| [5] EVDV14, EVDV15 Buffer Registers (EVDV14BF, EVDV15BF)          |       |

| 11.4.2 Operation of Type A2 Register Modules (TMR14, TMR15)       |       |

| 11.4.3 Capture Pin Dividing Circuit                               | 11-22 |

| [1] Configuration of Dividing Circuit                             | 11-22 |

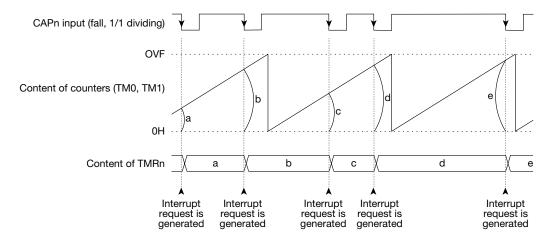

| [2] Operation of Dividing Circuit                                 | 11-22 |

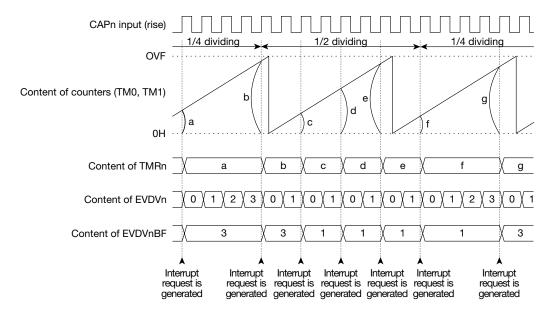

| [3] Operation to Switch Dividing Ratio                            | 11-22 |

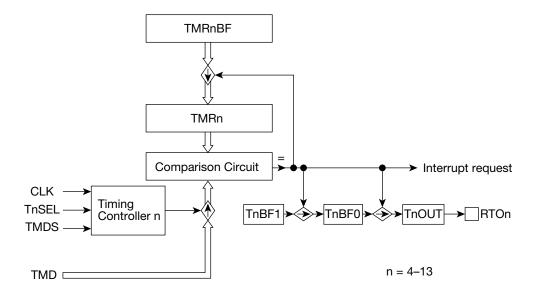

| 11.5 Type B Register Modules (TMR4–TMR13)                         | 11-23 |

| 11.5.1 Configuration of Type B Register Modules (TMR4–TMR13)      | 11-23 |

| [1] Timer Registers (TMR4–TMR13)                                  | 11-24 |

| [2] Timer Register Buffer Registers (TMR4BF–TMR13BF)              | 11-24 |

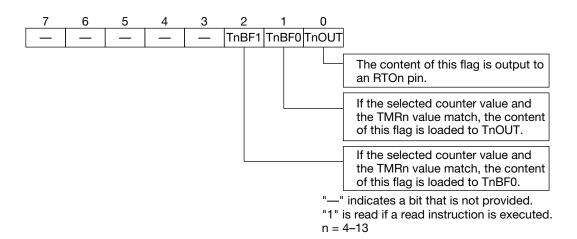

| [3] Real-time Output Control Registers (RTOCON4-RTOCON13)         | 11-24 |

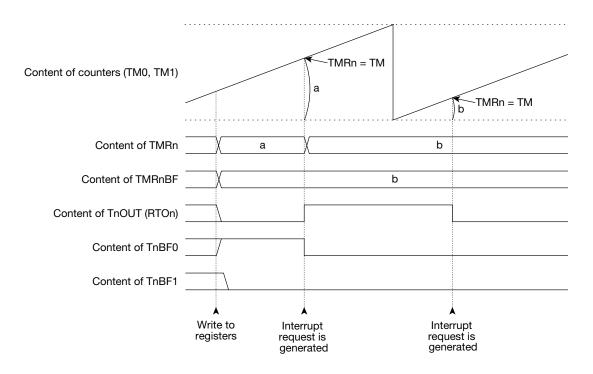

| 11.5.2 Operation of Type B Register Modules (TMR4–TMR13)          | 11-26 |

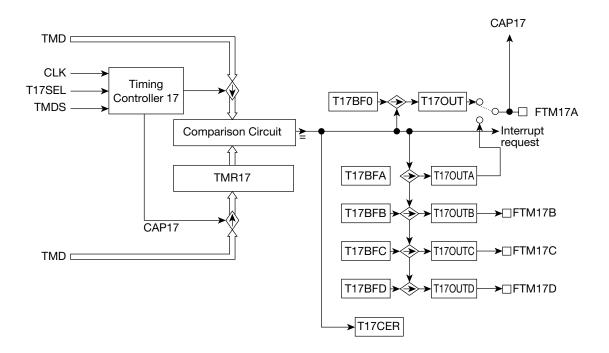

| 11.6 Type D Register Module (TMR17)                               | 11-27 |

| 11.6.1 Configuration of Type D Register Module (TMR17)            | 11-27 |

| [1] Timer Register (TMR17)                                        | 11-29 |

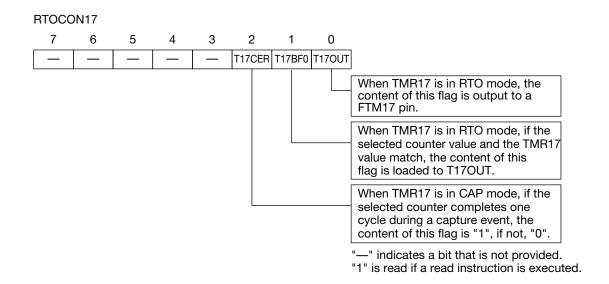

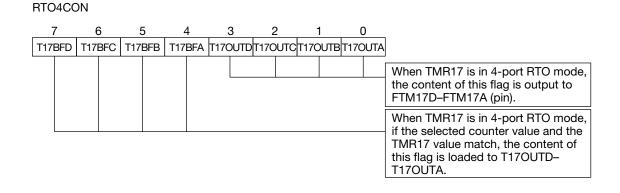

| [2] Real-time Output Control Registers (RTOCON17, RTO4CON)        | 11-29 |

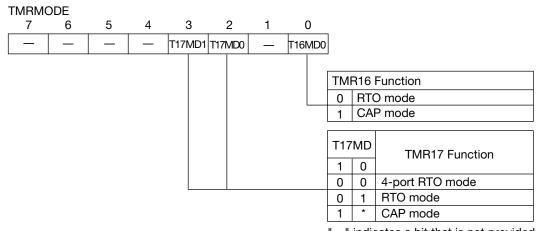

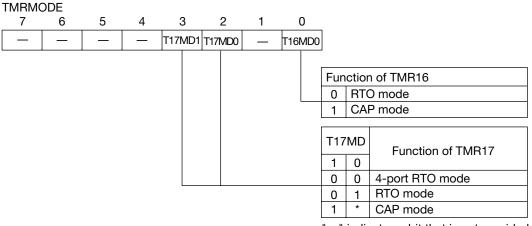

| [3] TMR Mode Register (TMRMODE)                                   | 11-31 |

| [4] Capture Control Register (CAPCON)                             | 11-32 |

| 11.6.2 Operation of Type D Register Module (TMR17)                | 11-33 |

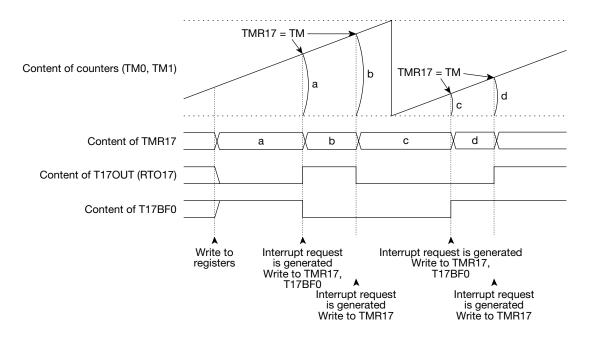

| [1] Operation in Real-time Output Mode (RTO)                      | 11-33 |

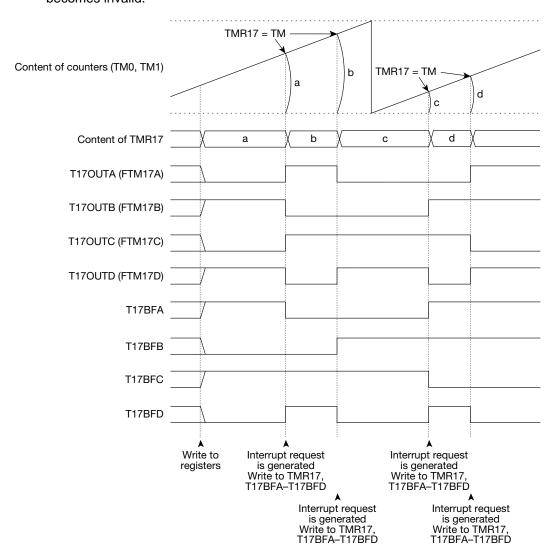

| [2] Operation in 4-Port Output Real-time Output Mode (4-Port RTO) | 11-34 |

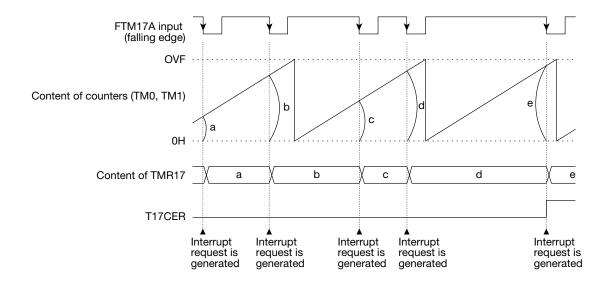

| [3] Operation in CAP Mode                                         | 11-35 |

| 11.7 Type E Register Module (TMR16)                               | 11-36 |

| 11.7.1 Configuration of Type E Register Module (TMR16)            | 11-36 |

| [1] Timer Register (TMR16)                                        | 11-37 |

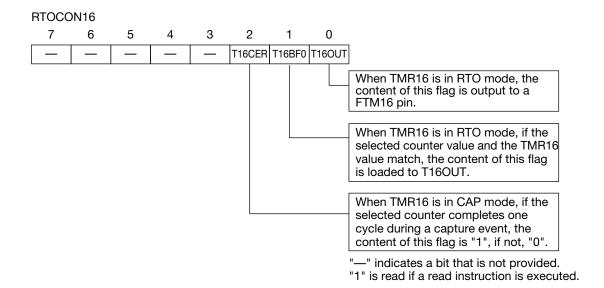

| [2] Real-time Output Control Register (RTOCON16)                  | 11-37 |

| [3] TMR Mode Register (TMRMODE)                                   | 11-38 |

| [4] Capture Control Register (CAPCON)                             | 11-39 |

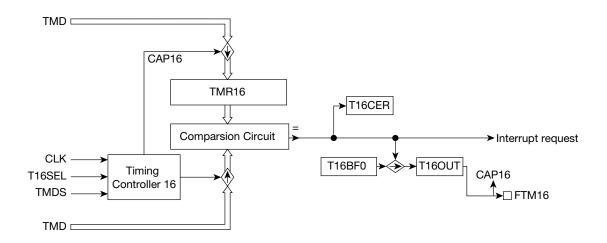

| 11.7.2 Operation of Type E Register Module (TMR16)                | 11-40 |

| [1] Operation in Real-time Output Mode (RTO)                      | 11-40 |

| [2] Operation in CAP Mode                                         | 11-40 |

| 11.8 RTO Mode Output Timing Changes                               | 11-41 |

| Chapter 12 General-Purpose 8-Bit Timer Function                  |             |

|------------------------------------------------------------------|-------------|

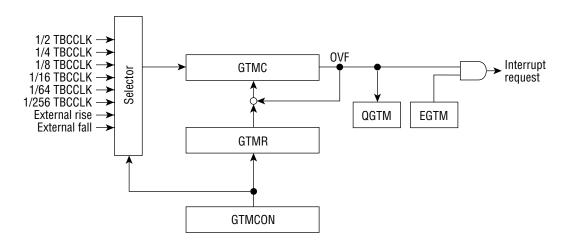

| 12.1 General-Purpose 8-Bit Timer (GTM)                           | 12-2        |

| [1] General-Purpose 8-Bit Timer Counter (GTMC)                   | 12-3        |

| [2] General-Purpose 8-Bit Timer Register (GTMR)                  | 12-3        |

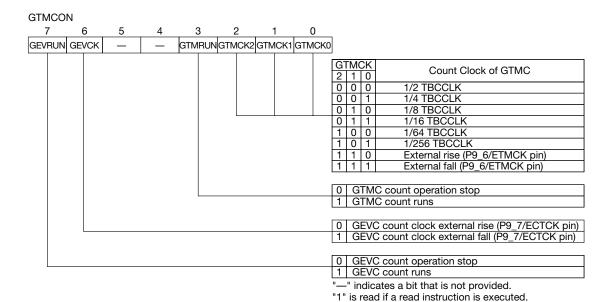

| [3] General-Purpose 8-Bit Timer Control Register (GTMCON)        | 12-3        |

| [4] General-Purpose 8-Bit Timer Interrupt Control Register (GTII | NTCON) 12-5 |

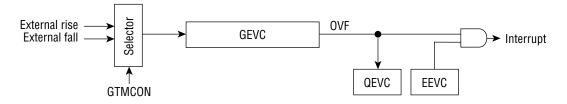

| 12.2 General-Purpose 8-Bit Event Counter (GEVC)                  | 12-6        |

| [1] General-Purpose 8-Bit Event Counter (GEVC)                   | 12-6        |

| [2] General-Purpose 8-Bit Timer Control Register (GTMCON)        | 12-6        |

| [3] General-Purpose 8-Bit Timer Interrupt Control Register (GTII | NTCON) 12-7 |

| Chapter 13 PWM Functions                                         |             |

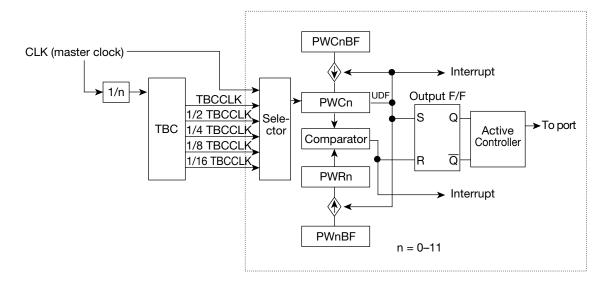

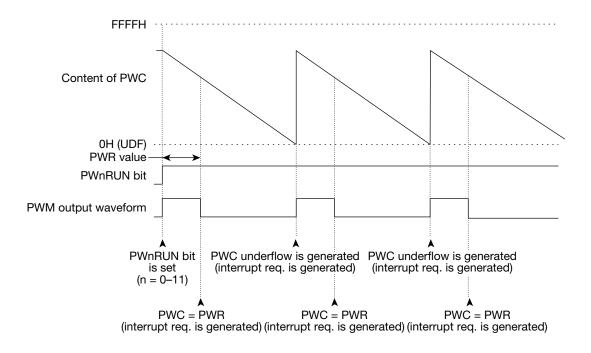

| 13.1 Configuration of PWM                                        | 13-4        |

| [1] PWM Counters (PWC0-PWC11)                                    | 13-4        |

| [2] PWM Counter Buffer Registers (PWC0BF–PWC11BF)                | 13-4        |

| [3] PWM Registers (PWR0–PWR11)                                   | 13-5        |

| [4] PWM Buffer Registers (PW0BF–PW11BF)                          | 13-5        |

| [5] Comparison Circuit                                           | 13-5        |

| [6] Output F/F                                                   | 13-5        |

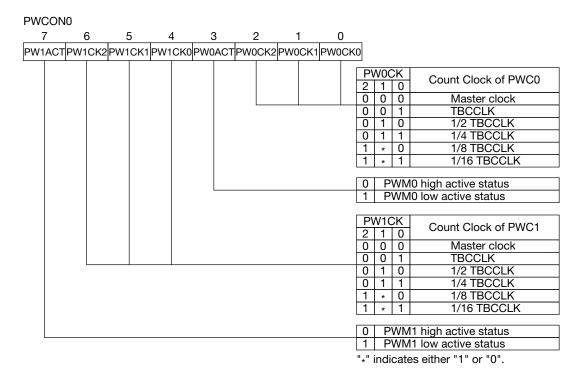

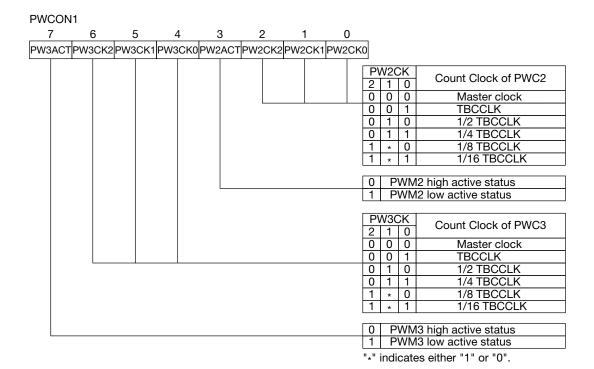

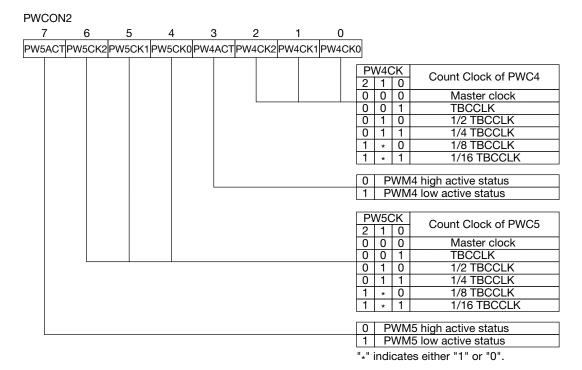

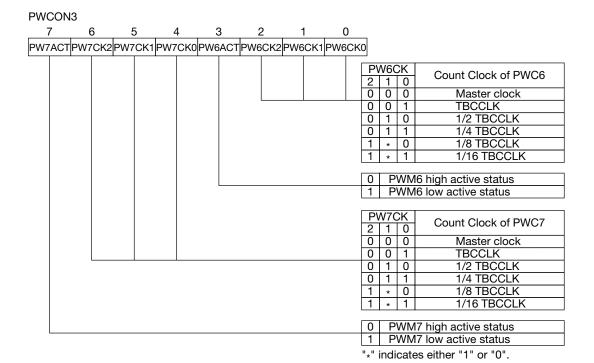

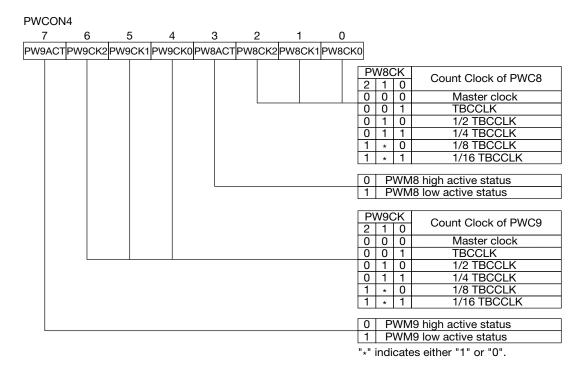

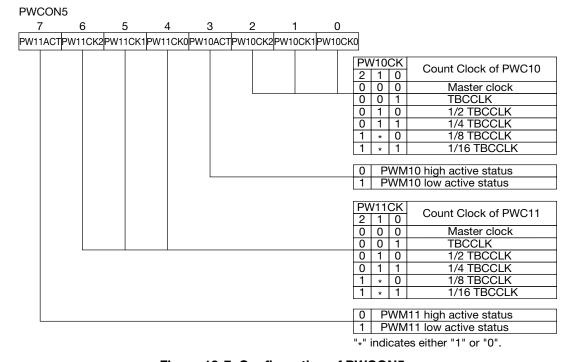

| [7] PWM Control Registers (PWCON0–PWCON5)                        | 13-5        |

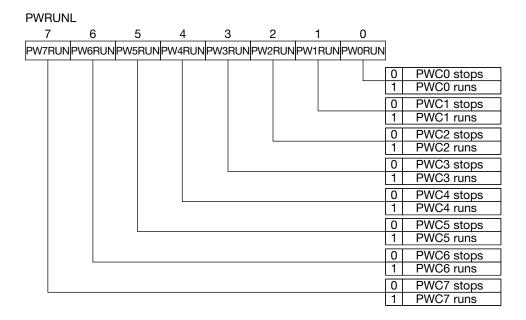

| [8] PWMRUN Register (PWRUN)                                      | 13-9        |

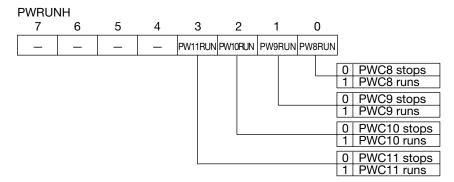

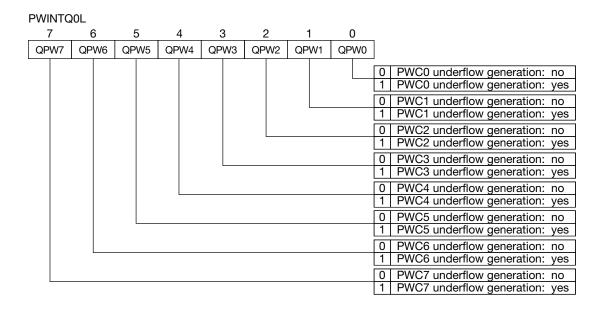

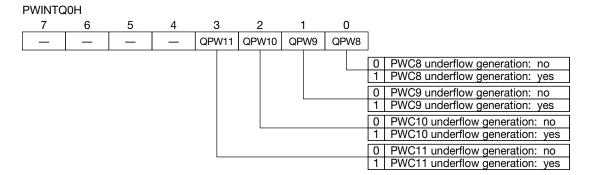

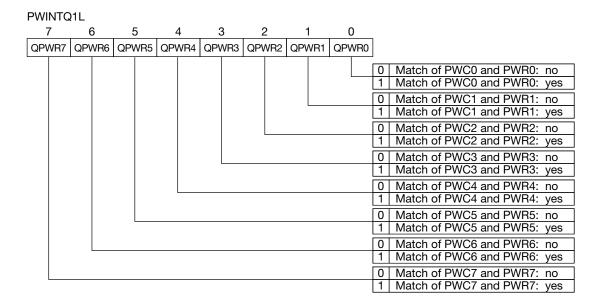

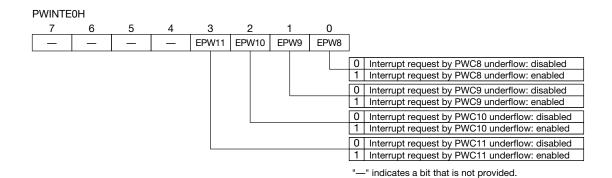

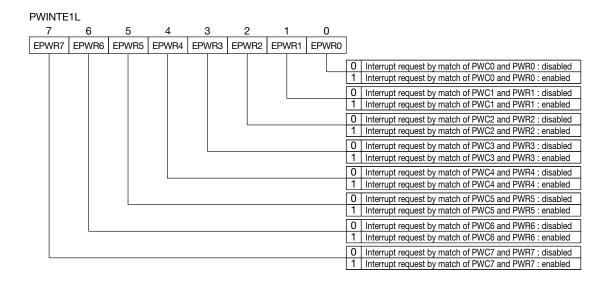

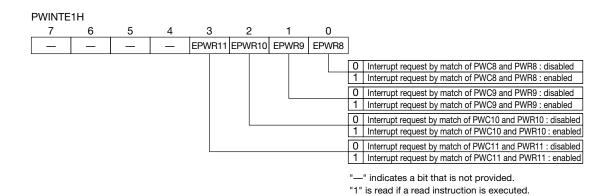

| [9] PWM Interrupt Registers (PWINTQ0, PWINTQ1)                   | 13-10       |

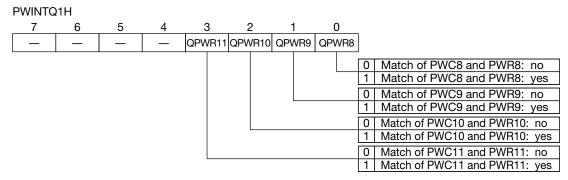

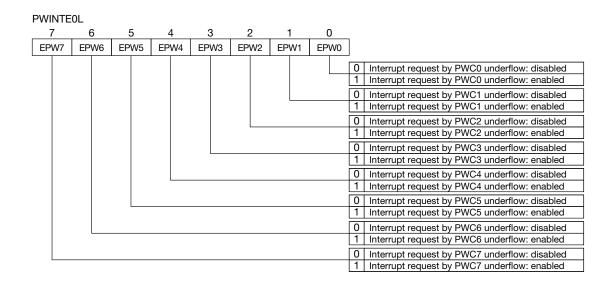

| [10] PWM Interrupt Enable Registers (PWINTE0, PWINTE1)           | 13-13       |

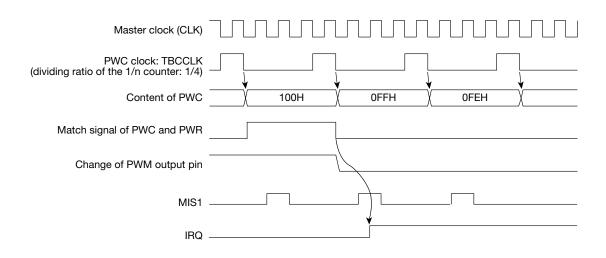

| 13.2 Operation of PWM                                            | 13-16       |

| Chapter 14 Baud Rate Generator Functions                         |             |

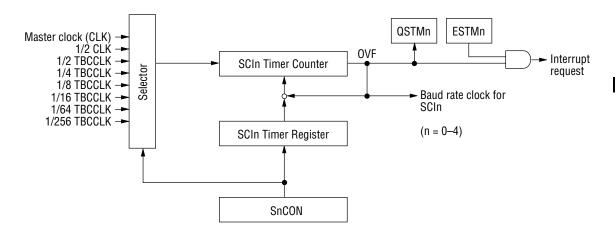

| 14.1 Configuration of SCI0 Timer (S0TM)                          |             |

| [1] SCI0 Timer Counter                                           | 14-3        |

| [2] SCI0 Timer Register                                          |             |

| [3] SCI0 Timer Control Register (S0CON)                          | 14-3        |

| 14.2 Operation of SCI0 Timer                                     |             |

| 14.3 Configuration of SCI1 Timer (S1TM)                          | 14-6        |

| [1] SCI1 Timer Counter                                           |             |

| [2] SCI1 Timer Register                                          |             |

| [3] SCI1 Timer Control Register (S1CON)                          |             |

| 14.4 Operation of SCI1 Timer                                     | 14-8        |

| 14.5 Configuration of SCI2 Timer (S2TM)                    | 14-9  |

|------------------------------------------------------------|-------|

| [1] SCI2 Timer Counter                                     | 14-9  |

| [2] SCI2 Timer Register                                    | 14-9  |

| [3] SCI2 Timer Control Register (S2CON)                    | 14-9  |

| 14.6 Operation of SCI2 Timer                               | 14-11 |

| 14.7 Configuration of SCI3 Timer (S3TM)                    | 14-12 |

| [1] SCI3 Timer Counter                                     | 14-12 |

| [2] SCI3 Timer Register                                    | 14-12 |

| [3] SCI3 Timer Control Register (S3CON)                    | 14-12 |

| 14.8 Operation of SCI3 Timer                               | 14-14 |

| 14.9 Configuration of SCI4 Timer (S4TM)                    | 14-15 |

| [1] SCI4 Timer Counter                                     | 14-15 |

| [2] SCI4 Timer Register                                    | 14-15 |

| [3] SCI4 Timer Control Register (S4CON)                    | 14-15 |

| 14.10 Operation of SCI4 Timer                              | 14-17 |

|                                                            |       |

| Chapter 15 Serial Port Functions                           |       |

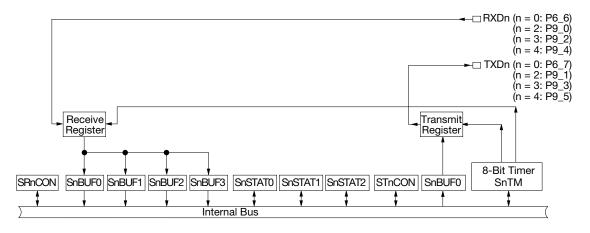

| 15.1 Configuration of Serial Ports                         | 15-2  |

| 15.2 Serial Port Control Registers                         |       |

| 15.2.1 Control Registers for SCI0                          | 15-5  |

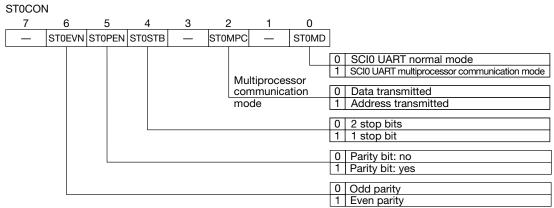

| [1] SCI0 Transmit Control Register (ST0CON)                | 15-5  |

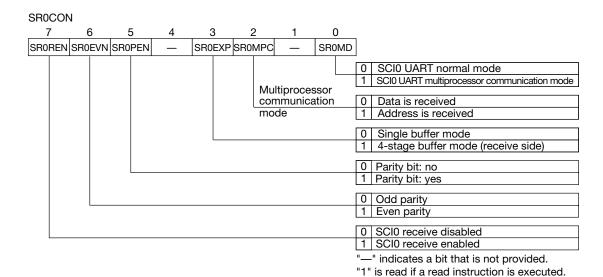

| [2] SCI0 Receive Control Register (SR0CON)                 | 15-7  |

| [3] SCI0 Transmit/Receive Buffer Register (S0BUF0)         | 15-9  |

| [4] SCI0 Receive Buffer Registers (S0BUF1, S0BUF2, S0BUF3) | 15-9  |

| [5] SCI0 Transmit and Receive Registers                    | 15-9  |

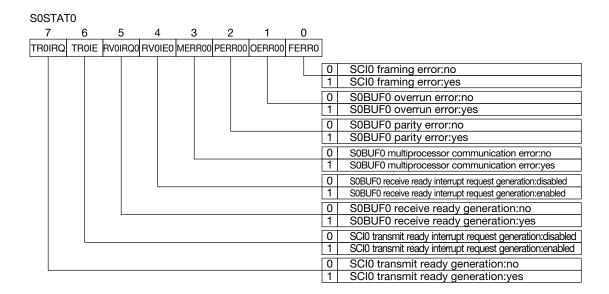

| [6] SCI0 Status Register 0 (S0STAT0)                       | 15-10 |

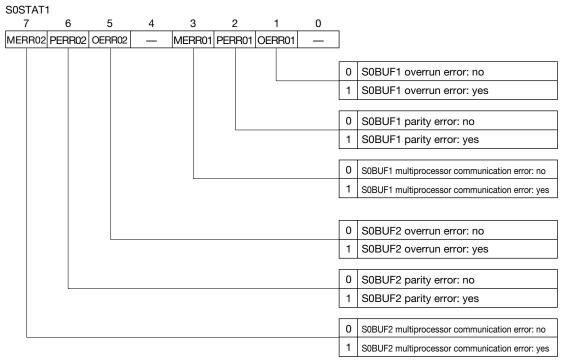

| [7] SCI0 Status Register 1 (S0STAT1)                       | 15-13 |

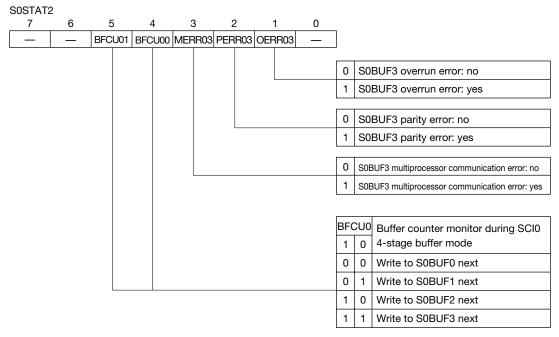

| [8] SCI0 Status Register 2 (S0STAT2)                       | 15-15 |

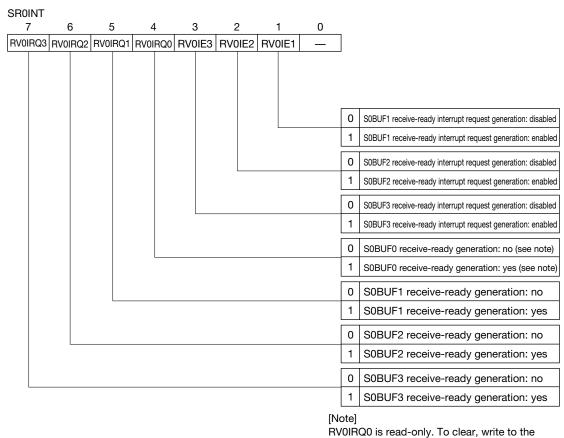

| [9] SCI0 Interrupt Control Register (SR0INT)               | 15-17 |

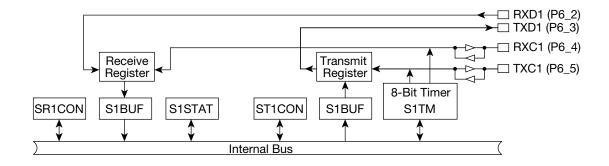

| 15.2.2 Control Registers for SCI1                          | 15-19 |

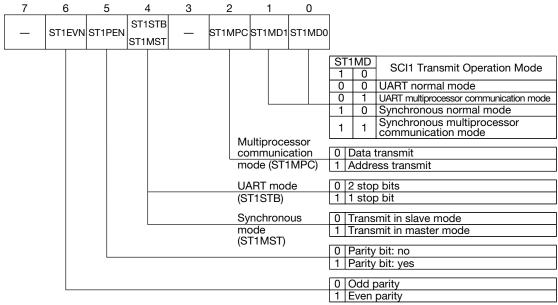

| [1] SCI1 Transmit Control Register (ST1CON)                | 15-19 |

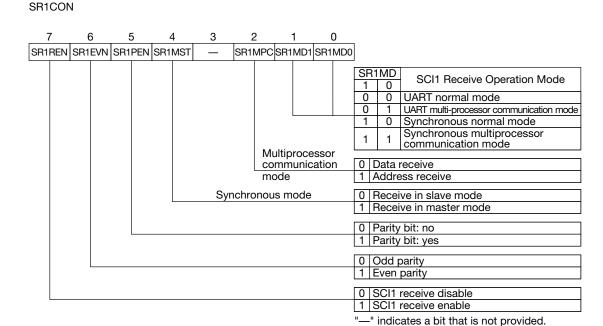

| [2] SCI1 Receive Control Register (SR1CON)                 | 15-21 |

| [3] SCI1 Transmit/Receive Buffer Register (S1BUF)          | 15-23 |

| [4] SCI1 Transmit and Receive Registers                    | 15-23 |

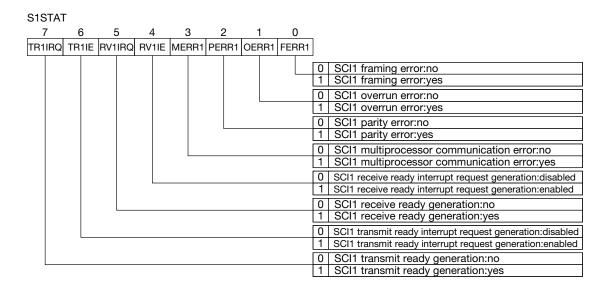

| [5] SCI1 Status Register (S1STAT)                          | 15-23 |

|                                                            |       |

| 15.2.3 | Control Registers for SCI2                             | 15-26 |

|--------|--------------------------------------------------------|-------|

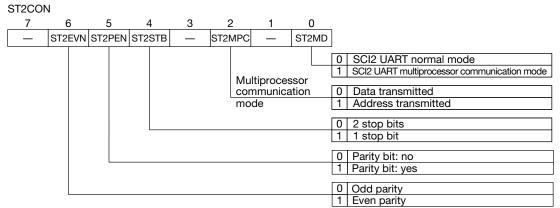

| [1]    | SCI2 Transmit Control Register (ST2CON)                | 15-26 |

| [2]    | SCI2 Receive Control Register (SR2CON)                 | 15-28 |

| [3]    | SCI2 Transmit/Receive Buffer Register (S2BUF0)         | 15-30 |

| [4]    | SCI2 Receive Buffer Registers (S2BUF1, S2BUF2, S2BUF3) | 15-30 |

| [5]    | SCI2 Transmit and Receive Registers                    | 15-30 |

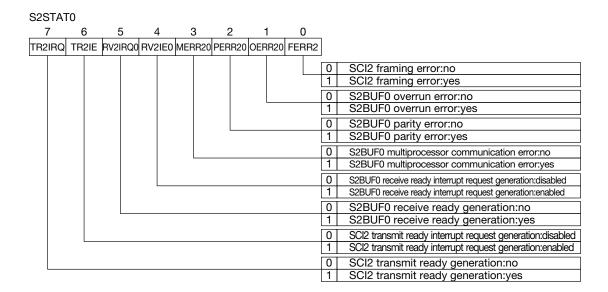

| [6]    | SCI2 Status Register 0 (S2STAT0)                       | 15-31 |

| [7]    | SCI2 Status Register 1 (S2STAT1)                       | 15-34 |

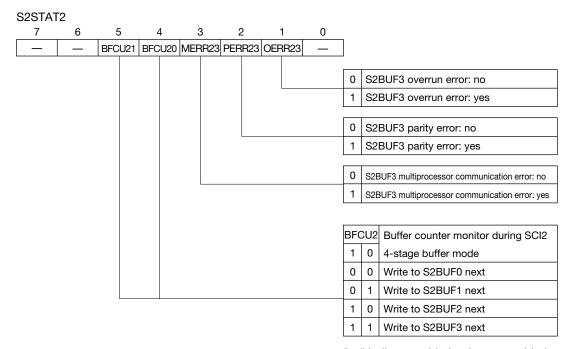

| [8]    | SCI2 Status Register 2 (S2STAT2)                       | 15-36 |

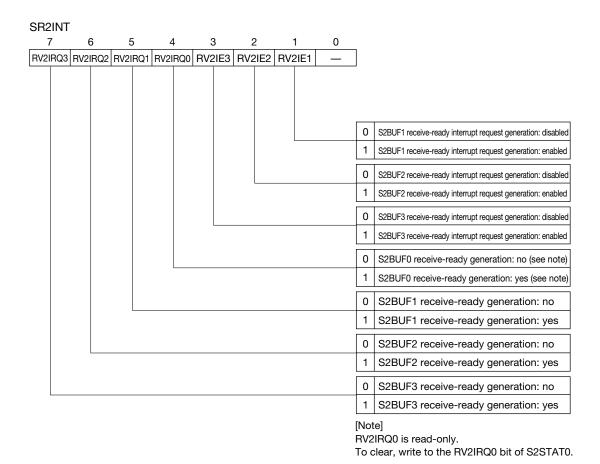

| [9]    | SCI2 Interrupt Control Register (SR2INT)               | 15-38 |

| 15.2.4 | Control Registers for SCI3                             | 15-40 |

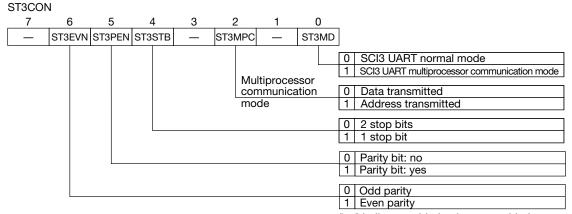

| [1]    | SCI3 Transmit Control Register (ST3CON)                | 15-40 |

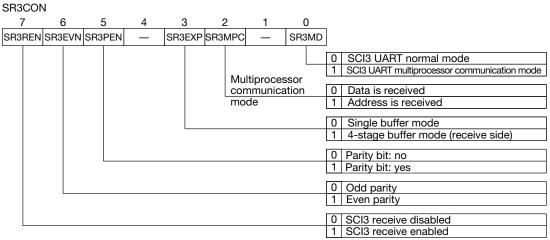

| [2]    | SCI3 Receive Control Register (SR3CON)                 | 15-42 |

| [3]    | SCI3 Transmit/Receive Buffer Register (S3BUF0)         | 15-44 |

| [4]    | SCI3 Receive Buffer Registers (S3BUF1, S3BUF2, S3BUF3) | 15-44 |

| [5]    | SCI3 Transmit and Receive Registers                    | 15-44 |

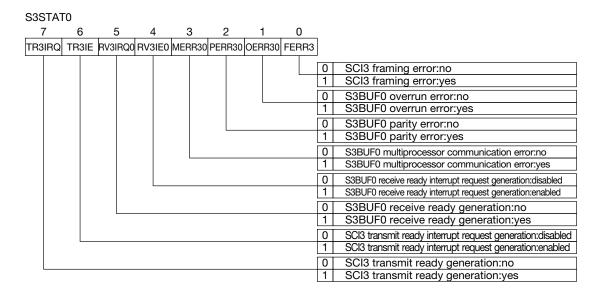

| [6]    | SCI3 Status Register 0 (S3STAT0)                       | 15-45 |

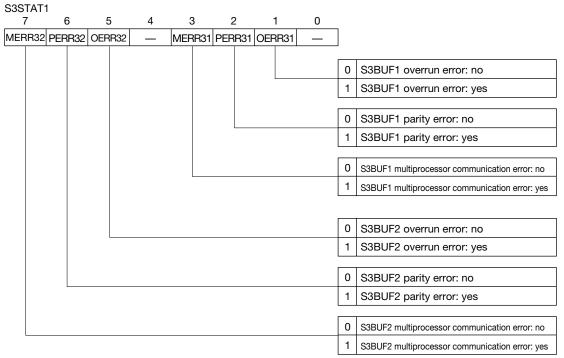

| [7]    | SCI3 Status Register 1 (S3STAT1)                       | 15-48 |

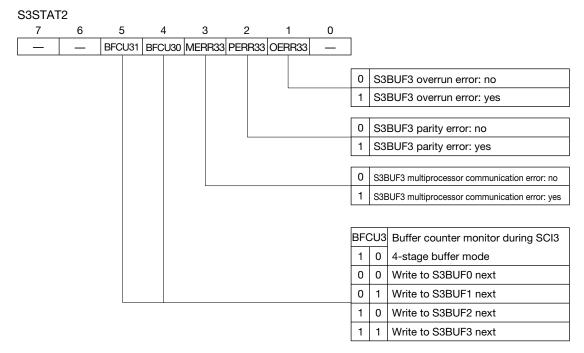

| [8]    | SCI3 Status Register 2 (S3STAT2)                       | 15-50 |

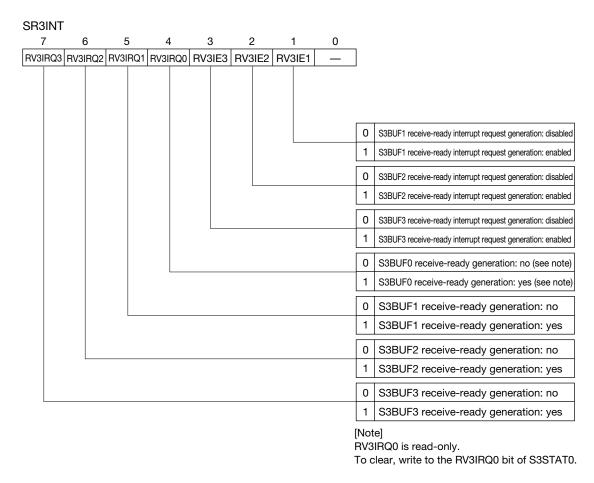

| [9]    | SCI3 Interrupt Control Register (SR3INT)               | 15-52 |

| 15.2.5 | Control Registers for SCI4                             | 15-54 |

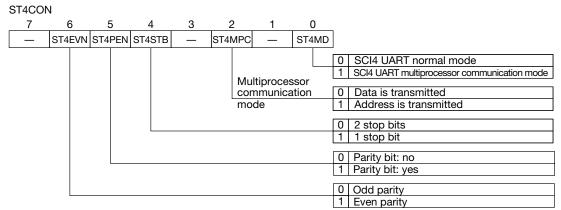

| [1]    | SCI4 Transmit Control Register (ST4CON)                | 15-54 |

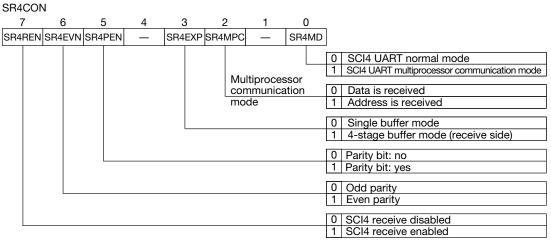

| [2]    | SCI4 Receive Control Register (SR4CON)                 | 15-56 |

| [3]    | SCI4 Transmit/Receive Buffer Register (S4BUF0)         | 15-58 |

| [4]    | SCI4 Receive Buffer Registers (S4BUF1, S4BUF2, S4BUF3) | 15-58 |

| [5]    | SCI4 Transmit and Receive Registers                    | 15-58 |

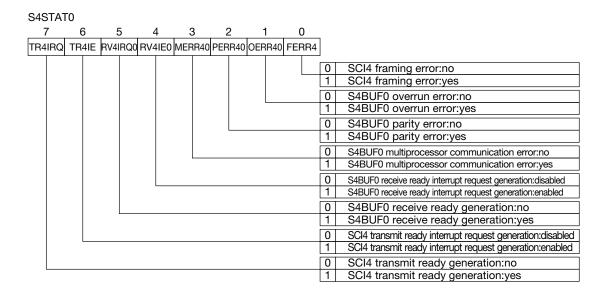

| [6]    | SCI4 Status Register 0 (S4STAT0)                       | 15-59 |

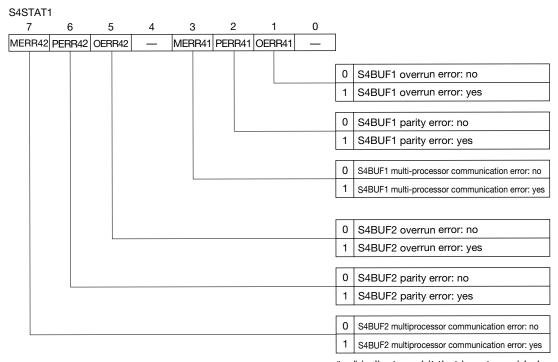

| [7]    | SCI4 Status Register 1 (S4STAT1)                       | 15-62 |

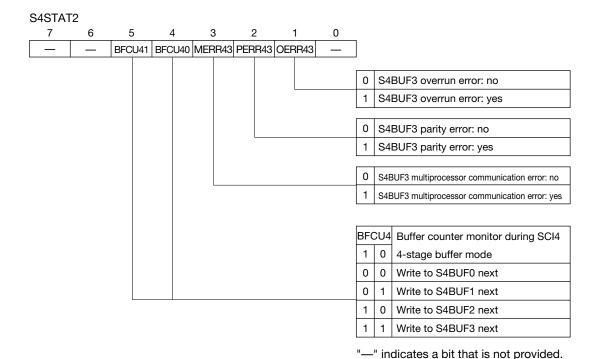

| [8]    | SCI4 Status Register 2 (S4STAT2)                       | 15-64 |

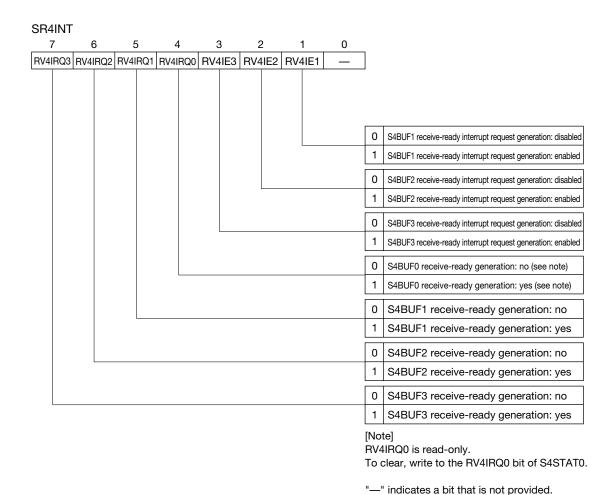

| [9]    | SCI4 Interrupt Control Register (SR4INT)               | 15-66 |

| 15.3 C | Pperation of Serial Ports                              | 15-68 |

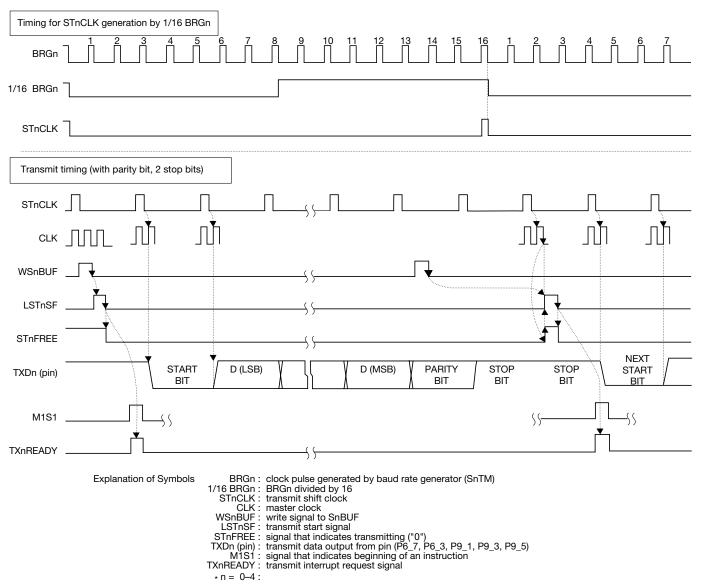

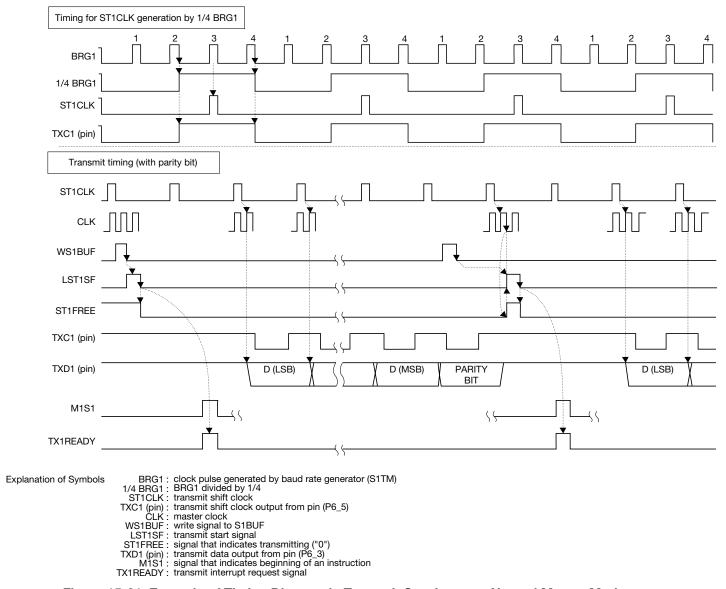

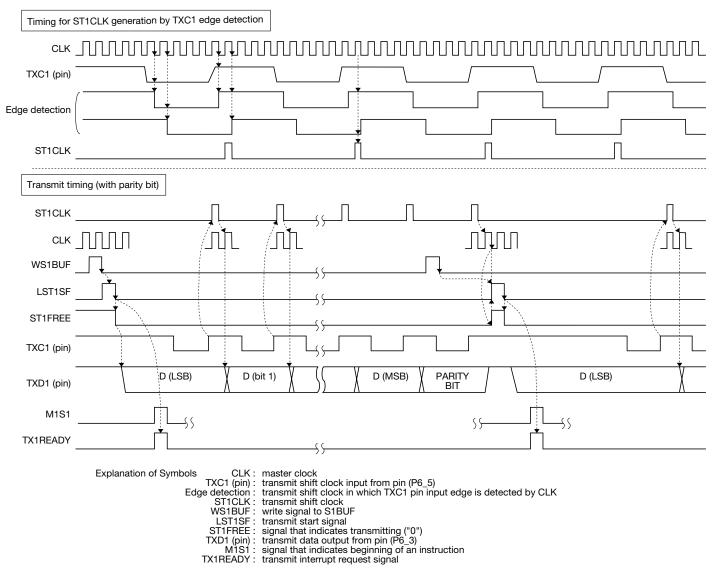

| 15.3.1 | Transmit Operation                                     | 15-68 |

| 15.3.2 | Receive Operation                                      | 15-74 |

| [1]    | Single Buffer Mode                                     | 15-74 |

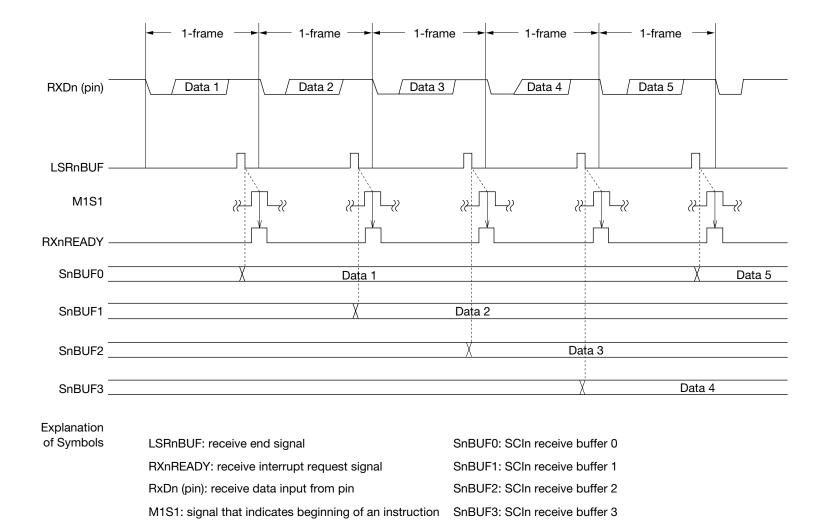

| [2]    | 4-Stage Buffer Mode                                    | 15-81 |

| Chapter 16 | A/D Converter Functions                             |       |

|------------|-----------------------------------------------------|-------|

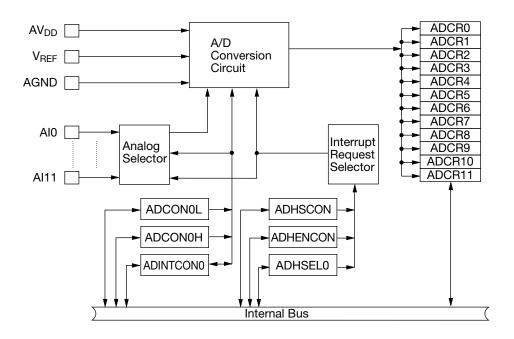

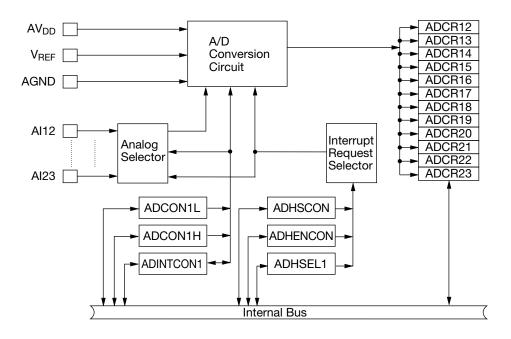

| 16.1 C     | Configuration of A/D Converter                      | 16-4  |

| [1]        | Scan Mode                                           | 16-4  |

| [2]        | Select Mode                                         | 16-4  |

| [3]        | Hard Select Mode                                    | 16-4  |

| 16.2 C     | Control Register of A/D Converter                   | 16-7  |

| [1]        | A/D Control Register 0L (ADCON0L)                   | 16-7  |

| [2]        | A/D Control Register 1L (ADCON1L)                   | 16-9  |

| [3]        | A/D Control Register 0H (ADCON0H)                   | 16-11 |

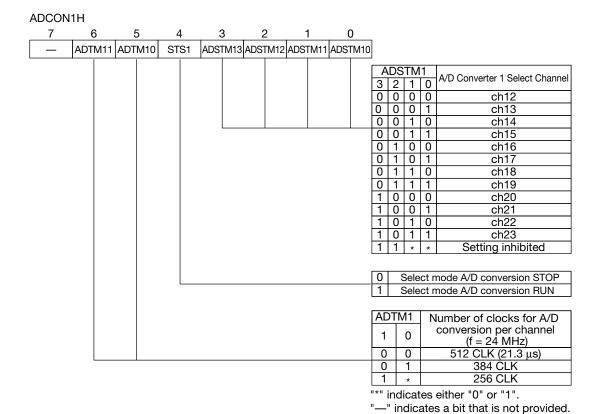

| [4]        | A/D Control Register 1H (ADCON1H)                   | 16-13 |

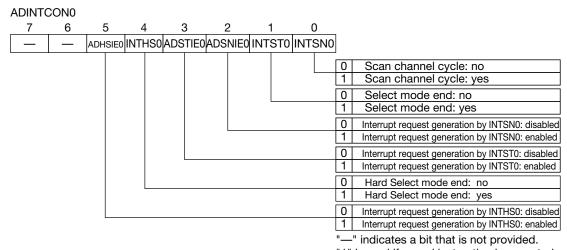

| [5]        | A/D Interrupt Control Register 0 (ADINTCON0)        | 16-15 |

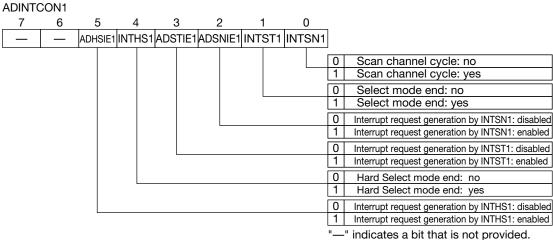

| [6]        | A/D Interrupt Control Register 1 (ADINTCON1)        | 16-17 |

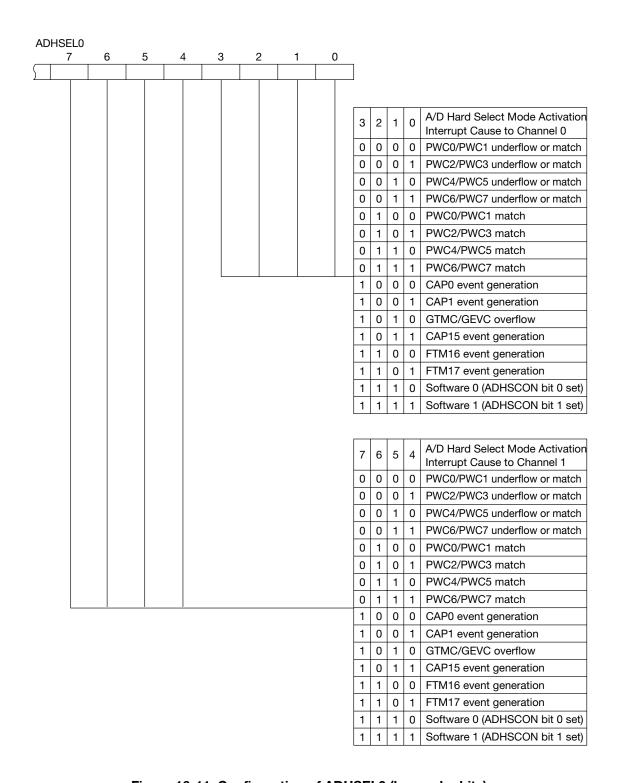

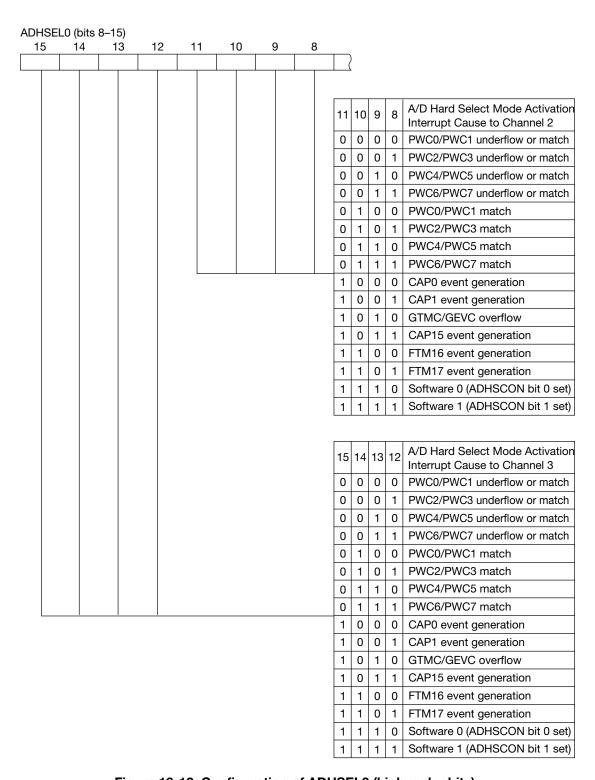

| [7]        | A/D Hard Select Register 0 (ADHSEL0)                | 16-19 |

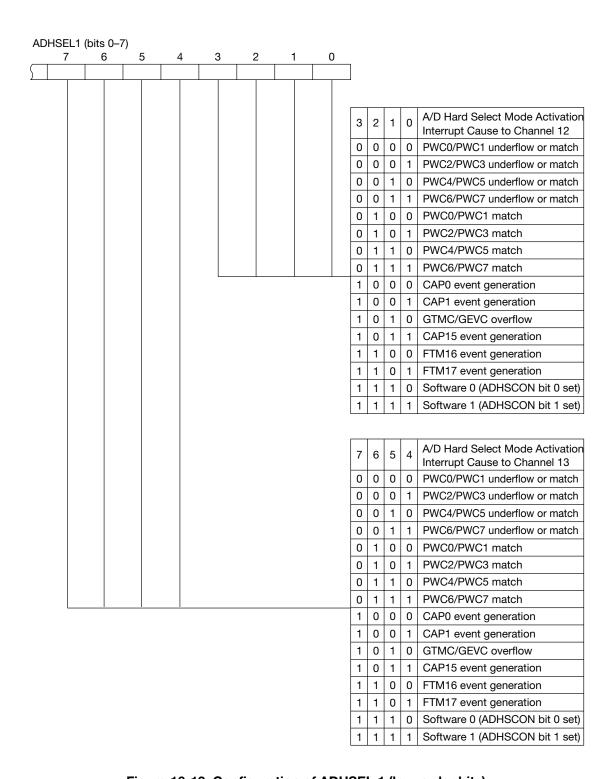

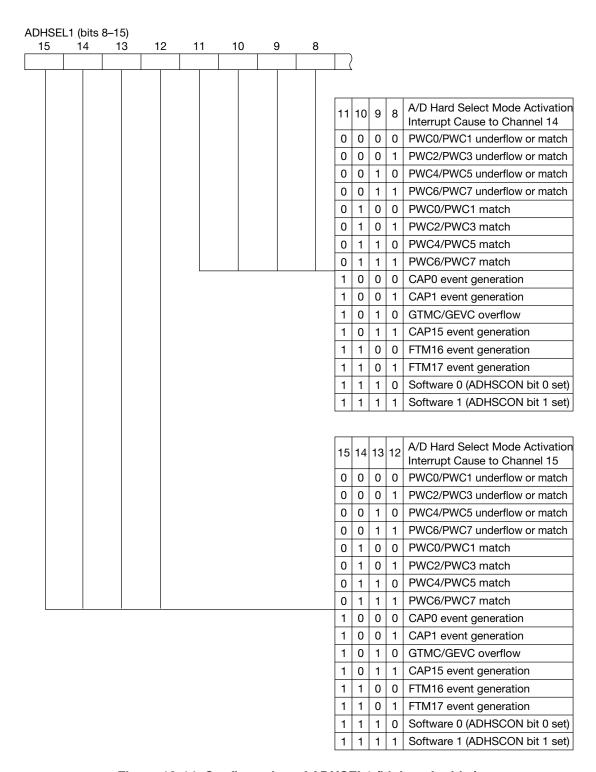

| [8]        | A/D Hard Select Register 1 (ADHSEL1)                | 16-22 |

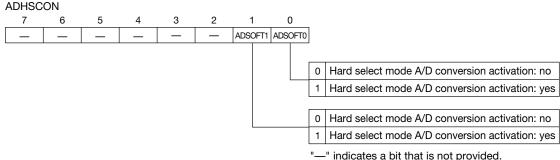

| [9]        | A/D Hard Select Software-Control Register (ADHSCON) | 16-25 |

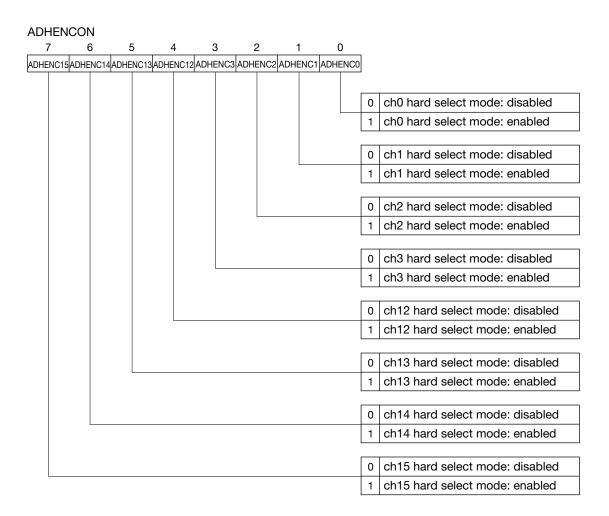

| [10]       | A/D Hard Select Enable Register (ADHENCON)          | 16-26 |

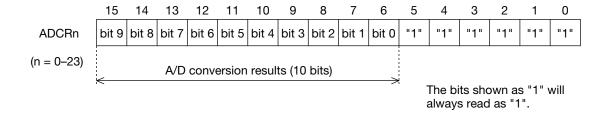

| [11]       | A/D Result Registers (ADCR0-ADCR23)                 | 16-28 |

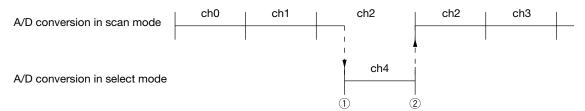

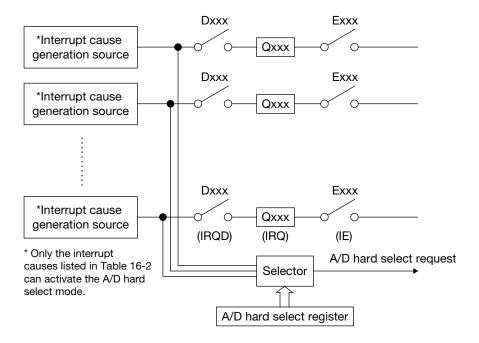

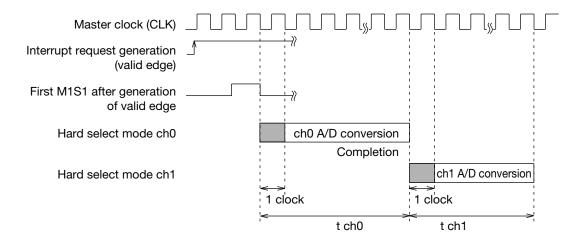

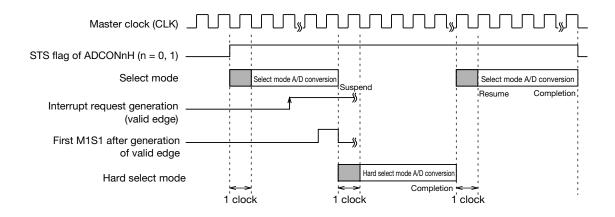

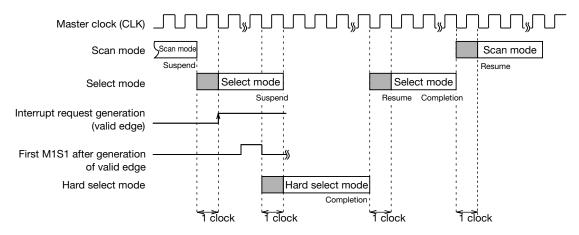

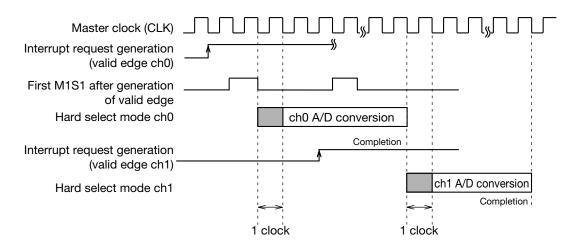

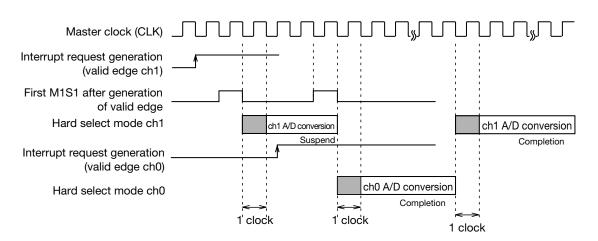

| 16.3       | Generated Timing of the A/D Hard Select Mode        | 16-29 |

|            |                                                     |       |

| Chapter 17 | Transition Detector Functions                       |       |

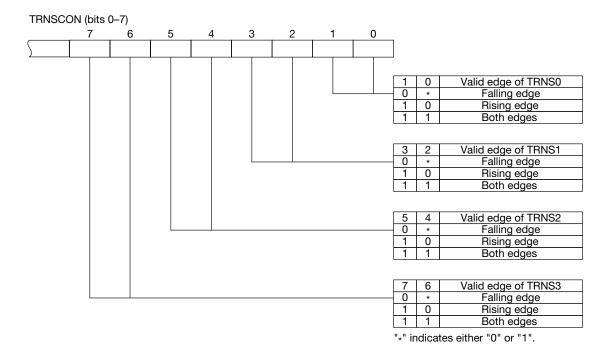

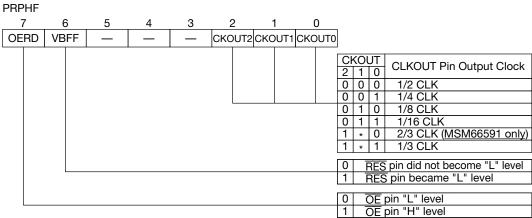

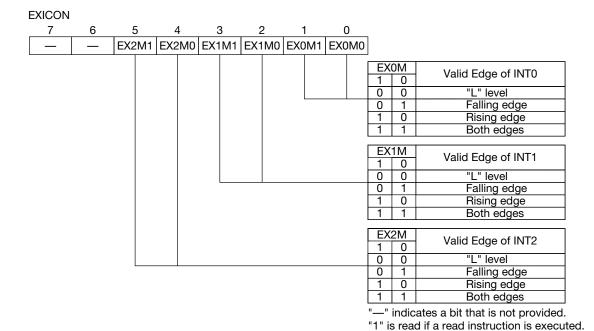

| 17.1 T     | ransition Detector Control Register (TRNSCON)       | 17-1  |

| 17.2 T     | ransition Detector Register (TRNSIT)                | 17-3  |

| Chapter 18 | B Peripheral Functions                              |       |

| •          | •                                                   | 10.4  |

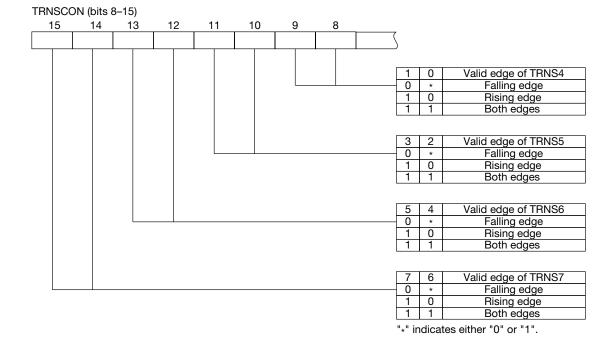

|            | Clockout Function                                   |       |

|            | RES Pin Valid Level Detection Function              |       |

| 18.3 C     | DE Pin Monitor Function                             | 18-1  |

# **Chapter 19 External Interrupt Request Function**

| Chapter 20 Interrupt Request Processing Function                       |        |

|------------------------------------------------------------------------|--------|

| 20.1 Non-maskable Interrupt (NMI)                                      | . 20-2 |

| 20.2 Maskable Interrupt                                                | . 20-4 |

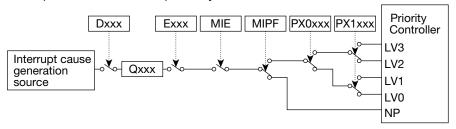

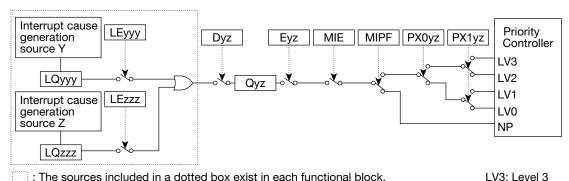

| [1] Interrupt Request Flag Disable Register IRQD                       |        |

| (IRQD0L, IRQD0H, IRQD1L, IRQD1H, IRQD2L)                               | . 20-6 |

| [2] Interrupt Request Register IRQ (IRQ0L, IRQ0H, IRQ1L, IRQ1H, IRQ2L) | . 20-6 |

| [3] Interrupt Enable Register IE (IE0L, IE0H, IE1L, IE1H, IE2L)        | . 20-6 |

| [4] Master Interrupt Enable Flag (MIE)                                 | . 20-6 |

| [5] Master Interrupt Priority Flag (MIPF)                              | . 20-6 |

| [6] Interrupt Priority Control Register                                |        |

| IPX0 (IP00L, IP00H, IP10L, IP10H, IP20L),                              |        |

| IPX1 (IP01L, IP01H, IP11L, IP11H, IP21L)                               | . 20-7 |

| 20.3 Operation of Maskable Interrupt                                   | . 20-8 |

|                                                                        |        |

| Chapter 21 Bus Port Functions                                          |        |

| 21.1 Bus Port (P0, P1, P12_0, P12_1) Functions                         | . 21-1 |

| 21.1.1 Operation of P0, P1, P12_0 and P12_1 During a Program Memory    |        |

| Access                                                                 | . 21-1 |

| 21.2 External Memory Access                                            | . 21-2 |

| 21.2.1 External Program Memory Access                                  | . 21-2 |

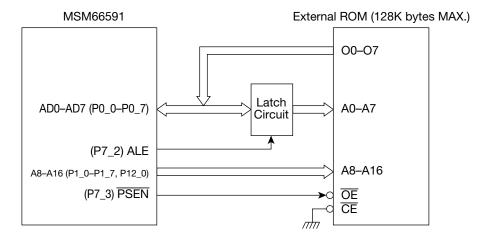

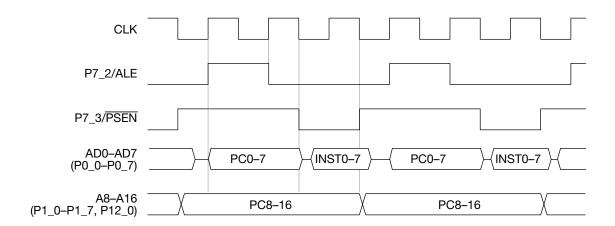

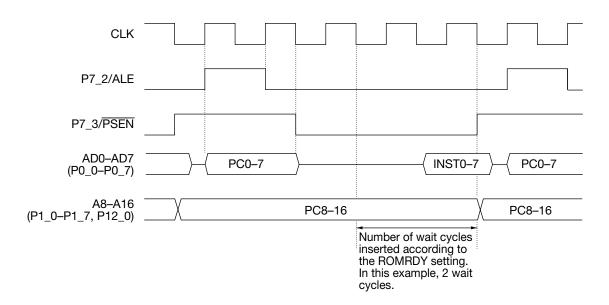

| 21.2.2 External Program Memory Access Timing                           | . 21-2 |

| Chapter 22 Expansion Port                                              |        |

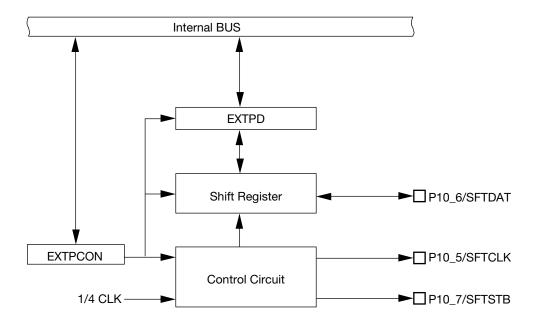

| 22.1 Expansion Port Configuration                                      | . 22-1 |

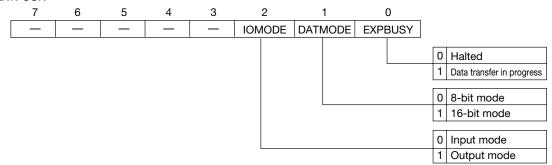

| 22.2 Expansion Port Control Register (EXTPCON)                         | . 22-2 |

| 22.3 Expansion Port Register (EXTPD)                                   |        |

| 22.4 Expansion Port Operation                                          |        |

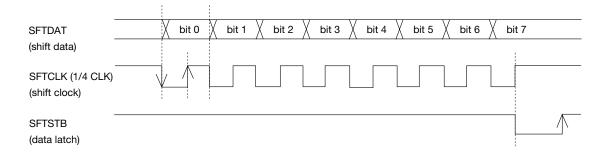

| [1] Input Mode                                                         | . 22-3 |

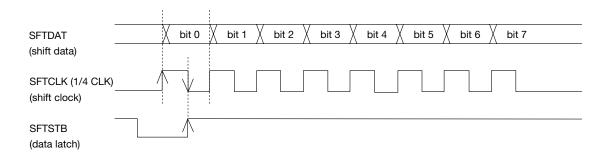

| [2] Output Mode                                                        | . 22-4 |

|                                                                        |        |

| Chapter | 23 Serial Port with FIFO (SCI5)        |       |

|---------|----------------------------------------|-------|

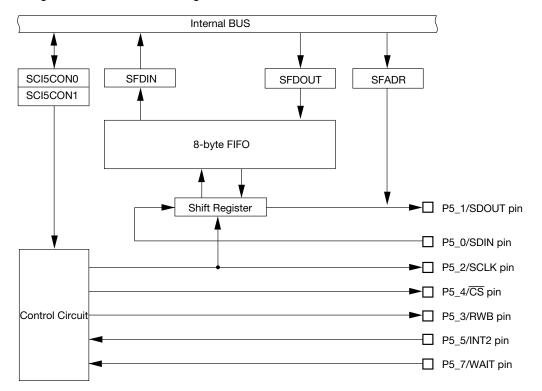

| 23.1    | SCI5 Configuration                     | 23-1  |

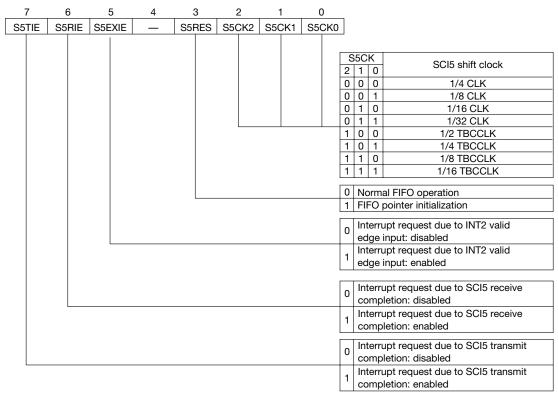

| 23.2    | SCI5 Control Register 0 (SCI5CON0)     | 23-2  |

| 23.3    | SCI5 Control Register 1 (SCI5CON1)     | 23-4  |

| 23.4    | SCI5 Interrupt Register (SCI5INT)      | 23-5  |

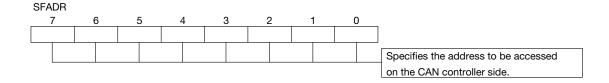

| 23.5    | Serial Address Output Register (SFADR) | 23-6  |

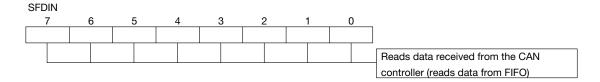

| 23.6    | Serial Data Input Register (SFDIN)     | 23-7  |

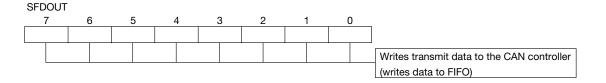

| 23.7    | Serial Data Output Register (SFDOUT)   | 23-7  |

| 23.8    | SCI5 Operation                         | 23-8  |

| Chapter | 24 RAM Monitor Function                |       |

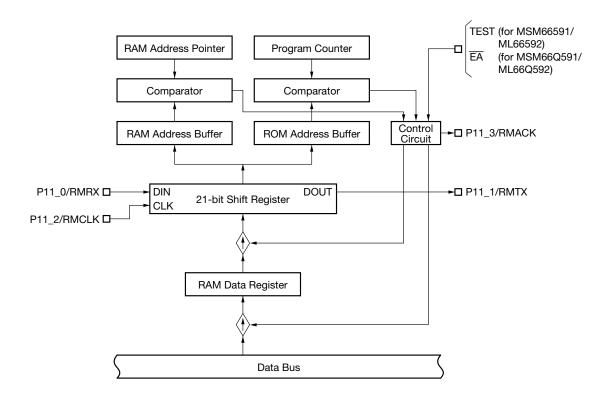

| 24.1    | Configuration of RAM Monitor Function  | 24-1  |

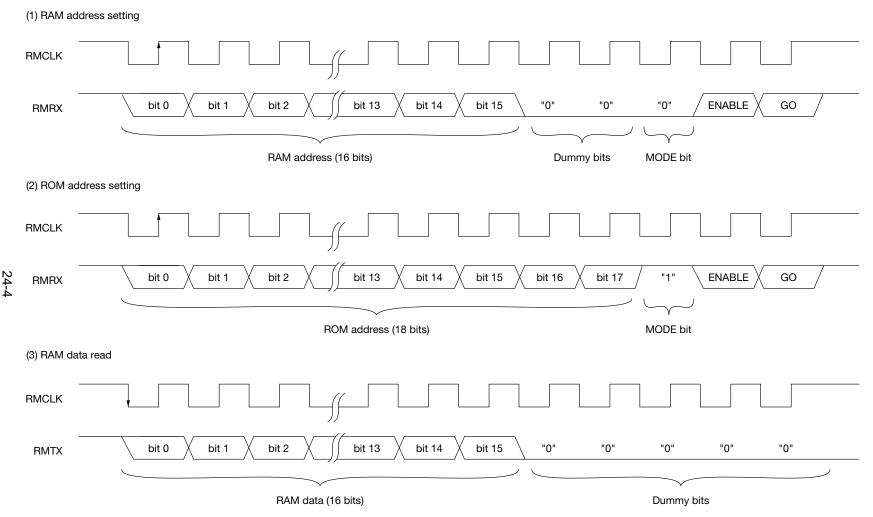

| 24.2    | Configuration of Serial Transfer Data  | 24-3  |

| 24.3    | RAM Monitor Function Operation         | 24-5  |

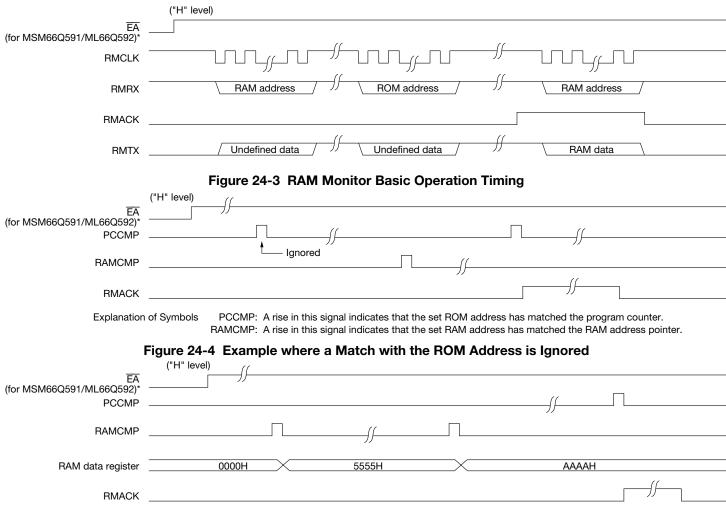

| [       | [1] Setting the addresses              | 24-5  |

| [       | [2] Detection of address matching      | 24-5  |

| [       | [3] Reading data                       | 24-5  |

| Chapter | 25 Electrical Characteristics          |       |

| •       | M66591 Electrical Characteristics]     | 25-1  |

| 25.1    | Absolute Maximum Ratings               |       |

| 25.2    | Operating Range                        |       |

| 25.3    | DC Characteristics                     |       |

| 25.4    | AC Characteristics                     |       |

| [       | [1] External Program Memory Control    | 25-5  |

| 25.5    | A/D Converter Characteristics          |       |

| [ML6    | 6592 Electrical Characteristics]       | 25-8  |

| 25.6    | Absolute Maximum Ratings               | 25-8  |

| 25.7    | Operating Range                        | 25-9  |

| 25.8    | DC Characteristics                     | 25-10 |

| 25.9    | AC Characteristics (Preliminary)       | 25-12 |

| [       | [1] External Program Memory Control    | 25-12 |

| 25.10   | A/D Converter Characteristics          | 25-13 |

|         |                                        |       |

# **Chapter 26 Package Dimensions**

# **Chapter 27 Revision History**

| Chapter 7  | Output Pin Control Pin (OE)           | 7  |

|------------|---------------------------------------|----|

| Chapter 8  | Clock Generation Circuit              | 8  |

| Chapter 9  | Time Base Counter (TBC)               | 9  |

| Chapter 10 | Watchdog Timer (WDT)                  | 10 |

| Chapter 11 | Flexible Timer (FTM)                  | 11 |

| Chapter 12 | General-Purpose 8-Bit Timer Function  | 12 |

| Chapter 13 | PWM Functions                         | 13 |

| Chapter 14 | Baud Rate Generator Functions         | 14 |

| Chapter 15 | Serial Port Functions                 | 15 |

| Chapter 16 | A/D Converter Functions               | 16 |

| Chapter 17 | Transition Detector Functions         | 17 |

| Chapter 18 | Peripheral Functions                  | 18 |

| Chapter 19 | External Interrupt Request Function   | 19 |

| Chapter 20 | Interrupt Request Processing Function | 20 |

| Chapter 21 | Bus Port Functions                    | 21 |

| Chapter 22 | Expansion Port                        | 22 |

| Chapter 23 | Serial Port with FIFO (SCI5)          | 23 |

| Chapter 24 | RAM Monitor Function                  | 24 |

| Chapter 25 | Electrical Characteristics            | 25 |

| Chapter 26 | Package Dimensions                    | 26 |

| Chapter 27 | Revision History                      | 27 |

Chapter 1

Chapter 2

Chapter 3

Chapter 4

Chapter 5

Chapter 6

Overview

Description of Pins

CPU Architecture

Port Functions

**CPU Control Functions**

Memory Control Functions

2

4

5

6

# Chapter 1

# Overview

#### 1. Overview

The MSM66591/ML66592 are high performance 16-bit microcontrollers that contain a 16-bit CPU (nX-8/500S), ROM, RAM, a 10-bit A/D converter, serial ports, flexible timers, and PWMs.

The ML66592 is the same as the MSM66591 with the exception that the ML66592 has an increased ROM and RAM capacity and a higher operating speed. Table 1-1 lists the functional differences between the MSM66591 and ML66592.

The MSM66Q591 is a Flash EEPROM version of the MSM66591. The ML66Q592 is a Flash EEPROM version of the ML66592.

Table 1-1 Differences between MSM66591/66Q591 and ML66592/66Q592 Specifications

| Item                                                                                              | MSM66591/66Q591                  | ML66592/66Q592                                                       | Modifications in<br>ML66592/ML66Q592 and notes                                                                                                    |

|---------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating frequency (internal)                                                                    | 20 to 24 MHz                     | 20 to 28 MHz                                                         | Increased by 4 MHz (with increased supply current)                                                                                                |

| Operating temperature                                                                             | –40 to +115°C                    | -40 to +95°C                                                         | Changed from +115°C to +95°C                                                                                                                      |

| Program memory space                                                                              | 128K bytes<br>0:0000H to 1:FFFFH | 192K bytes (internal)<br>256K bytes (external)<br>0:0000H to 3:FFFFH | Increased by 64K bytes (internal) (SEG2) Increased by 128K bytes (external) (SEG2, 3) External A17 output (P12_1) has been added. (When EA = "L") |

| Data memory space                                                                                 | 6K bytes<br>200H to 19FFH        | 8K bytes<br>200H to 21FFH                                            | Increased by 2K bytes<br>(1A00H to 21FFH)                                                                                                         |

| Internal ROM capacity                                                                             | 128K bytes<br>0:0000H to 1:FFFFH | 192K bytes<br>0:0000H to 2:FFFFH                                     | Increased by 64K bytes (SEG2) One valid bit has been added to each of CSR and TSR. Access forbidden to the internal SEG3.                         |

| Internal RAM capacity                                                                             | 6K bytes<br>200H to 19FFH        | 8K bytes<br>0200H to 21FFH                                           | Increased by 2K bytes<br>(1A00H to 21FFH)                                                                                                         |

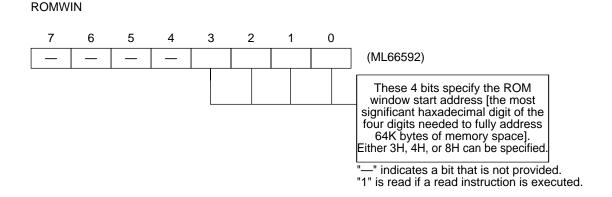

| Starting address for the ROM Window function                                                      | 2000H                            | 3000H                                                                | Changed from 2000H to 3000H                                                                                                                       |

|                                                                                                   | 4000H                            | 4000H                                                                |                                                                                                                                                   |

|                                                                                                   | 8000H                            | 8000H                                                                |                                                                                                                                                   |

|                                                                                                   | 1/2 CLK (12 MHz)                 | 1/2 CLK (14 MHz)                                                     |                                                                                                                                                   |

| CLKOUT function                                                                                   | 1/4 CLK (6 MHz)                  | 1/4 CLK (7 MHz)                                                      |                                                                                                                                                   |

| (Values in parentheses are output frequencies of the                                              | 1/8 CLK (3 MHz)                  | 1/8 CLK (3.5 MHz)                                                    |                                                                                                                                                   |

| device operating at the maximum frequency)                                                        | 1/16 CLK (1.5 MHz)               | 1/16 CLK (1.75 MHz)                                                  |                                                                                                                                                   |

| maximum requericy)                                                                                | 2/3 CLK (16 MHz)                 | 2/3 CLK (forbidden)                                                  | Use of 2/3 CLK is forbidden.                                                                                                                      |

|                                                                                                   | 1/3 CLK (8 MHz)                  | 1/3 CLK (9.3 MHz)                                                    |                                                                                                                                                   |

| 10-bit A/D converter conversion time                                                              | 512 CLK (21.3 μs)                | 512 CLK (18.3 μs)                                                    | Should be used at 16 μs or more                                                                                                                   |

| (Values in parentheses are conversion time when the device is operating at the maximum frequency) | 384 CLK (16 μs)                  | 384 CLK (13.7μs)                                                     |                                                                                                                                                   |

|                                                                                                   | 256 CLK (10.7 μs)                | 256 CLK (9.1 μs)                                                     |                                                                                                                                                   |

| Transfer clock during                                                                             | 1/4 CLK (6 MHz*)                 | Not provided                                                         | 1/4 CLK has been deleted.                                                                                                                         |

| Flash ROM reprogramming in the user mode                                                          | 1/8 CLK (3 MHz)                  | 1/8 CLK (3.5 MHz)                                                    | * 6 MHz is outside the guarantee range.                                                                                                           |

| (MSM66Q591/ML66Q592 only)                                                                         | 1/16 CLK (1.5 MHz)               | 1/16 CLK (1.75 MHz)                                                  | 90.                                                                                                                                               |

Note: In the ML66592/66Q592, the AC characteristics during external program memory access apply only when the internal operating frequency is not more than 24 MHz.

#### 1.1 Features

#### [1] Abundant Instruction Set

- Instruction set has superb orthogonal capability

- 8/16-bit arithmetic instructions

- Multiplication/division instructions

- Bit operation instructions

- Bit logic operation instructions

- ROM table reference instructions

#### [2] Abundant Addressing Modes

- · Register addressing

- · Page addressing

- · Pointing register indirect addressing

- Stack addressing

- · Immediate addressing

#### [3] Minimum Instruction Cycle

MSM66591: 83.3 nsec @ 12 MHz (internal: 24 MHz) ML66592: 71.4 nsec @ 14 MHz (internal: 28 MHz)

#### [4] Program Memory (ROM)

MSM66591: Internal: 128K bytes

External: 128K bytes, EA pin active

ML66592: Internal: 192K bytes

External: 256K bytes (EA pin active)

#### [5] Data memory (RAM)

MSM66591: Internal: 6K bytes ML66592: Internal: 8K bytes

#### [6] I/O Ports

Analog input ports: 24

• I/O ports: 98

#### [7] Multiplier

MSM66591: MUL ERn instruction: 208 nsec @ 12 MHz ML66592: MUL ERn instruction: 178.6 nsec @ 14 MHz

- [8] Flexible Timer

- Freerun counter: 20-bit × 1, 16-bit × 1

- Capture register with divider: 6

- Double-buffer realtime output: 10

- Multifunction timer: 2

- [9] General-Purpose 8-Bit Timers

- General-purpose 8-bit timer: 1

- 8-bit event counter: 1

- [10] 16-Bit PWM: 12

- [11] 8-Bit Serial Ports

- UART with BRG (provided with a 4-stage buffer on the receive side): 4

- UART/synchronous type with BRG: 1

- Synchronous (with 8-byte FIFO): 1

- [12] A/D Converter

- 10-bit resolution: 24 channels (12-channel × 2)

- [13] Transition Detector: 8

- [14] Watchdog Timer: 1

- [15] Expansion Port (serial-parallel conversion): 1

- [16] Interrupts

- Non-maskable: 1

- Maskable internal: 63/external: 3 (38 vectors)

- · 4-level priority

- [17] ROM Window Functions

- [18] RAM Monitor Functions

- [19] Standby Modes

- HALT mode

- STOP mode

- [20] Clock Multiplier (2x original oscillation clock)

- [21] Package

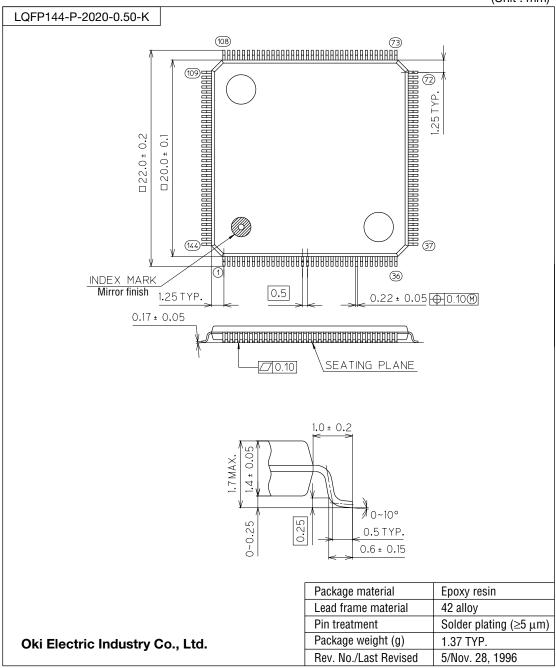

- 144-pin plastic LQFP (LQFP144-P-2020-0.50-K)

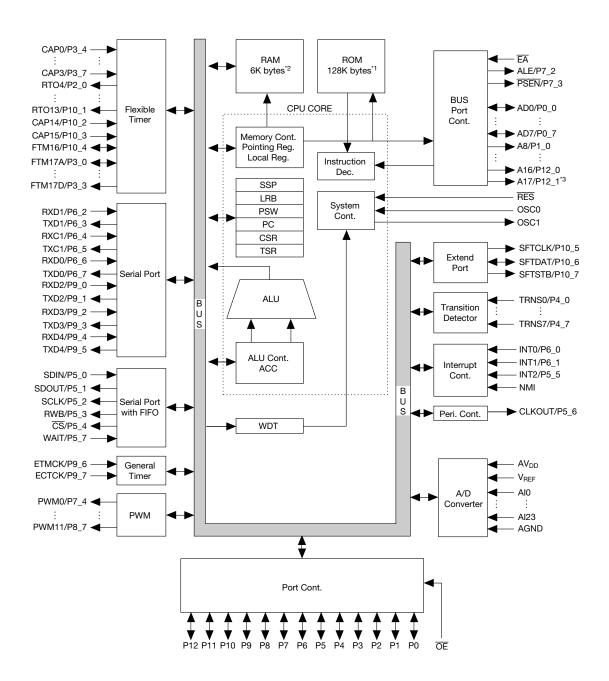

#### 1.2 Block Diagram

<sup>\*1 192</sup>K bytes for the ML66592/66Q592

<sup>\*2 8</sup>K bytes for the ML66592/66Q592

<sup>\*3</sup> For the ML66592/66Q592 only

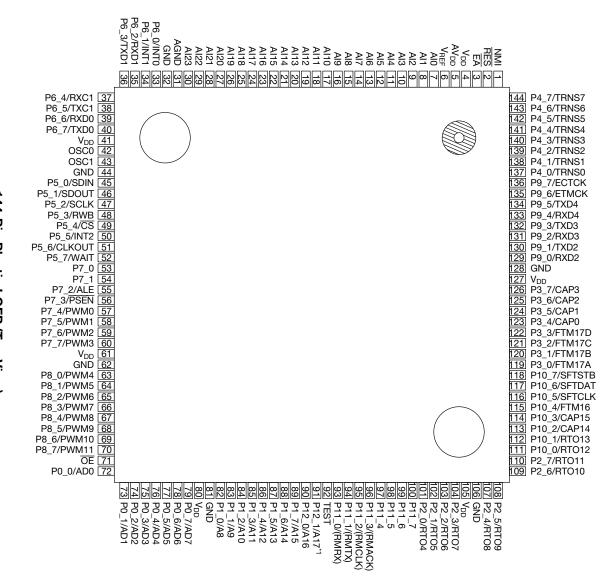

# 1.3 Pin Configuration

144-Pin Plastic LQFP (Top View)

For the ML66592/66Q592 only

Note: For the package dimensions, see Chapter 26. For handling of unused pins, see Section 2.27

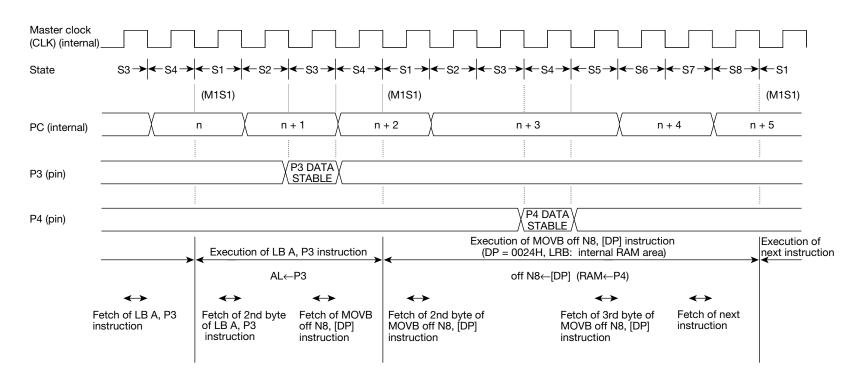

#### 1.4 Basic Operation Timing

The MSM66591/ML66592 utilize the Oki-original 16-bit CPU core (nX-8/500S).

With the nX-8/500S, the basic instruction code unit is 8 bits, and instructions are 1 byte to 6 bytes long. Instructions are classified as either NATIVE instructions for frequent operation or COMPOSIT instructions to realize a wide addressing range.

NATIVE instructions consist of 1 to 4 bytes and achieve high code efficiency and high processing efficiency.

COMPOSIT instructions consist of a 1- to 3-byte address specification field (PREFIX) and a 1- to 3-byte operation specification field (SUFFIX). A wide addressing range can be realized by combining the PREFIX and SUFFIX.

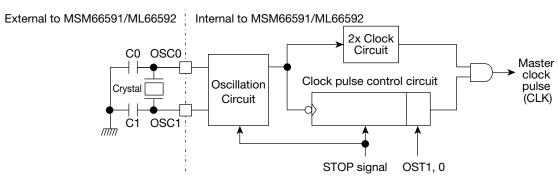

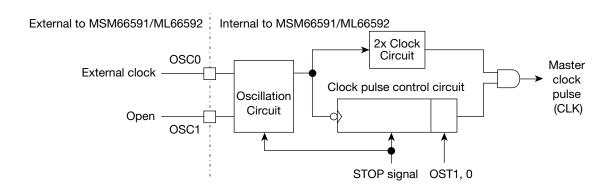

The MSM66591/ML66592 multiply the original oscillation clock by a factor of 2 to generate the master clock pulse (CLK). One master clock pulse (CLK) forms one state. In other words, one state is 41.7 nsec (@ 12 MHz) for the MSM66591 or 35.7 nsce (@ 14 MHz) for the ML66592. The execution of a single instruction is performed over several states (S2, S3, ...Sn).

The number of states required for instruction execution depends upon the instruction. The minimum is 2 states and the maximum is 48 states. (For details, refer to the "nX-8/500S Core Instruction Manual.")

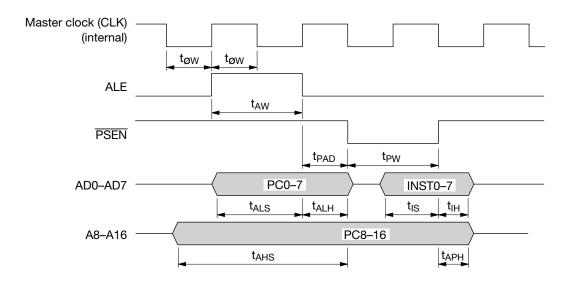

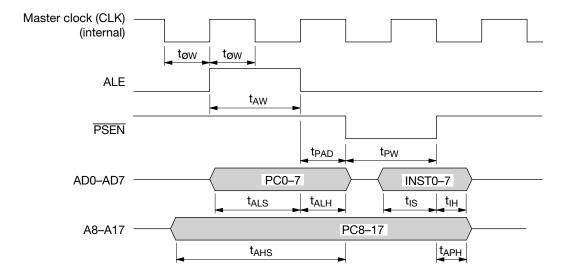

Figures 1-1 through 1-4 show examples of the basic timing.

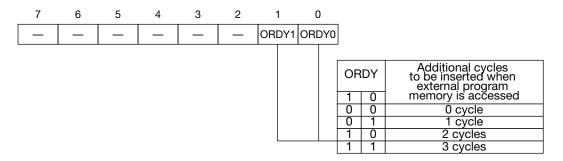

In the case of external program memory access (EA pin = "L" level), 1 cycle (= 1 state) is automatically inserted for a 1 byte read (fetch) operation. In addition, the number of wait cycles (0 to 3 cycles) specified by the ROM ready control register (ROMRDY) are also inserted.

For further details regarding external memory access timing, see Chapter 21, "Bus Port Functions".

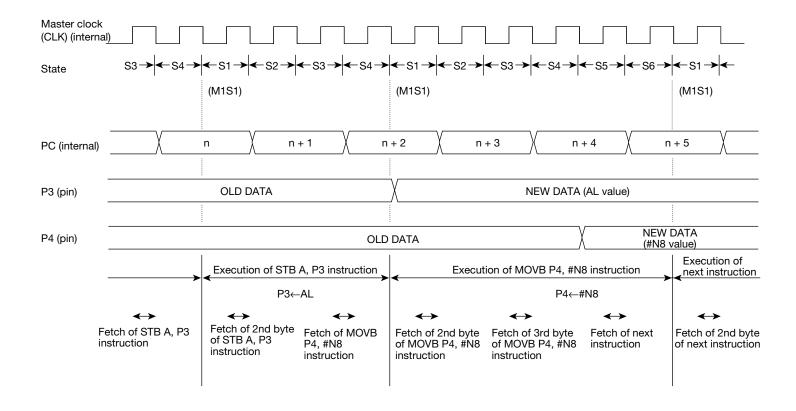

Figure 1-1 Basic Operation Timing Example (Input of Port Data)

Figure 1-2 Basic Operation Timing Example (Output to Port)

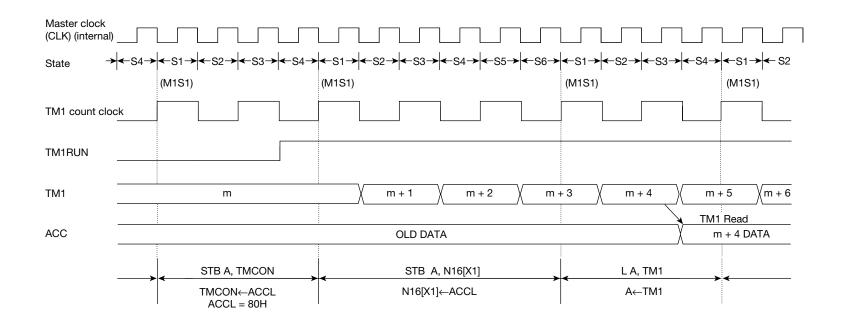

- The timing for the RUN bit that becomes "1" differs depending on the instruction executed.

- The timing to read TM1 differs, depending on the instruction executed.

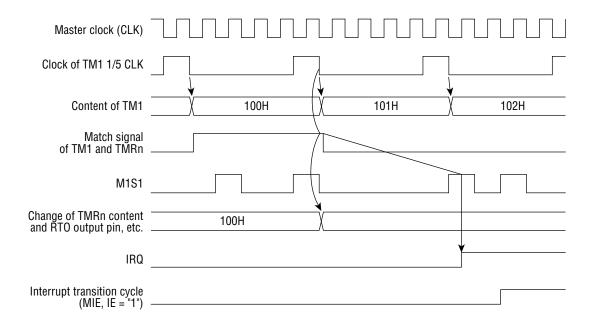

- The count timing of TM1 differs, depending on the selected clock of TM1.

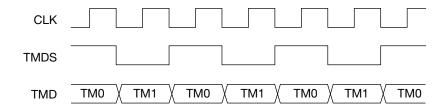

Figure 1-3 TM1 Operation Timing

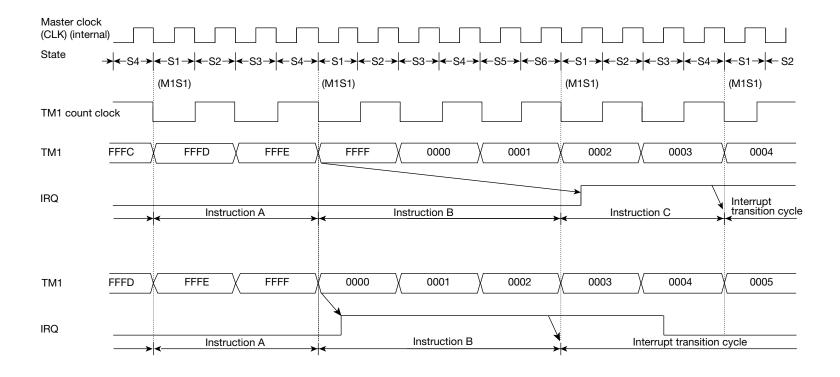

- The interrupt transition cycle has 14 cycles. However, it has 17 cycles if the program memory space is extended to 128K bytes.

- IRQ is reset ("0") at the 3rd cycle of the interrupt transition cycle.

**Figure 1-4 Interrupt Transition Timing Example**

# **Description of Pins**

## 2. Desacacription of Pins

Chapter 2 describes each pin of the MSM66591/ML66592.

For handling of unused pins, see Section 2.27.

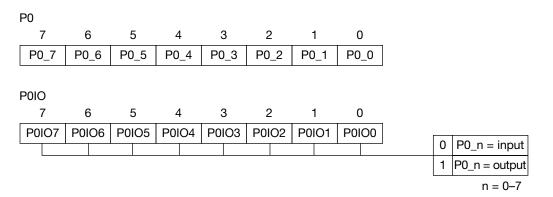

#### 2.1 P0\_0-P0\_7: Input/Output Pins

8-bit I/O pins of Port 0. I/O can be specified in bit units by the Port 0 mode register (P0IO).

If the  $\overline{EA}$  pin is set to "L" level, these pins automatically function as time-shared address output and data I/O pins (AD0–AD7) for external program memory access.

At reset (when the  $\overline{\text{RES}}$  signal is input, the BRK instruction is executed, the watchdog timer (WDT) is overflown, or an operation code trap is generated), P0 becomes a high impedance input.

When Port 0 is in output status, "H" or "L" level is output if the  $\overline{OE}$  pin (pin 71) is in "L" level, but Port 0 goes into high impedance status if the  $\overline{OE}$  pin is in "H" level.

#### 2.2 P1 0-P1 7: Input/Output Pins

8-bit I/O pins of Port 1. I/O can be specified in bit units by the Port 1 mode register (P1IO).

By setting the  $\overline{EA}$  pin to "L" leve, P1\_0–P1\_7 also function as output pins for internal operations (secondary function).

<Description of Secondary Functions of Each Pin>

• A8-A15 (P1\_0-P1\_7)

If the externally expanded data memory is accessed with the  $\overline{EA}$  pin in "L" level, these pins function as output pins to output addresses A8–A15.

At reset (when the RES signal is input, the BRK instruction is executed, the watchdog timer is overflown, or an operation code trap is generated), P1 becomes high impedance input.

When Port 1 is in output status, "H" or "L" level is output if the  $\overline{OE}$  pin (pin 71) is in "L" level, but Port 1 goes into high impedance status if the  $\overline{OE}$  pin is in "H" level.

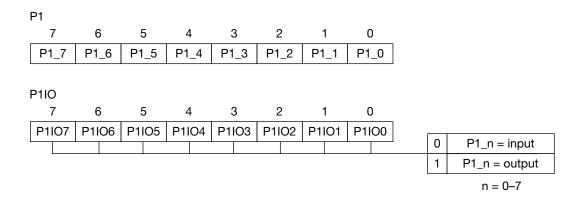

#### 2.3 P2 0-P2 7: Input/Output Pins

8-bit I/O pins of Port 2. I/O can be specified in bit units by the Port 2 mode register (P2IO).

P2\_0-P2\_7 also function as output pins for internal operations (secondary function). The secondary functions for P2\_0-P2\_7 are set in bit units by the Port 2 secondary function control register (P2SF).

For the pins that have secondary functions set by P2SF, I/O settings by P2IO become invalid.

<Description of the Secondary Functions of Each Pin>

• RTO4 (P2 0)-RTO11 (P2 7)

The preset level is output when the value of registers 4–11 (TMR4–TMR11) of the flexible timer match the selected counter values.

At reset (when the  $\overline{\text{RES}}$  signal is input, the BRK instruction is executed, the watchdog timer is overflown, or an operation code trap is generated), P2 becomes a high impedance input.

When Port 2 is in output status, "H" or "L" level is output if the  $\overline{OE}$  pin (pin 71) is in "L" level. If the  $\overline{OE}$  pin is in "H" level, Port 2 goes into high impedance status.

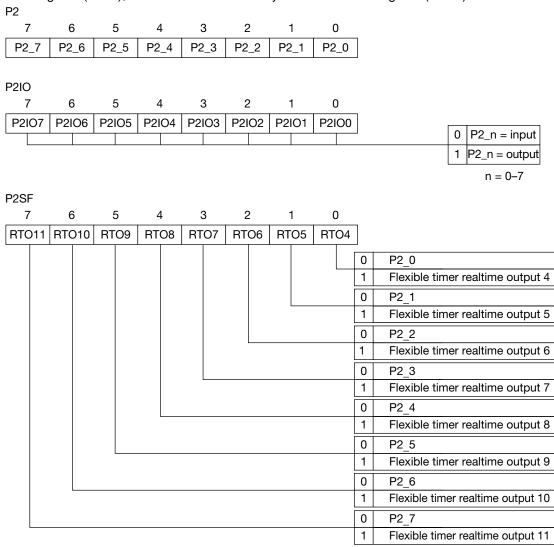

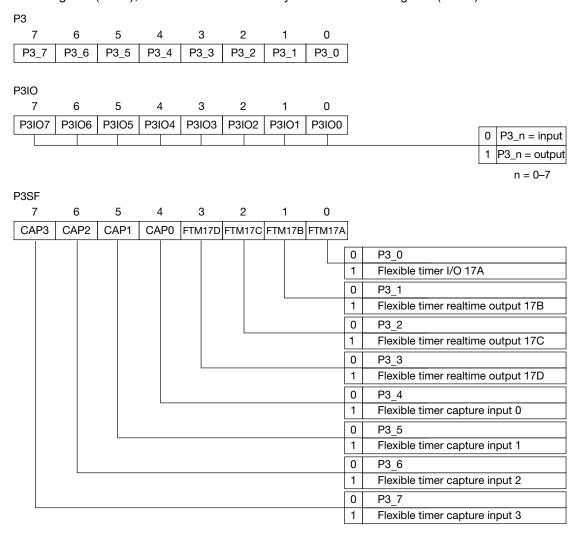

#### 2.4 P3\_0-P3\_7: Input/Output Pins

8-bit I/O pins of Port 3. I/O can be specified in bit units by the Port 3 mode register (P3IO).

P3\_0-P3\_7 also function as I/O pins for internal operations (secondary function).

Secondary functions for P3\_0-P3\_7 are set in bit units by the Port 3 secondary function control register (P3SF). For the pins that have secondary functions set by P3SF, I/O settings by P3IO become invalid.

<Description of Secondary Functions of Each Pin>

• FTM17A (P3 0)

When register 17 (TMR17) of the flexible timer is in RTO mode, and when the value of the TMR17 matches the selected counter value, the preset level is output.

When the TMR17 is in CAP mode, FTM17A is set to input pin status. If the specified edge is input to this pin, the selected counter value is input to the TMR17.

• FTM17B (P3\_1)-FTM17D (P3\_3)

When the TMR17 is in 4-port output RTO mode, and when the value of the TMR17 matches the selected counter value, the preset level is output.

CAP0 (P3 4)—CAP3 (P3 7)

If the edge specified to this pin is input for a specified number of times, the selected counter value is input to timer registers 0–3 (TMR0–TMR3).

At reset (when the  $\overline{\text{RES}}$  signal is input, the BRK instruction is executed, the watchdog timer is overflown, or an operation code trap is generated), P3 becomes a high impedance input.

When P3\_0–P3\_3 are in output status, "H" or "L" level is output if the  $\overline{OE}$  pin (pin 71) is in "L" level. If the  $\overline{OE}$  pin is in "H" level, they go into high impedance status.

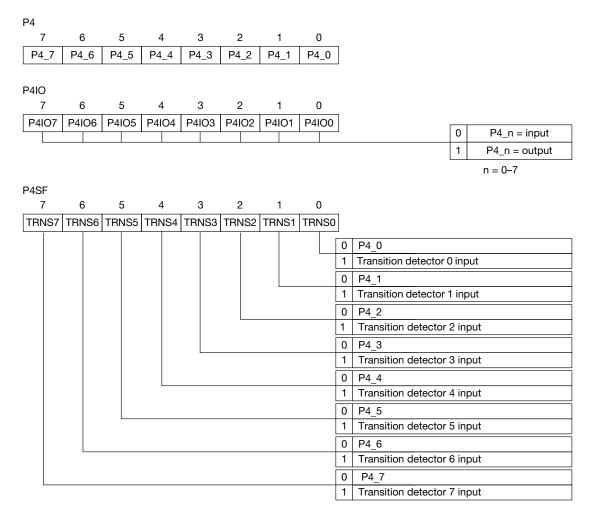

#### 2.5 P4 0-P4 7: Input/Output Pins

8-bit I/O pins of Port 4. I/O can be specified in bit units by the Port 4 mode register (P4IO).

P4\_0-P4\_7 also function as input pins for internal operations (secondary function).

Secondary functions for P4\_0-P4\_7 are set in bit units by the Port 4 secondary function control register (P4SF).

For the pins that have secondary functions set by P4SF, I/O settings by P4IO become invalid.

<Description of Secondary Functions of Each Pin>

TRNS0 (P4\_0)-TRNS7 (P4\_7)

Input pins of transition detectors 0-7.

At reset (when the  $\overline{\text{RES}}$  signal is input, the BRK instruction is executed, the watchdog timer is overflown, or an operation code trap is generated), P4 becomes a high impedance input.

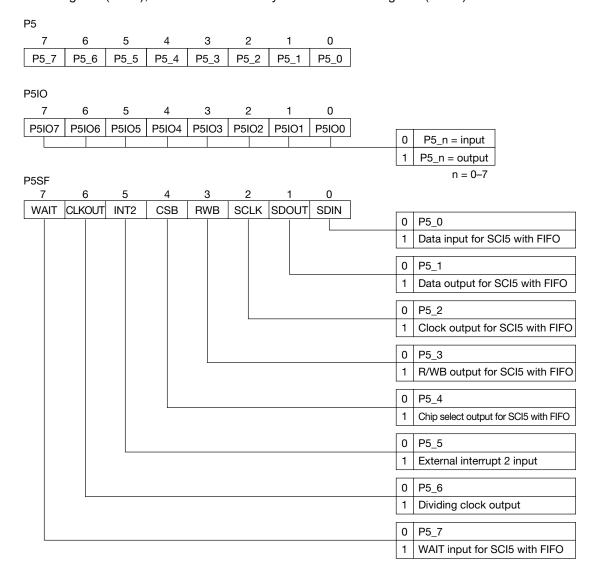

#### 2.6 P5\_0-P5\_7: Input/Output Pins

8-bit I/O pins of Port 5. I/O can be specified in bit units by the Port 5 mode register (P5IO).

P5 0-P5 7 also function as output pins for internal operations (secondary function).

Secondary functions for P5\_0–P5\_7 are set in bit units by the Port 5 secondary function control register (P5SF). For the pins that have secondary functions set by P5SF, I/O settings by P5IO become invalid.

<Description of Secondary Functions of Each Pin>

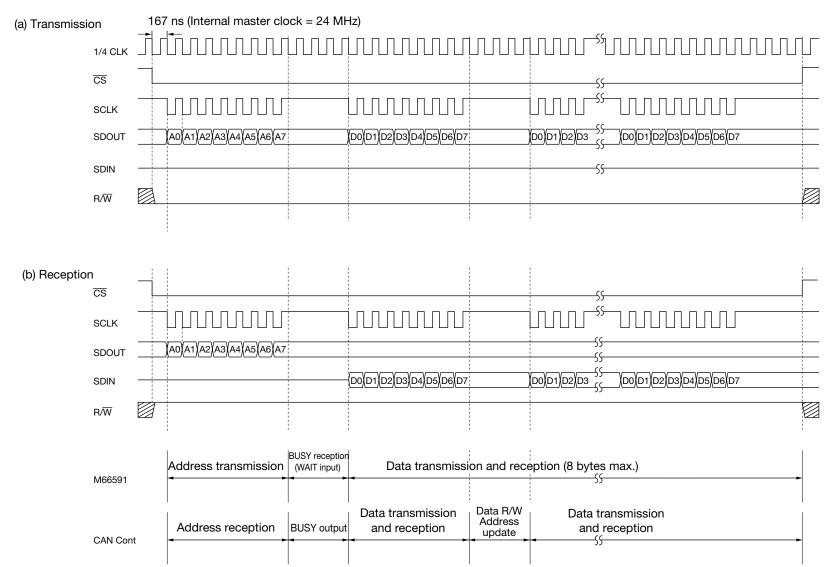

• SDIN (P5\_0)

Data input pin of serial port 5 (synchronous SCI with FIFO)

• SDOUT (P5\_1)

Data output pin of serial port 5 (synchronous SCI with FIFO)

• SCLK (P5 2)

Synchronous clock output pin of serial port 5 (synchronous SCI with FIFO)

• R/W (P5 3)

Data read/write switch signal output pin of serial port 5 (synchronous SCI with FIFO)

•  $\overline{\text{CS}}$  (P5 4)

Chip select signal output pin of serial port 5 (synchronous SCI with FIFO)

• INT2 (P5\_5)

Dual function interrupt and external interrupt 2 input pin of serial port 5 (synchronous SCI with FIFO)

• CLKOUT (P5\_6)

Output pin that outputs clock pulses specified by the peripheral control register (PRPHF)

• WAIT (P5\_7)

BUSY signal input pin of serial Port 5 (synchronous SCI with FIFO)

At reset (when the  $\overline{\text{RES}}$  signal is input, the BRK instruction is executed, a watchdog timer is overflown, or an operation code trap is generated), P5 becomes a high impedance input.

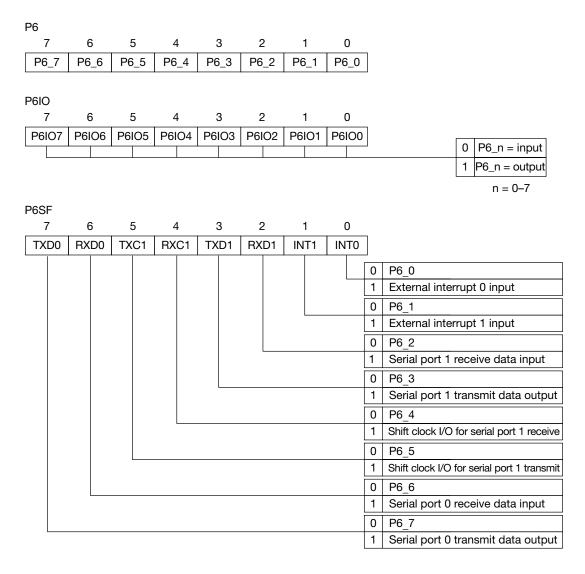

#### 2.7 P6\_0-P6\_7: Input/Output Pins

8-bit pins of Port 6. I/O can be specified in bit units by the Port 6 mode register (P6IO).

P6 0-P6 7 also function as I/O pins for internal operations (secondary function).

Secondary functions for P6\_0–P6\_7 are set in bit units by the Port 6 secondary function control register (P6SF).

For pins that have secondary functions set by P6SF, I/O settings by P6IO become invalid.

<Description of Secondary Functions of Each Pin>

- INT0 (P6\_0), INT1 (P6\_1)

Input pins for external interrupts 0 and 1.

- RXD1 (P6 2)

Input pin to input receive data at the serial port 1 receive side.

• TXD1 (P6\_3)

Output pin to output transmit data at the serial port 1 transmit side.

RXC1 (P6\_4)

Configured to be the output pin for the shift clock if the serial port 1 receive side is in synchronous and master mode, and configured to be the input pin of the shift clock if the receive side is in slave mode.

• TXC1 (P6 5)

Becomes the output pin of the shift clock if the serial port 1 transmit side is in synchronous mode and master mode, and becomes the input pin of the shift clock if in slave mode.

RXD0 (P6 6)

Input pin to input receive data at the serial port 0 receive side.

• TXD0 (P6 7)

Output pin to output transmit data at the serial port 0 transmit side.

At reset (when the  $\overline{\text{RES}}$  signal is input, the BRK instruction is executed, the watchdog timer is overflown, or an operation code trap is generated), P6 becomes a high impedance input.

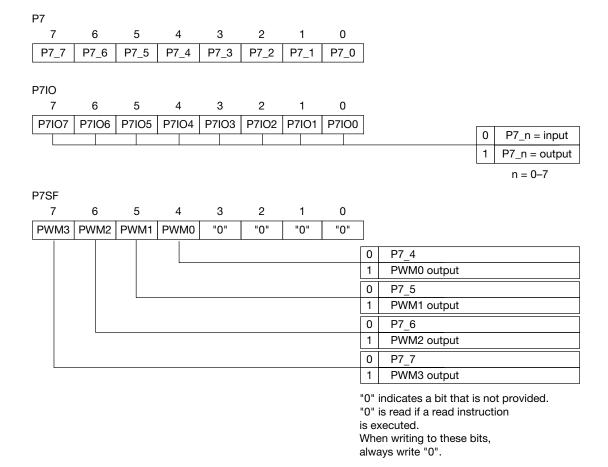

#### 2.8 P7\_0-P7\_7: Input/Output Pins

8-bit pins of Port 7. I/O can be specified in bit units by the Port 7 mode register (P7IO).

P7 2-P7 7 also function as I/O pins for internal operations (secondary function).

Secondary functions for P7\_2–P7\_7 are set in bit units by the Port 7 secondary function control register (P7SF).

For the pins that have secondary functions set by P7SF, I/O settings by P7IO become invalid.

<Description of Secondary Functions of Each Pin>

• ALE (P7\_2)

When accessing external memory, this pin outputs a strobe signal to externally latch the lower 8 bits of the address output from P0.

If the  $\overline{\text{EA}}$  pin has been set to a "L" level, the pin function automatically changes to the secondary function.

If both the  $\overline{EA}$  and  $\overline{RES}$  pins have been set to a "L" level, this pin is pulled up.

• PSEN (P7 3)

When accessing external program memory, this pin outputs a strobe signal for the read operation.

If the  $\overline{\sf EA}$  pin has been set to a "L" level, the pin function automatically changes to the secondary function.

If both the EA and RES pins have been set to a "L" level, this pin is pulled up.

PWM0 (P7\_4)–PWM3 (P7\_7)

PWM0–PWM3 output pins.

At reset (when the  $\overline{\text{RES}}$  signal is input, the BRK instruction is executed, the watchdog timer is overflown, or an operation code trap is generated), P7 becomes a high impedance input.

If the  $\overline{\text{OE}}$  pin (pin 71) is in "L" level when P7\_4 (PWM0)–P7\_7 (PWM3) are in output status, these pins output "H" or "L" level, but if the  $\overline{\text{OE}}$  pin is in "H" level, these pins go into high impedance status.

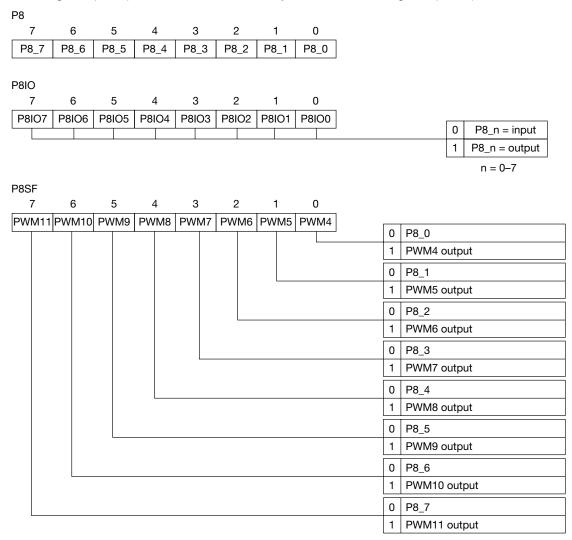

#### 2.9 P8 0-P8 7: Input/Output Pins

8-bit I/O pins of Port 8. I/O can be specified in bit units by the Port 8 mode register (P8IO).

P8 0-P8 7 also function as output pins for internal operations (secondary function).

Secondary functions for P8\_0–P8\_7 are set in bit units by the Port 8 secondary function control register (P8SF).

For the pins that have secondary functions set by P8SF, I/O settings by P8IO become invalid.

<Description of Secondary Functions of Each Pin>

PWM4 (P8\_0)-PWM11 (P8\_7)

Output Pins of PWM4-PWM11

At reset (when the  $\overline{\text{RES}}$  signal is input, the BRK instruction is executed, the watchdog timer is overflown, or an operation code trap is generated), P8 becomes a high impedance input.

If the  $\overline{OE}$  pin (pin 71) is in "L" level when P8 is in output status, these pins output "H" or "L" level, but if the  $\overline{OE}$  pin is in "H" level, these pins go into high impedance status.

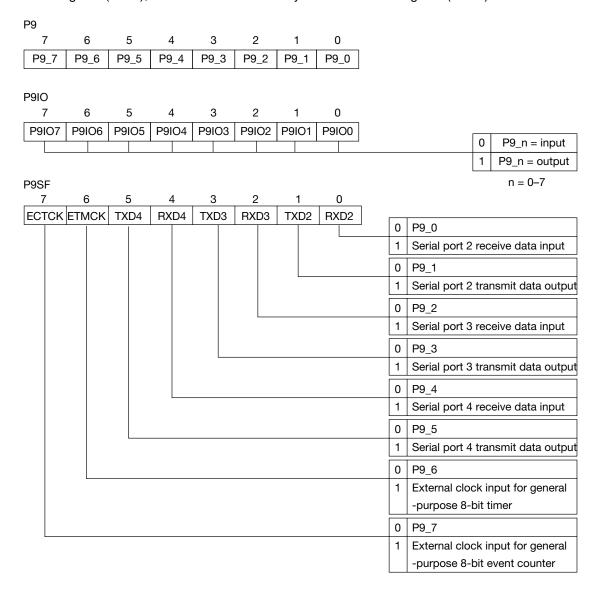

# 2.10 P9\_0-P9\_7: Input/Output Pins

8-bit I/O pins of Port 9. I/O can be specified in bit units by the Port 9 mode register (P9IO).

P9 0-P9 7 also functions as an output pin for internal operations (secondary function).

Secondary functions for P9\_0–P9\_7 are set in bit units by the Port 9 secondary function control register (P9SF). For the pins that have secondary functions set by P9SF, I/O settings by P9IO become invalid.

<Description of Secondary Functions of Each Pin>

RXD2 (P9\_0)

Receive data for the receive side serial port 2 is input through this pin.

• TXD2 (P9\_1)

Transmit data for the transmit side serial port 2 is output through this pin.

• RXD3 (P9\_2)

Receive data for the receive side serial port 3 is input through this pin.

• TXD3 (P9 3)

Transmit data for the transmit side serial port 3 is output through this pin.

• RXD4 (P9\_4)

Receive data for the receive side serial port 4 is output through this pin.

• TXD4 (P9 5)

Transmit data for the transmit side serial port 4 is input through this pin.

• ETMCK (P9 6)

External clock input pin of the general-purpose 8-bit timer counter.

ECTCK (P9 7)

External clock input pin of the general-purpose 8-bit event counter.

At reset (when the  $\overline{\text{RES}}$  signal is input, the BRK instruction is executed, a watchdog timer is overflown, or an operation code trap is generated), P9 becomes a high impedance input.

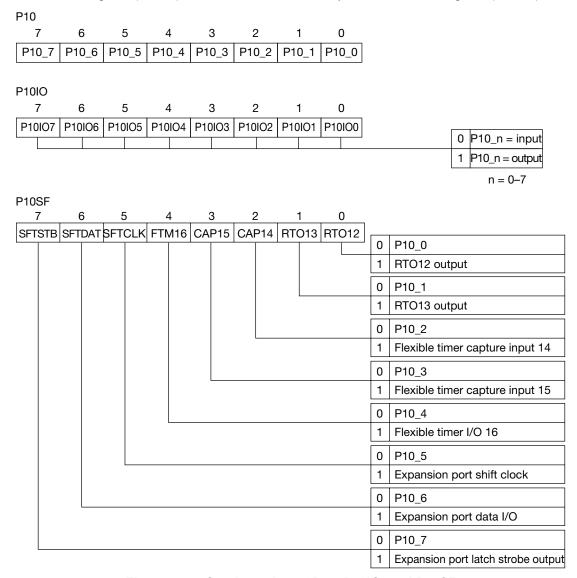

# 2.11 P10\_0-P10\_7: Input/Output Pins

8-bit I/O pins of Port 10. I/O can be specified in bit units by the Port 10 mode register (P10IO).

P10 0-P10 7 also function as output pins for internal operations (secondary function).

Secondary functions for P10\_0–P10\_7 are set in bit units by the Port 10 secondary function control register (P10SF).

For the pins that have secondary functions set by P10SF, I/O settings by P10IO become invalid.

<Description of Secondary Functions of Each Pin>

• RTO12 (P10\_0), RTO13 (P10\_1)

The output pins from which the set level is output when the value of the registers 12 and 13 (TMR12, TMR13) for the flexible timer is consistent with the value of the selected counter. These are I/O pins that output the set level.

CAP14 (P10 2), CAP15 (P10 3)

When the specified edge is input to these pins for the specified number of times, the value of the selected counter is input to TMR14, TMR15.

• FTM16 (P10\_4)

Output pins from which set level is output when the value of the register 16 (TMR16) for the flexible timer matches the value of the selected counter. This is true when the TMR16 is in RTO mode.

If this register is in CAP mode, the FTM16 pin is configured to be input pin. When the specified edge is input to this pin, the value of the selected counter is input to TMR16.

• SFTCLK (P10\_5)

Shift clock output pin for the expansion port.

• SFTDAT (P10 6)

Serial data input/output pin for the expansion port.

• SFTSTB (P10\_7)

Strobe signal output pin for externally latching serial data through the expansion port.

At reset (when the  $\overline{\text{RES}}$  signal is input, the BRK instruction is executed, the watchdog timer is overflown, or an operation code trap is generated), P10 becomes a high impedance input.

If the  $\overline{\text{OE}}$  pin (pin 71) is in "L" level when P10\_0–P10\_4 are in output status, these pins output "H" or "L" level, but if the  $\overline{\text{OE}}$  pin is in "H" level, these pins go into high impedance status.

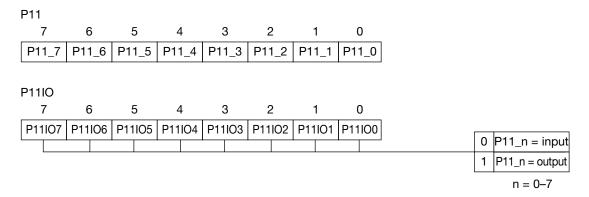

# 2.12 P11\_0-P11\_7: Input/Output Pins

8-bit I/O pins of Port 11. Individual bits can be specified as input or output by the Port 11 mode register (P11IO).

P11\_0-P11\_3 also function (secondary and tertiary functions) as I/O pins for internal operation.

<Description of Secondary/Tertiary Functions of Each Pin>

• RMRX (P11\_0)

Address input pin for RAM monitor function.

Also functions (tertiary function) as data I/O pin for serial write mode of the MSM66Q591/ML66Q592 flash EEPROM.

• RMTX (P11\_1)

Data output pin for RAM monitor function.

• RMCLK (P11 2)

Synchronous clock input pin for RAM monitor function.

Also functions (tertiary function) as clock input pin for serial write mode of the MSM66Q591/ML66Q592 Flash EEPROM.

• RMACK (P11 3)

Address match signal output pin for RAM monitor function.

At reset (when the  $\overline{\text{RES}}$  signal is input, the BRK instruction is executed, the watchdog timer is overflown, or an operation code trap is generated), P11 becomes a high impedance input, except when the RAM monitor function is enabled.

# 2.13 P12\_0, P12\_1: Input/Output Pins

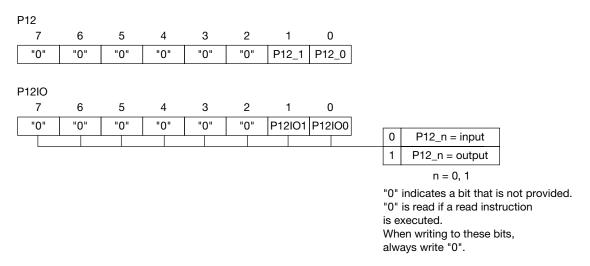

2-bit I/O pins of Port 12. Individual bits can be specified as input or output by the Port 12 mode register (P12IO).

P12\_0 can also be made to function (secondary function) as an output pin for internal operation by setting the  $\overline{EA}$  pin to a "L" level. In the ML66592, P12\_1, also, functions as its secondary function.

<Description of Secondary Functions of Each Pin>

• A16 (P12\_0)

If the  $\overline{EA}$  pin has been set to a "L" level, this pin functions to output address A16 that is used to access external expanded program memory.

• A17 (P12 1)

If the  $\overline{EA}$  pin has been set to a "L" level, this pin functions to output address A17 that is used to access external expanded program memory. (ML66592 only)

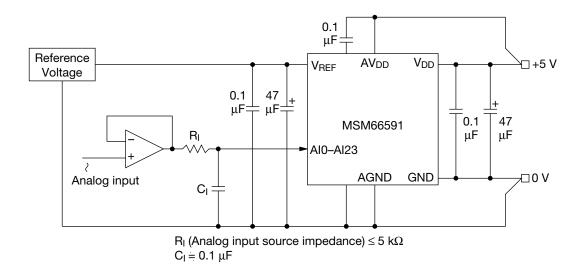

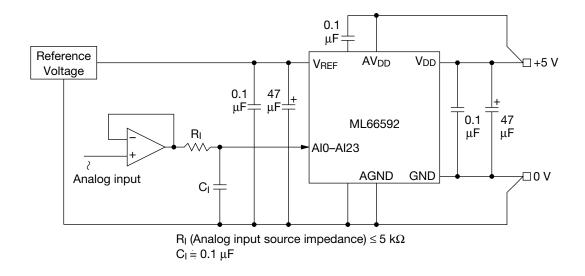

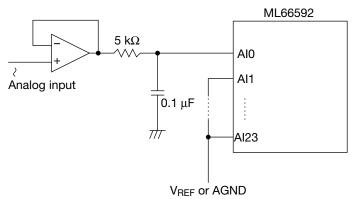

## 2.14 AI0-AI23: Input Pins

Analog input pins of the A/D converter.

# 2.15 AV<sub>DD</sub>: Input Pin

Power input pin of the A/D converter. Supply the same voltage as V<sub>DD</sub> to this pin.

#### 2.16 V<sub>RFF</sub>: Input Pin

Reference voltage input pin of the A/D converter.

# 2.17 AGND: Input Pin

GND pin of the A/D converter.

#### 2.18 OSC0, OSC1: Input Pin, Output Pin

Connection pins to connect the crystal oscillator, ceramic resonator or capacitors for basic clock oscillation. If the basic clock is supplied externally, input to the OSC0 pin, and leave the OSC1 pin open.

## 2.19 OE: Input Pin

When the  $\overline{OE}$  pin is in "H" level, and when each of P0–P2, P3\_0–P3\_3, P7\_4–P7\_7, P8, P10\_0–P10\_4, P12\_0, and P12\_1 is in output status, each pin goes into high impedance state.

#### 2.20 NMI: Input Pin

Input pin of a non-maskable interrupt request.

#### 2.21 RES: Input Pin

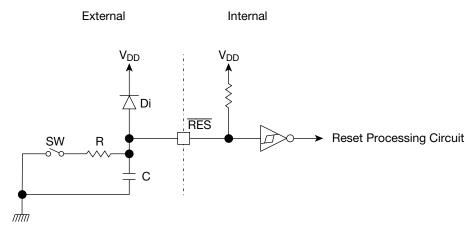

Input pin of low active reset.

# 2.22 EA: Input Pin

If the  $\overline{EA}$  pin is set to "H" level, internal program memory is accessed for the entire program address (0H–1FFFFH).

When in "H" level, the RAM monitor function is enabled.

If the  $\overline{EA}$  pin is set to "L" level, external program memory is accessed for the entire program address.

In the MSM66Q591/ML66Q592 flash EEPROM version, the RAM monitor function becomes enabled by setting the EA pin to a "H" level.

<u>Do not apply a high voltage (more than 5 V) to the  $\overline{EA}$  pin when using the MSM66591/ML66592 mask ROM version.</u>

#### 2.23 TEST: Input Pin

Load test pin. Connect to GND.

In the MSM66Q591/ML66Q592 flash EEPROM version, this pin becomes a high voltage supply pin while writing to the flash EEPROM.

In the MSM66591/ML66592 mask ROM version, the RAM monitor function becomes enabled by setting the TEST pin to "H" level. Do not apply a high voltage (more than 5 V) to this pin.

# 2.24 V<sub>DD</sub>: Input Pin

Power pin. Connect all the  $V_{DD}$  pins (pins 4, 41, 61, 80, 105, 127) to the power supply. Connect a bypass capacitor of 0.01 to 0.1  $\mu$ F between the  $V_{DD}$  and GND pins.

#### 2.25 GND: Input Pin

GND pin. Connect all the GND pins (pins 32, 44, 62, 81, 106, 128) to the ground.

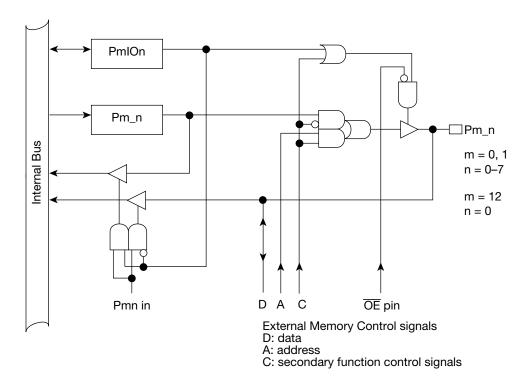

#### 2.26 Structure of Pins

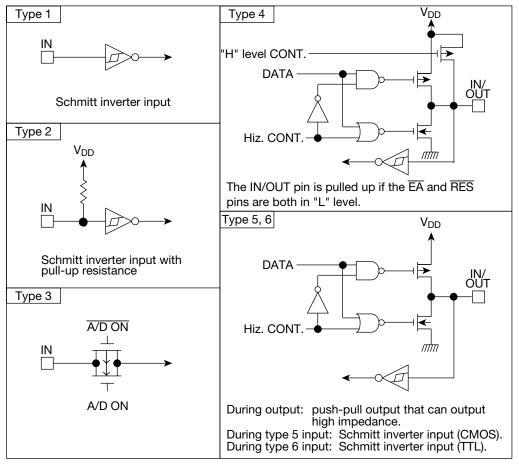

Table 2-1 and Figure 2-1 show the basic structure of each MSM66591/ML66592 pin.

| Pin Name   | Type No. | Pin Name     | Type No. |

|------------|----------|--------------|----------|

| P0_0-P0_7  | 6        | P8_0-P8_7    | 5        |

| P1_0-P1_7  | 5        | P9_0-P9_7    | 5        |

| P2_0-P2_7  | 5        | P10_0-P10_7  | 5        |

| P3_0-P3_7  | 5        | P11_0-P11_7  | 5        |

| P4_0-P4_7  | 5        | P12_0, P12_1 | 5        |

| P5_0-P5_7  | 5        | AI0-AI23     | 3        |

| DC 0 DC 7  | 5        | ŌĒ           | 1        |

| P6_0-P6_7  | 5        | NMI          | 1        |

| P7_0, P7_1 | 5        | RES          | 2        |

| P7_2, P7_3 | 4        | ĒĀ           | 1        |

|            |          |              |          |

**TEST**

5

P7\_4-P7\_7

Table 2-1 Structure of Each Pin

Figure 2-1 Pin Structure Types

# 2.27 Handling of Unused Pins

Table 2-2 shows how unused pins should be handled.

Table 2-2 Handling of Unused Pins

| Pin              | Recommended pin handling            |

|------------------|-------------------------------------|

| P0_0-P0_7        |                                     |

| P1_0-P1_7        |                                     |

| P2_0-P2_7        |                                     |

| P3_0-P3_7        |                                     |

| P4_0-P4_7        |                                     |

| P5_0-P5_5        | For input setting: "H" or "L" level |

| P6_0-P6_7        | For output setting: open            |

| P7_0-P7_7        |                                     |

| P8_0-P8_7        |                                     |

| P9_0-P9_7        |                                     |

| P10_0-P10_7      |                                     |

| P11_0-P11_7      |                                     |

| P12_0, P12_1     |                                     |

| AI0-AI23         | Connect to V <sub>REF</sub> or AGND |

| AV <sub>DD</sub> | Connect to V                        |

| V <sub>REF</sub> | Connect to V <sub>DD</sub>          |

| AGND             | Connect to GND                      |

| ŌĒ               | Set to "L" level                    |

| NMI              | Set to "H" or "L" level             |

| ĒĀ               | Set to "H" level                    |

| TEST             | Set to "L" level                    |

# **CPU Architecture**

# 3. CPU Architecture

# 3.1 Memory Space

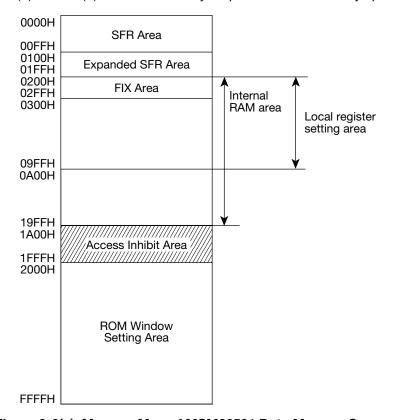

Program memory space and data memory space in MSM66591/ML66592 are set independently. At reset, up to 64K bytes (small-sized memory model) can be accessed for program memory space, and up to 6K bytes (MSM66591) or 8K bytes (ML66592) for data memory space. By changing the setting of the memory size control register allocated to the SFR, the program memory space can be expanded up to 128K bytes (MSM66591) or 192K bytes (ML66592) (medium-sized memory model).

# 3.1.1 Memory Space Expansion

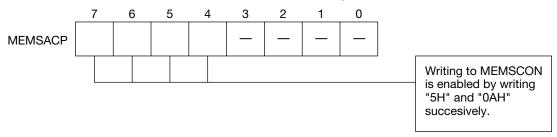

The memory size control register (MEMSCON) is a register allocated to the SFR area and specifies the size of the memory space. The program memory space can be expanded to 128K bytes (medium-sized memory model) by setting the LROM bit (bit 1) to "1". (Write "0" to bit 0.)

|         | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0   |   |                                                  |

|---------|---|---|---|---|---|---|------|-----|---|--------------------------------------------------|

| MEMSCON | _ | _ | _ | _ | _ | _ | LROM | "0" |   |                                                  |

|         |   |   |   |   |   |   |      |     | 0 | Program Memory<br>Space 64K bytes                |

|         |   |   |   |   |   |   |      |     | 1 | Program Memory<br>Space 128K bytes <sup>*1</sup> |

# \*1 192K bytes for the ML66Q592

To write to the LROM bit of MEMSCON, first write "5H" to the high-order 4 bits (low-order 4 bits are arbitrary data) of the memory size accepter (MEMSACP) allocated to the SFR area, then write "0AH" to them successively.

When an FJ or FCAL is executed with the LROM bit "0", an OP code trap is generated and a reset occurs.

When data is written to the LROM bit (setting to "1"), an actual memory space expansion is enabled after the instruction next to a LROM bit write instruction (setting to "1") is executed.

<sup>&</sup>quot;—" indicates a bit that is not provided.

<sup>&</sup>quot;1" is read if a read instruction is executed.

<sup>&</sup>quot;0" indicates a bit that is not provided.

<sup>&</sup>quot;0" is read if a read instruction is executed. Always write "0" to this bit for write.

Following is a programing example when expanding the program memory space.

This example indicates that the program memory space is expanded up to 128K bytes (MSM66591) or 192K bytes (ML66592) after the execution of NOP instruction.

MOVB MEMSACP, #50H MOVB MEMSACP, #0A0H SB LROM NOP

MSMSCON can be written only once after reset. Therefore, resetting (by RES signal input, by execution of BRK instruction, by watchdog timer (WDT) overflow, or by an operation code trap) is the only way to restore the program memory size to 64K bytes after it has been expanded to 128K bytes (MSM66591) or 192K bytes (ML66592).

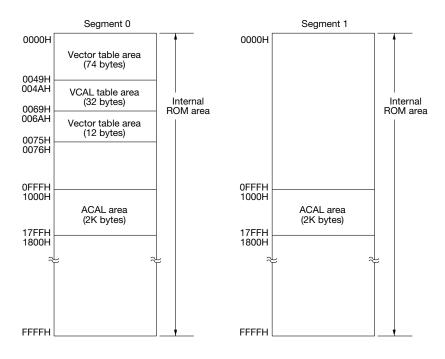

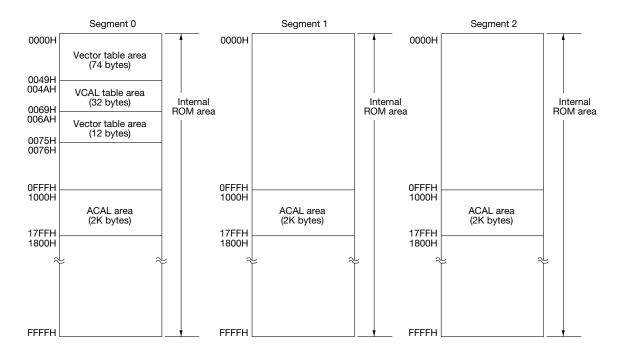

# 3.1.2 Program Memory Space

Program memory space is referred to as "ROM space."

The MSM66591 can access a maximum of 128K (131072) bytes of program memory in 64K (65536)-byte unit (segment) for segments 0 and 1. The ML66592 can access a maximum of 192K (196608) bytes of program memory in 64K (65536)-byte unit (segment) for segments 0, 1 and 2. Since segment 3 is not provided, do not try to access it. However, if more than 64K bytes (segments 1 and 2) are accessed, the LROM bit of the MEMSCON (memory size control register) allocated to SFR must be set to "1".

The code segment register (CSR) specifies the segment to be used, and the program counter (PC) specifies the address in the segment. However, the segment to be used at execution of ROM table reference instructions (LC A, obj etc.) and the ROM window functions is specified by the table segment register (TSR).

In the MSM66591, the entire 128K-byte area of the sum of the 64K (65536)-byte area in segment 0 and the 64K (65536)-byte area in segment 1 is the internal ROM area.

In the ML66592, the entire 192K (196608)-byte area of the sum of the 64K-byte area in segment 0 and each 64K-byte area in segment 1 and segment 2 is the internal ROM area.

The following areas are assigned to segment 0:

- Vector table area (86 bytes)

- VCAL table area (32 bytes)

The ACAL area (2048 bytes) is assigned to each segment.

Figures 3-1(a) and 3-1(b) show the memory maps of program memory space.

Figure 3-1(a) Memory Map of MSM66591 Program Memory Space

Figure 3-1(b) Memory Map of ML66592 Program Memory Space

## [1] Accessing Program Memory Space

Program memory space is usually accessed by the program counter (PC) and the code segment register (CSR). However, when a ROM table reference instruction (LC A, obj...etc.) or a ROM window function (see Section 5.1) is executed, program memory space is accessed by the content of the table segment register (TSR) and the register specified by the instruction.

Accessing the internal ROM area and the external memory (ROM) area of the program memory space is automatically switched by an internal MSM66591/ML66592 operation by the status of the  $\overline{EA}$  pin (input: pin 3).

When "H" level is input to the  $\overline{EA}$  pin, the internal program memory area is accessed for the entire program address. When "L" level is input to the  $\overline{EA}$  pin, the external program memory area is accessed for the entire program address.

If the external memory area of the program memory space is accessed with the  $\overline{EA}$  pin in "L" level, Port 0 (I/O: pins 72–79: output of low address and input of data), Port 1 (output: pins 82–89: output of high address) and P12\_0/A16 pin (output: pin 90: output of code segment) operates as the bus port, and the P7\_3/PSEN pin (output: pin 56) becomes active synchronizing with the P7\_2/ALE pin (output: pin 55). In ML66592, P12\_1/A17 (output: pin 91: output of code segment) also operates as a bus port.

In MSM66591, the internal program fetch enable area is 00000H–1FFFDH. This means that the final address of instruction code must not exceed 1FFFDH. The final address of the table data is 1FFFFH.

In ML66592, the internal program fetch enable area is 00000H–2FFFDH. This means that the final address of instruction code must not exceed 2FFFDH. The final address of the table data is 2FFFFH.

Segment 3 is not provided in the ML66592. Therefore, do not access address 30000H or later.

#### [2] Vector Table Area

The 74-byte area and 12-byte area of program memory space, which are 0000H–0049H and 006AH–0074H in segment 0 respectively, are the vector table area (43 types). This program memory space is used to store branch addresses caused by reset by  $\overline{RES}$  (input: pin 2) input, reset by execution of BRK instruction, reset by watchdog timer (WDT) overflow, and reset by an operation code trap (OPTRP). It is also used to store branch addresses by various interrupt requests.

If a reset or interrupt occurs, a 2-byte content of a branch address, stored in the corresponding vector table, is loaded to the PC (an even address is insignificant data, the following odd address is significant data), while at the same time "0" is loaded to the CSR, and program execution starts from the loaded address in segment 0. Therefore, if the reset or interrupt occurs during execution of the instruction for segment 1, the program is executed from an address in segment 0.