#### 3.3V, 8-OUTPUT ZERO DELAY BUFFER

FEBRUARY 2006 REV. P1.0.0

#### **XRK39653 GENERAL DESCRIPTION**

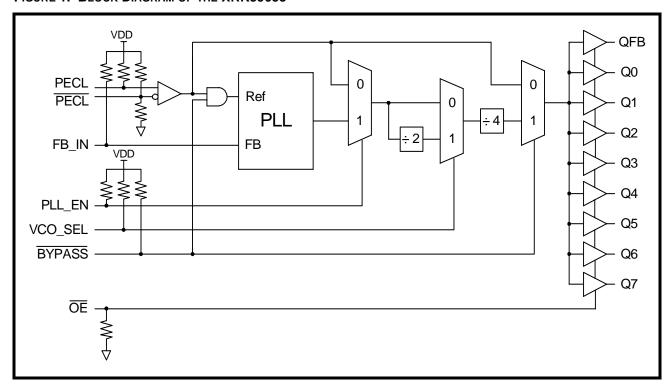

The XRK39653 is a low voltage high performance PLL based zero delay buffer/clock generator designed for high speed clock distribution applications. It provides 9 low skew, low jitter outputs ideal for networking, computing and telecom applications.

The PLL based design allows the 9 outputs (8 clock outputs and 1 feedback output) to be phase aligned to the input reference clock. The outputs source LVCMOS compatible levels and can drive  $50\Omega$  transmission lines. If series termination is used, each output can drive up to 2 lines providing effectively a fanout of 1:16. The XRK39653's reference input accepts a LVPECL clock source.

For normal operation (PLL used to source the outputs), the feedback output (QFB) is connected to the feedback input (FB\_IN). The VCO range of operation is 200 to 500MHz. This means that the input/output ranges are determined by the divider setting. If  $\div 4$  is used, the input/output range is 50 to 125MHz (high range), if  $\div 8$  is used the input/output range is 25 to 62.5MHz (low range).

For testing purposes two PLL bypass modes are provided. The first simply replaces the PLL output with the reference clock (PLL\_EN=0, BYPASS=1). The dividers are still in

use. The second is a full bypass mode that has the PLL and divider operation removed (BYPASS=0). In this mode the reference clock directly sources the outputs drivers.

#### **FEATURES**

- 8 LVCMOS Clock Outputs

- 1 Feedback Output

- LVPECL reference clock input

- 25-200 MHz input/output frequency range

- Input/Output range (÷4): 50-125MHz

- Input/Output range (÷8): 25-62.5MHz

- 150ps max output to output skew

- Two bypass test mode options

- Fully Integrated PLL

- 3.3V Operation

- Pin compatible with MPC9353

- Industrial temp range: -40°C to +85°C

- 32-Lead TQFP Packaging

FIGURE 1. BLOCK DIAGRAM OF THE XRK39653

### PRODUCT ORDERING INFORMATION

| PRODUCT NUMBER | PACKAGE TYPE             | OPERATING TEMPERATURE RANGE |

|----------------|--------------------------|-----------------------------|

| XRK39653IQ     | 32-Lead TQFP             | -40°C to +85°C              |

| XRK39653IQ-F   | 32-Lead TQFP "Lead Free" | -40°C to +85°C              |

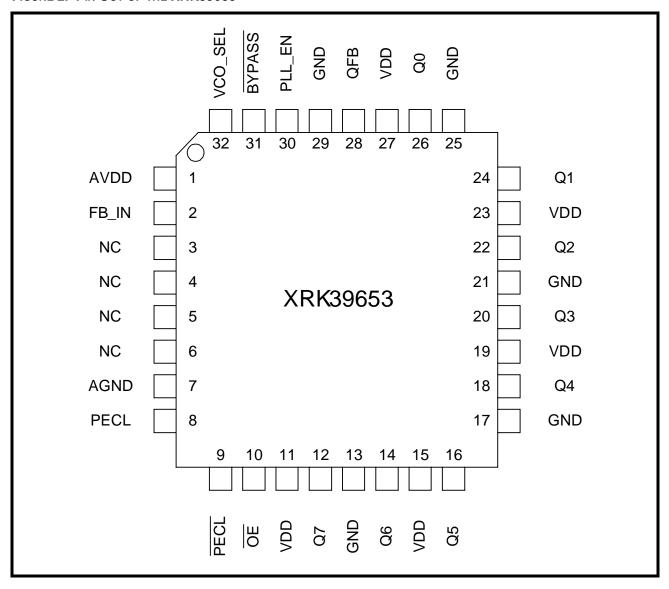

FIGURE 2. PIN OUT OF THE XRK39653

### REV. P1.0.0

## **PIN DESCRIPTIONS**

| Number                               | NAME    | T      | (PE       | DESCRIPTION                               |

|--------------------------------------|---------|--------|-----------|-------------------------------------------|

| 1                                    | AVDD    | Power  |           | Power supply for PLL                      |

| 2                                    | FB_IN   | Input  | pull-up   | External PLL feedback clock input         |

| 3, 4, 5, 6                           | NC      |        |           |                                           |

| 7                                    | AGND    | Power  |           | PLL ground                                |

| 8                                    | PECL    | Input  |           | LVPECL - pos differential reference clock |

| 9                                    | PECL    | Input  |           | LVPECL - neg differential reference clock |

| 10                                   | ŌE      | Input  | pull-down | Output enable/disable and device reset    |

| 11,15, 19,<br>23, 27,                | VDD     | Power  |           | Power supply                              |

| 12, 14, 16,<br>18, 20, 22,<br>24, 26 | Q[7:0]  | Output |           | Clock outputs                             |

| 13, 17, 21,<br>25, 29                | GND     | Power  |           | Ground                                    |

| 28                                   | QFB     | Output |           | Feedback output for PLL                   |

| 30                                   | PLL_EN  | Input  | pull-up   | PLL enable/disable select                 |

| 31                                   | BYPASS  | Input  | pull-up   | PLL and output divider bypass select      |

| 32                                   | VCO_SEL | Input  | pull-up   | VCO divider select                        |

TABLE 1: CONTROL INPUT FUNCTION TABLE

| Pin Name | 0                                                                                                           | 1                                                                                       | Default |

|----------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------|

| VCO_SEL  | System Divide = 4 of VCO output                                                                             | System Divide = 8 of VCO output                                                         | 1       |

| PLL_EN   | PLL is bypassed and disabled. The PECL clock reference source drives the outputs through the divider blocks | PLL enabled. Normal operation. VCO output drives the outputs through the divider blocks | 1       |

| BYPASS   | Complete bypass of the PLL and divider blocks. PECL reference clocks the outputs.                           | Normal operation. Dividers selected.                                                    | 1       |

| ŌĒ       | Outputs enabled                                                                                             | Outputs tri-stated and device reset. VCO running at minimum frequency                   | 0       |

## DC Characteristics ( $V_{CC}$ = 3.3 $\pm$ 5%, $T_A$ = -40°C to +85°C)

| SYMBOL                        | CHARACTERISTICS                       | MIN | TYP                | MAX                  | Unit   | CONDITION                                    |

|-------------------------------|---------------------------------------|-----|--------------------|----------------------|--------|----------------------------------------------|

| V <sub>CMR</sub> <sup>a</sup> | PECL Clock inputs common mode range   | 1.0 |                    | V <sub>DD</sub> -0.6 | V      | LVPECL                                       |

| V <sub>PP</sub>               | PECL Clock peak-to-peak input voltage | 300 |                    | 1000                 | mV     | LVPECL                                       |

| V <sub>IH</sub>               | Input voltage high                    | 2.0 |                    | V <sub>DD</sub> +0.3 | V      | LVCMOS                                       |

| V <sub>IL</sub>               | Input voltage low                     |     |                    | 0.8                  | V      | LVCMOS                                       |

| V <sub>OH</sub>               | Output High Voltage <sup>a</sup>      | 2.4 |                    |                      | V      | I <sub>OH</sub> =-24mA                       |

| V <sub>OL</sub>               | Output Low Voltage <sup>a</sup>       |     |                    | 0.55<br>0.30         | V<br>V | I <sub>OL</sub> =24mA                        |

|                               |                                       |     |                    | 0.00                 | V      | I <sub>OL</sub> =12mA                        |

| Z <sub>OUT</sub>              | Output Impedance                      |     | 14-17              |                      | Ω      |                                              |

| I <sub>IN</sub>               | Input leakage current                 |     |                    | <u>+</u> 200         | μΑ     | $V_{IN} = V_{DD}$ or $V_{IN} = GND$          |

| I <sub>CC_PLL</sub>           | Maximum PLL supply current            |     | 5.0                | 10.0                 | mA     | AV <sub>DD</sub> pin                         |

| I <sub>CCQ</sub>              | Maximum Quiescent supply current      |     |                    | 10.0                 | mA     | All V <sub>DD</sub> pins, $\overline{OE}$ =1 |

| V <sub>TT</sub>               | Output Termination Voltage            |     | V <sub>CC</sub> ÷2 |                      | V      |                                              |

**a.** VCMR is the cross point of the differential input signal.

# AC Characteristics (V<sub>CC</sub>= 3.3 $\pm$ 5%, T<sub>A</sub>= -40°C to +85°C) <sup>a</sup>

| SYMBOL                | PARAMETER                                               |                           | Min | Түр | Max                   | Unit | CONDITION   |

|-----------------------|---------------------------------------------------------|---------------------------|-----|-----|-----------------------|------|-------------|

| $f_{VCO}$             | VCO Frequency                                           |                           | 200 |     | 500                   | MHz  |             |

| f <sub>ref</sub>      | Input Reference Frequency                               | ÷4 feedback               | 50  |     | 125                   | MHz  | PLL locked  |

|                       |                                                         | ÷8 feedback               | 25  |     | 62.5                  |      | PLL locked  |

|                       |                                                         | PLL Bypass                | 0   |     | 200                   |      | bypass mode |

| f <sub>MAX</sub>      | Max Output Frequency                                    | ÷4 feedback               | 50  |     | 125                   | MHz  | PLL locked  |

|                       |                                                         | ÷8 feedback               | 25  |     | 62.5                  |      | PLL locked  |

| V <sub>PP</sub>       | PECL Clock peak-to-peak input voltage                   |                           | 450 |     | 1000                  | mV   | LVPECL      |

| $V_{CMR}$             | PECL input Common Mode range                            |                           | 1.2 |     | V <sub>DD</sub> -0.75 | V    | LVPECL      |

| t <sub>PW Min</sub>   | Input Reference Clock Minimum Pulse Width               |                           | 2   |     |                       | ns   |             |

| t <sub>SPO</sub>      | Propagation Delay - Static Phase Offset (PECL to FB_IN) |                           | -75 |     | 125                   | ps   | PLL locked  |

| t <sub>PD</sub>       | Propagation Delay - PLL Bypas                           | ssed                      |     |     |                       |      |             |

|                       | Bypass mode 1                                           | $(\overline{BYPASS} = 0)$ | 1.2 |     | 3.3                   | ns   |             |

|                       | Bypass mode 2, (BYPASS = 1, PLL_EN = 0)                 |                           | 3.0 |     | 7.0                   | ns   |             |

| t <sub>skew(O)</sub>  | Output-to-Output Skew                                   |                           |     |     | 150                   | ps   |             |

| t <sub>skew(PP)</sub> | Part to Part Skew (bypass PLL & divider)                |                           |     |     | 1.5                   | ns   | BYPASS=0    |

| t <sub>JIT(CC)</sub>  | Cycle-to-Cycle Jitter                                   |                           |     |     | 100                   | ps   |             |

## AC CHARACTERISTICS ( $V_{CC}$ = 3.3 $\pm$ 5%, $T_A$ = -40°C to +85°C) <sup>a</sup>

| SYMBOL                           | PARAMETER                             | Min | Түр | Max                  | Unit       | Condition    |

|----------------------------------|---------------------------------------|-----|-----|----------------------|------------|--------------|

| t <sub>JIT(PER)</sub>            | Period Jitter                         |     |     | 100                  | ps         |              |

| t <sub>JIT(I/O)</sub>            | I/O Phase Jitter (RMS)                |     |     | 25                   | ps         |              |

| BW                               | PLL bandwidth ÷4 feedback ÷8 feedback |     |     | 0.8 - 4<br>0.5 - 1.3 | MHz<br>MHz |              |

| DC                               | Output duty cycle                     | 45  | 50  | 55                   | %          | PLL locked   |

| t <sub>LOCK</sub>                | Maximum PLL Lock Time                 |     |     | 10.0                 | ms         |              |

| t <sub>or</sub> /t <sub>of</sub> | Output Rise/Fall time                 | 100 |     | 1000                 | ps         | 0.55 to 2.4V |

| t <sub>PLZ,HZ</sub>              | Output Disable Time                   |     |     | 7                    | ns         |              |

| t <sub>PHZ,LZ</sub>              | Output Enable Time                    |     |     | 6                    | ns         |              |

a. AC characteristics apply for parallel output termination of  $50\Omega$  to  $V_{TT\cdot}$

### **MAXIMUM RATINGS**<sup>a</sup>

| SYMBOL           | CHARACTERISTICS     | Min  | Max                  | Unit | CONDITION |

|------------------|---------------------|------|----------------------|------|-----------|

| $V_{DD}$         | Supply Voltage      | -0.3 | 3.9                  | V    |           |

| V <sub>IN</sub>  | DC Input Voltage    | -0.3 | V <sub>DD</sub> +0.3 | V    |           |

| V <sub>OUT</sub> | DC Output Voltage   | -0.3 | V <sub>DD</sub> +0.3 | V    |           |

| I <sub>IN</sub>  | DC Input Current    |      | <u>+</u> 20          | mA   |           |

| I <sub>OUT</sub> | DC Output Current   |      | <u>+</u> 50          | mA   |           |

| T <sub>S</sub>   | Storage Temperature | -65  | 125                  | °C   |           |

**a.** Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability.

#### **GENERAL SPECIFICATIONS**

| SYMBOL          | CHARACTERISTICS                   | Min  | Түр                | Max | Unit | CONDITION |

|-----------------|-----------------------------------|------|--------------------|-----|------|-----------|

| $V_{TT}$        | Output termination voltage        |      | V <sub>CC</sub> ÷2 |     | V    |           |

| MM              | ESD Protection (Machine model)    | 200  |                    |     | V    |           |

| HBM             | ESD Protection (Human body model) | 2000 |                    |     | V    |           |

| LU              | Latch-up immunity                 | 200  |                    |     | mA   |           |

| C <sub>IN</sub> | Input Capacitance                 |      | 4.0                |     | pF   | Inputs    |

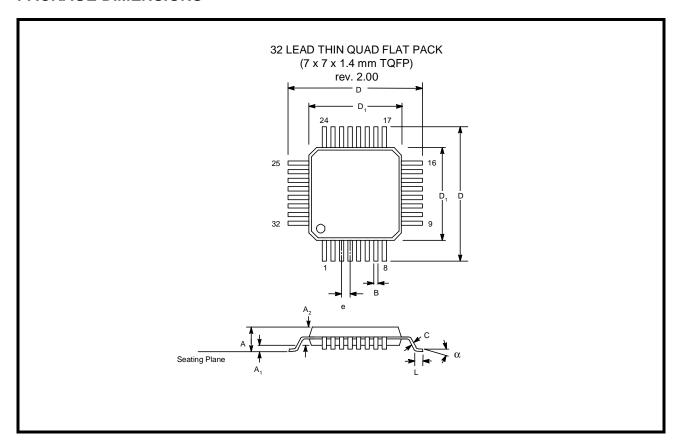

## **PACKAGE DIMENSIONS**

Note: The control dimension is the millimeter column

|                | INC   | HES   | MILLIN | IETERS     |

|----------------|-------|-------|--------|------------|

| SYMBOL         | MIN   | MAX   | MIN    | MAX        |

| А              | 0.055 | 0.063 | 1.40   | 1.60       |

| A <sub>1</sub> | 0.002 | 0.006 | 0.05   | 0.15       |

| A <sub>2</sub> | 0.053 | 0.057 | 1.35   | 1.45       |

| В              | 0.012 | 0.018 | 0.30   | 0.45       |

| С              | 0.004 | 0.008 | 0.09   | 0.20       |

| D              | 0.346 | 0.362 | 8.80   | 9.20       |

| D <sub>1</sub> | 0.272 | 0.280 | 6.90   | 7.10       |

| е              | 0.031 | 5 BSC | 0.80   | BSC        |

| L              | 0.018 | 0.030 | 0.45   | 0.75       |

| α              | 0°    | 7°    | 0°     | <b>7</b> ° |

# REV. P1.0.0

#### **REVISION HISTORY**

| REVISION # | DATE          | DESCRIPTION      |

|------------|---------------|------------------|

| P1.0.0     | February 2006 | Initial release. |

|            |               |                  |

|            |               |                  |

|            |               |                  |

|            |               |                  |

|            |               |                  |

|            |               |                  |

|            |               |                  |

|            |               |                  |

|            |               |                  |

|            |               |                  |

#### **NOTICE**

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 2006 EXAR Corporation

Datasheet February 2006.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.