## **General Description**

The MAX6391/MAX6392 microprocessor (µP) supervisory circuits provide sequenced logic reset outputs for multicomponent or dual-voltage systems. Each device can monitor two supply voltages and time-sequence two reset outputs to control the order in which system components are turned on and off. The MAX6391/MAX6392 increase system reliability and reduce circuit complexity and cost compared to separate ICs or discrete components.

The MAX6391/MAX6392 monitor VCC as the master reset supply. Both RESET1 and RESET2 are asserted whenever VCC drops below the selected factory-fixed reset threshold voltage. RESET1 remains asserted as long as VCC is below the threshold and deasserts 140ms (min) after VCC exceeds the thresholds.

RESET IN2 is monitored as the secondary reset supply and is adjustable with an external resistive-divider network. RESET2 is asserted whenever either VCC or RESET IN2 is below the selected thresholds. RESET2 remains asserted 140ms (min) or a capacitoradjustable time period after  $V_{CC}$  and RESET IN2 exceed their thresholds.  $\overline{\text{RESET2}}$  is always deasserted after RESET1 during system power-up and is always asserted before RESET1 during power-down.

The MAX6391 includes two internal pullup resistors for RESET1 and RESET2 (the open-drain outputs can be externally connected to the desired pullup voltages). The MAX6392 includes an active-low manual reset input (MR) that asserts both RESET1 (push-pull) and RESET2 (open drain).

The MAX6391/MAX6392 are available in small 8-pin SOT23 packages and are specified over the -40°C to +85°C extended temperature range.

## **Applications**

Computers

Controllers

Critical µP Power Monitoring

Set-Top Boxes

**Printers**

Servers/Workstations

Industrial Equipment

Multivoltage Monitoring

**Features**

- ♦ Preset VCC Reset Threshold Voltages from 1.58V to 4.63V (master supply)

- ♦ Customer-Adjustable RESET IN2 to Monitor Voltages Down to 625mV (secondary supply)

- ♦ Fixed (140ms min) RESET1 Timeout

- ♦ Fixed (140ms min) or Customer-Adjustable **RESET2** Timeout Period

- ♦ Guaranteed Reset Valid to Vcc = 1V

- **♦** Active-Low Open-Drain Outputs or Push-**Pull/Open-Drain Combination**

- ♦ Internal Open-Drain Pullup Resistors (for external **VOH voltage connections)**

- ♦ Manual Reset Input (MAX6392 only)

- **♦ Immune to Short Negative Vcc Transients**

- ♦ 15µA Typical Supply Current

- **♦ Few External Components**

- ♦ Small 8-Pin SOT23 Package

## **Ordering Information**

| PART*      | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX6391KAT | -40°C to +85°C | SOT23-8     |

| MAX6392KAT | -40°C to +85°C | SOT23-8     |

\*Insert the desired suffix (see Selector Guide) into the blanks to complete the part number. The MAX6391/MAX6392 require a 2.5k minimum order increment and are available in tape-andreel only. Samples are typically available for standard versions (see Selector Guide for standard versions). Contact factory for availability.

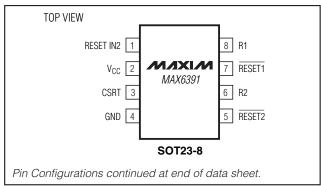

## **Pin Configurations**

Typical Operating Circuit appears at end of data sheet.

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| 0.074                                                 |

|-------------------------------------------------------|

| V <sub>CC</sub> to GND0.3V to +6.0V                   |

| RESET1 (MAX6392), RESET IN2, CSRT,                    |

| MR to GND0.3V to (V <sub>CC</sub> + 0.3V)             |

| RESET1 (MAX6391), RESET2, R1, R2 to GND0.3V to +6.0V  |

| Input Current (VCC, GND, CSRT, R1, R2, MR)±20mA       |

| Output Current (RESET1, RESET2)±20mA                  |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

| 8-Pin SOT23 (derate 5.26mW/°C above +70°C)421mW       |

| Operating Temperature Range       | 40°C to +85°C  |

|-----------------------------------|----------------|

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 1.2V \text{ to } 5.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise specified.}$  Typical values are at  $V_{CC} = +5V$  and  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                       | SYMBOL           | CONDITIONS                                 | MIN  | TYP  | MAX  | UNITS        |

|-------------------------------------------------|------------------|--------------------------------------------|------|------|------|--------------|

| V Dance                                         |                  | $T_A = 0$ °C to +85°C                      | 1.0  |      | 5.5  | V            |

| V <sub>CC</sub> Range                           |                  | $T_A = -40$ °C to $+85$ °C                 | 1.2  |      | 5.5  | V            |

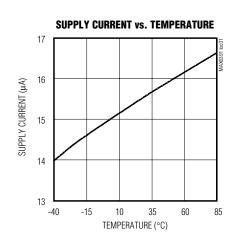

| Supply Current                                  | Icc              | No load                                    |      | 15   | 25   | μΑ           |

|                                                 |                  | MAX639_UA46                                | 4.50 | 4.63 | 4.75 |              |

|                                                 |                  | MAX639_UA44                                | 4.25 | 4.38 | 4.50 |              |

|                                                 |                  | MAX639_UA31                                | 3.00 | 3.08 | 3.15 |              |

| V <sub>CC</sub> Reset Threshold                 |                  | MAX639_UA29                                | 2.85 | 2.93 | 3.00 | V            |

|                                                 | V <sub>TH1</sub> | MAX639_UA26                                | 2.55 | 2.63 | 2.70 |              |

|                                                 |                  | MAX639_UA23                                | 2.25 | 2.32 | 2.38 |              |

|                                                 |                  | MAX639_UA22                                | 2.12 | 2.19 | 2.25 |              |

|                                                 |                  | MAX639_UA17                                | 1.62 | 1.67 | 1.71 | <u>]</u><br> |

|                                                 |                  | MAX639_UA16                                | 1.54 | 1.58 | 1.61 |              |

| RESET IN2 Threshold                             | V <sub>TH2</sub> | V <sub>CC</sub> = 5V                       | 610  | 625  | 640  | mV           |

| RESET IN2 Input Current                         |                  |                                            |      |      | 50   | nA           |

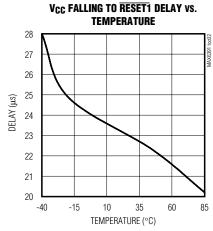

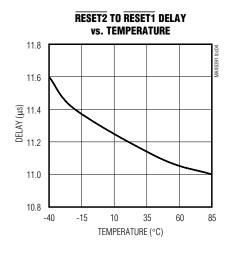

| V <sub>CC</sub> to RESET1 Delay                 | t <sub>RD1</sub> |                                            |      | 20   |      |              |

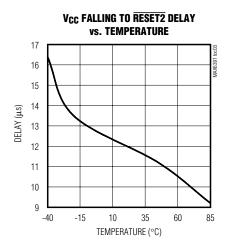

| V <sub>CC</sub> or RESET IN2 to RESET2<br>Delay | t <sub>RD2</sub> | V <sub>CC</sub> falling at 1mV/μs (Note 2) |      | 10   |      | μs           |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 1.2V \text{ to } 5.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise specified. Typical values are at } V_{CC} = +5V \text{ and } T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                              | SYMBOL           | CONDITIONS                                                                                          |                                                                        | MIN                              | TYP                             | MAX   | UNITS |

|--------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------|---------------------------------|-------|-------|

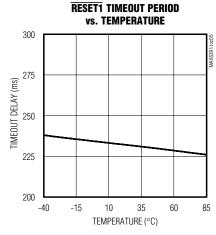

| RESET1 Timeout Period                                  | t <sub>RP1</sub> |                                                                                                     |                                                                        | 140                              | 200                             | 280   | ms    |

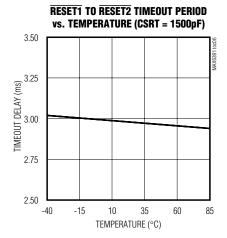

| DECETO Time out Deviced (Nata C)                       | t <sub>RP2</sub> | C <sub>CSRT</sub> = 1500pF                                                                          |                                                                        | 2.2                              | 3.1                             | 4.0   | ms    |

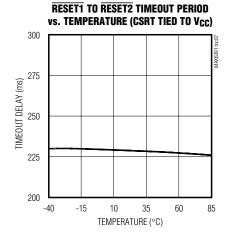

| RESET2 Timeout Period (Note 3)                         |                  | Ccsrt = Vcc                                                                                         |                                                                        | 140                              | 200                             | 280   |       |

| RESET_ Output Voltage Low                              | V <sub>OL</sub>  | ISINK = 50µA, reset asserted                                                                        | $V_{CC} \ge 1.0V$ ,<br>$T_A = 0^{\circ}C$ to $+85^{\circ}C$            |                                  |                                 | 0.3   | V     |

|                                                        |                  |                                                                                                     | $V_{CC} \ge 1.2V$ ,<br>$T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$ |                                  |                                 | 0.3   |       |

|                                                        |                  | ISINK = 1.2mA, reset                                                                                | asserted, V <sub>CC</sub> ≥ 2.5V                                       |                                  |                                 | 0.3   |       |

|                                                        |                  | I <sub>SINK</sub> = 3.2mA, reset asserted, V <sub>CC</sub> ≥ 4.25V                                  |                                                                        |                                  |                                 | 0.4   |       |

| Open-Drain RESET Output<br>Leakage Current             | I <sub>LKG</sub> | V <sub>CC</sub> ≥ V <sub>TH1</sub> , V <sub>RESET IN2</sub> ≥ V <sub>TH2</sub> , reset not asserted |                                                                        |                                  |                                 | 1.0   | μΑ    |

| Push-Pull RESET1 Output<br>Voltage High (MAX6392 only) | Vон              | V <sub>CC</sub> ≥ 2.25V, I <sub>SOURC</sub> reset not asserted                                      | E = 500μA,                                                             |                                  |                                 | 0.8 🏚 | V     |

|                                                        | VOH              | V <sub>CC</sub> ≥ 4.5V, I <sub>SOURCE</sub> asserted                                                | E = 800μA, reset not                                                   |                                  |                                 | Vcc   | C v   |

|                                                        | V <sub>IL</sub>  | V <sub>CC</sub> > 4.0V                                                                              |                                                                        |                                  |                                 | 0.8   | V     |

|                                                        | VIH              |                                                                                                     |                                                                        | 2.4                              |                                 |       |       |

| MR Input                                               | V <sub>IL</sub>  | V 4.0V                                                                                              |                                                                        |                                  | 0.3 <b>☆</b><br>V <sub>CC</sub> |       |       |

|                                                        | VIH              | V <sub>CC</sub> < 4.0V                                                                              |                                                                        | 0.7 <b>☆</b><br>V <sub>C</sub> C |                                 |       |       |

| MR Minimum Pulse Width                                 |                  |                                                                                                     |                                                                        | 50                               |                                 |       | μs    |

| MR Glitch Rejection                                    |                  |                                                                                                     |                                                                        |                                  | 100                             |       | ns    |

| MR to RESET1 Delay                                     | t <sub>MR1</sub> |                                                                                                     |                                                                        |                                  | 10                              |       | μs    |

| MR to RESET2 Delay                                     | t <sub>MR2</sub> |                                                                                                     |                                                                        |                                  | 100                             |       | ns    |

| t <sub>MR</sub> Skew                                   |                  | tMR1 - tMR2                                                                                         |                                                                        |                                  | 10                              |       | μs    |

| MR Pullup Resistance                                   |                  | Pullup to V <sub>CC</sub>                                                                           |                                                                        | 35                               | 47                              | 60    | kΩ    |

| Reset Pullup Resistance                                |                  | RESET1 to R1 or RES                                                                                 | SET2 to R2                                                             | 35                               | 47                              | 60    | kΩ    |

Note 1: Overtemperature limits are guaranteed by design and not production tested. Devices tested at +25°C only.

Note 2: RESET2 asserts before RESET1 when V<sub>CC</sub> goes below the threshold for all supply voltage and temperature ranges.

Note 3: CSRT must be connected to either V<sub>CC</sub> (for fixed RESET2 timeout period) or an external capacitor (for user-adjustable RESET2 timeout period).

## **Typical Operating Characteristics**

$(V_{CC} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

#### **Pin Description**

| PIN     |         | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                     |  |  |

|---------|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX6391 | MAX6392 |           |                                                                                                                                                                                                                                                                                                              |  |  |

| 1       | 1       | RESET IN2 | Input Voltage for RESET2 Monitor. High-impedance input for internal reset comparator. Connect this pin to an external resistive-divider network to set the resthreshold voltage.                                                                                                                             |  |  |

| 2       | 2       | Vcc       | Supply Voltage and Input Voltage for Primary Supply Monitor                                                                                                                                                                                                                                                  |  |  |

| 3       | 3       | CSRT      | RESET2 Delay Set Capacitor. Connect to V <sub>CC</sub> for a fixed 140ms (min) timeout period or to an external capacitor for a user-adjustable timeout period after V <sub>CC</sub> exceeds its minimum threshold.                                                                                          |  |  |

| 4       | 4       | GND       | Ground                                                                                                                                                                                                                                                                                                       |  |  |

| 5       | 5       | RESET2    | Secondary Reset Output, Open-Drain, Active-Low. RESET2 changes from high to when either V <sub>CC</sub> or RESET IN2 drop below their thresholds. RESET2 remains low for user-adjustable timeout period (see CSRT) or a fixed 140ms (min) after V <sub>CC</sub> and RESET IN2 meet their minimum thresholds. |  |  |

| 6       | 6       | R2        | 47kΩ Internal Pullup Resistor for $\overline{\text{RESET2}}$ . Connect to external voltage for $\overline{\text{RESET2}}$ high pullup.                                                                                                                                                                       |  |  |

| 7       | 7       | RESET1    | Primary Reset Output, Open-Drain (MAX6391) or Push-Pull (MAX6392), Active-Low. RESET1 changes from HIGH to LOW when the V <sub>CC</sub> input drops below the selected reset threshold. RESET1 remains LOW for the reset timeout period after V <sub>CC</sub> exceeds the minimum threshold.                 |  |  |

| 8       |         | R1        | $47$ k $\Omega$ Internal Pullup Resistor for RESET1. Connect to external voltage for RESET1 high pullup.                                                                                                                                                                                                     |  |  |

| _       | 8       | MR        | Manual Reset, Active-Low, Internal $47k\Omega$ Pullup to $V_{CC}$ . Pull LOW to force a reset. RESET1 and RESET2 remain asserted as long as $\overline{MR}$ is LOW and for the RESET1 RESET2 timeout periods after $\overline{MR}$ goes HIGH. Leave unconnected or connect to V if unused.                   |  |  |

## **Detailed Description**

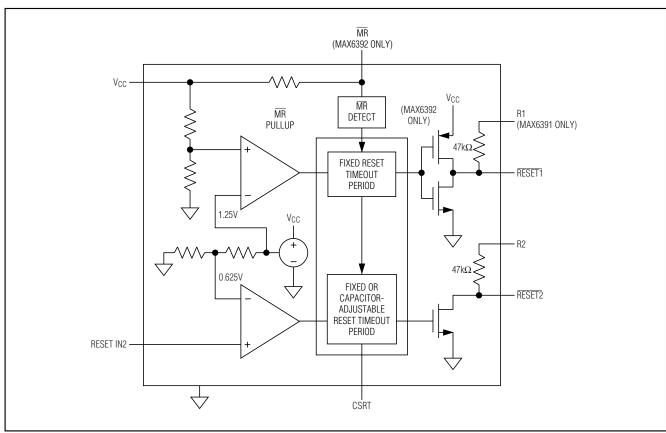

Each device includes a pair of voltage monitors with sequenced reset outputs. The first block monitors V<sub>CC</sub> only (RESET1 output is independent of the RESET IN2 monitor). It asserts a reset signal (LOW) whenever V<sub>CC</sub> is below the preset voltage threshold. RESET1 remains asserted for at least 140ms after V<sub>CC</sub> rises above the reset threshold. RESET1 timing is internally set in each device. V<sub>CC</sub> voltage thresholds are available from 1.57V to 4.63V. In all cases V<sub>CC</sub> acts as the master supply (all resets are asserted when V<sub>CC</sub> goes below its selected threshold). The V<sub>CC</sub> input also acts as the device power supply.

The second block monitors both RESET IN2 and V<sub>CC</sub>. It asserts a reset signal (LOW) whenever RESET IN2 is below the <u>625mV</u> threshold or V<sub>CC</sub> is below its reset threshold. RESET2 remains asserted for a fixed 140ms

(min) or a user-adjustable time period after RESET IN2 rises above the 625mV reset threshold and  $\overline{\text{RESET1}}$  is deasserted. Resets are guaranteed valid for VCC down to 1V.

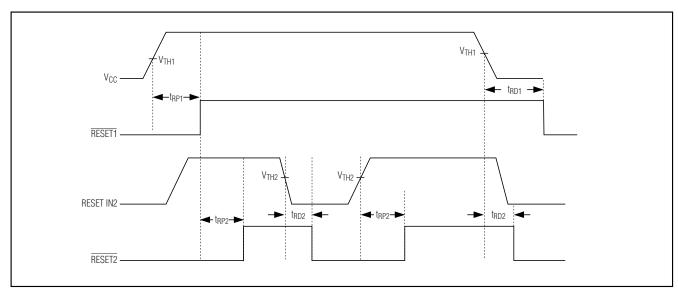

The timing diagram in Figure 2 shows the reset timing characteristics of the MAX6391/MAX6392. As shown in Figure 2,  $\overline{RESET1}$  deasserts 140ms (min) (tRP1) after VCC exceeds the reset threshold.  $\overline{RESET2}$  deasserts tRP2 (140ms minimum or a user-adjustable timeout period) after RESET IN2 exceeds 625mV and  $\overline{RESET1}$  is deasserted. When RESET IN2 drops below 625mV while VCC is above the reset threshold,  $\overline{RESET2}$  asserts within 10µs typ.  $\overline{RESET1}$  is unaffected when this happens. When VCC falls below VTH1,  $\overline{RESET2}$  always asserts before  $\overline{RESET1}$  (tRD2 < tRD1).

Figure 1. Functional Diagram

Figure 2. Timing Diagram

#### **Selector Guide**

| PART NUMBER         | NOMINAL<br>THRESHOLD (V) | TOP MARK |

|---------------------|--------------------------|----------|

| MAX6391KA <b>46</b> | 4.63                     | AAHJ     |

| MAX6391KA44         | 4.38                     | AAHK     |

| MAX6391KA31         | 3.08                     | AAHL     |

| MAX6391KA <b>29</b> | 2.93                     | AAHM     |

| MAX6391KA26         | 2.63                     | AAHN     |

| MAX6391KA <b>23</b> | 2.32                     | AAHO     |

| MAX6391KA22         | 2.19                     | AAHP     |

| MAX6391KA17         | 1.67                     | AAHQ     |

| MAX6391KA <b>16</b> | 1.58                     | AAHR     |

| MAX6392KA <b>46</b> | 4.63                     | AAHS     |

| MAX6392KA44         | 4.38                     | AAHT     |

| MAX6392KA31         | 3.08                     | AAHU     |

| MAX6392KA <b>29</b> | 2.93                     | AAHV     |

| MAX6392KA26         | 2.63                     | AAHW     |

| MAX6392KA <b>23</b> | 2.32                     | AAHX     |

| MAX6392KA22         | 2.19                     | AAHY     |

| MAX6392KA17         | 1.67                     | AAHZ     |

| MAX6392KA <b>16</b> | 1.58                     | AAIA     |

Standard versions in bold face. Samples are typically available for standard versions. Contact factory for availability.

## Applications Information

#### **Selecting the Reset Timeout Capacitor**

The RESET2 delay may be adjusted by the user with an external capacitor connected from the CSRT pin to ground. The MAX6391 includes a 600nA current source that is switched to C<sub>CSRT</sub> to create a voltage ramp. The voltage ramp is compared to the internal 1.25V reference to set the RESET2 delay period. The period is calculated by:

$$\Delta t = C \times \Delta V/I$$

where  $\Delta V$  = 1.25V, I = 600nA, and C is the external capacitor.

Simplifying,

$$t_{RP} = 2.08 \times 10^6 \text{ s} / F \times C_{CSRT}$$

For  $C_{CSRT} = 1500 \text{pF}$ ,  $t_{RP} = 3.1 \text{ms}$

$\frac{A \text{ fixed}}{\text{RESET2}}$  may be chosen by connecting the CSRT pin to V<sub>CC</sub>. The V<sub>CC</sub> to CSRT connection disables the voltage ramp and enables a separate fixed delay counter

chain. The MAX6391 internally determines the CSRT connection and provides the proper timing setup.

In all cases, RESET IN2 acts as the slave supply. VCC can assert the RESET2 output but RESET IN2 will have no effect on the RESET1 output.

#### **Monitoring Voltages Other Than Vcc**

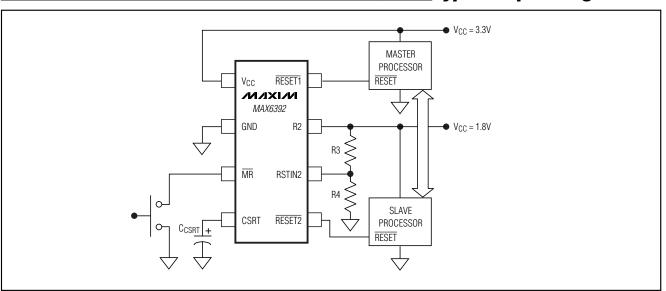

An external resistive-divider network is required at RESET IN2 for most applications. The divider resistors, R3 and R4, may be calculated by the following formula:

$$V_{RST} = V_{TH2} \times (R3 + R4)/R4$$

where  $V_{TH2}=625\text{mV}$  (internal reference voltage) and  $V_{RST}$  is the desired reset threshold voltage. R4 may be set to a conveniently high value ( $500\text{k}\Omega$  for example, to minimize current consumption) and the equation may be solved for R3 by:

$$R3 = R4 \times (V_{RST}/V_{TH2} - 1)$$

For single-supply operations requiring two reset outputs (RESET1 before RESET2), connect RESET IN2 directly to V<sub>CC</sub> and adjust RESET2 timeout delay with C<sub>CRST</sub> as desired.

#### **Pullup Resistors**

The MAX6391 includes open-drain outputs for both RESET1 and RESET2. Two internal resistors, R1 and R2, of  $47k\Omega$  each are provided with internal connections to RESET1 and RESET2. These resistors may be connected to the appropriate external voltage for independent VOH drive with no additional component requirements.

The MAX6392 includes a manual reset option,  $\overline{MR}$ , that replaces the R1 pullup resistor. The active-low manual reset input forces both  $\overline{RESET1}$  and  $\overline{RESET2}$  low.  $\overline{RESET2}$  is driven active before  $\overline{RESET1}$  in all cases (10µs typ). The resets follow standard reset timing specifications after the manual reset is released. The manual reset is internally pulled up to VCC through a  $47k\Omega$  resistor.

#### **Negative-Going Vcc Transients**

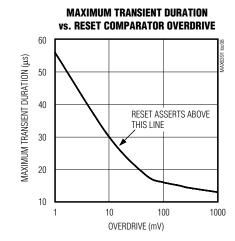

In addition to issuing a reset to the  $\mu P$  during power-up, power-down, and brownout conditions, these devices are relatively immune to short-duration, negative-going V<sub>CC</sub> or RESET IN2 transients (glitches). The *Typical Operating Characteristics* show the Maximum Transient Duration vs. Reset Comparator Overdrive graph. The graph shows the maximum pulse width that a negative-going V<sub>CC</sub> transient may typically have without issuing a reset signal. As the amplitude of the transient increases, the maximum allowable pulse width decreases.

## **Typical Operating Circuit**

## Pin Configurations (continued)

# TOP VIEW RESET IN2 1 Vcc 2 CSRT 3 GND 4 8 MR 7 RESET1 6 R2 5 RESET2 SOT23-8

## **Chip Information**

TRANSISTOR COUNT: 810 PROCESS: BICMOS

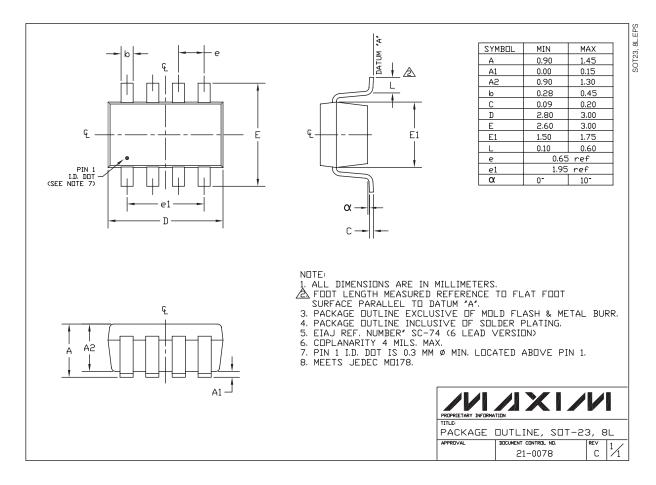

## Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.