# GM82C803C

2.88 MB FDC/ Dual UARTs with FIFO/ PIO(EPP/ ECP)/ IDE Interface/ S-IR/ PnP

# **General Description**

The GM82C803C is a single 100-pin PC95 compatible Super I/O chip with a Floppy Disk Controller with data separator, two UARTs (GM16C550) and an infrared interface, one Parallel port (IEEE 1284 Compliant). The GM82C803C is optimized for motherboard applications. The GM82C803C also includes one game port selection, IDE interface and an address decoder for on-chip function. The Floppy Disk Control part provides all the needed functionality between the host processor peripheral bus and the cable connector to the Floppy Disk Driver. integrates the selection, clock generation and high current drivers and supports the 4 MB drive as well as other standard drives. The UARTs GM82C803C are compatible with the 16C550. One UART (COM2) includes Serial Infrared Interface, complying with IrDA, HPSIR, and ASKIR streams. The Configuration register is used to allocate the I/O Base Address IRQ or DMA for each corresponding function.

## **Features**

- 100% Hardware compatible to the IBM PC/AT

- Floppy Disk Controller with 16 bytes FIFO (default disable)

- Data rates up to 1Mbps

- Perpendicular recording drive support

- Drives up to two FDDs

- 40 mA floppy disk drive interface

- FDD swap

- 48 Base I/O addresses, 7 IRQ and 3 DMA options

- Dual UARTs compatible to the GM16C550

- Programmable character lengths (5, 6, 7, 8)

- Even, odd, stick or no parity bit generation and detection

- Programmable baud rate generator

- High speed baud rate (230 Kbps, 460 Kbps) support

- Independent transmit/ receiver FIFOs

- MIDI interface

- Modem control

- Infrared -IrDA(HPSIR) and ASK(Amplitude Shift Keyed)IR

- Optional alternate IR pins

- 96 Base I/O addresses and 7 IRQ options

- Multi-mode parallel port

- Standard mode

- ECP (IEEE 1284)

- EPP (Version 1.9 : default, Version 1.7)

- 192 Base I/O addresses, 7 IRQ and 3 DMA options

- IDE interface (optional)

- 48 Base I/O addresses and 7 IRQ options

- Game chip selection logic

- 48 Base I/O addresses

- General Purpose Address Decoder

- 48 Base I/O addresses

- Power Down support

- 5 Volt operation

- 14.318 MHz or 24 MHz clock

- 100 pin QFP

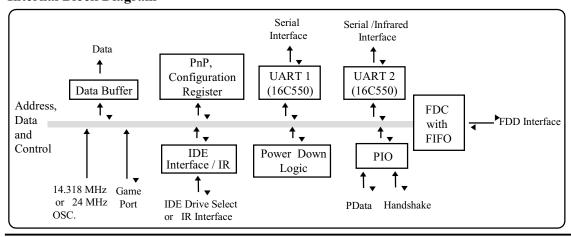

# **Internal Block Diagram**

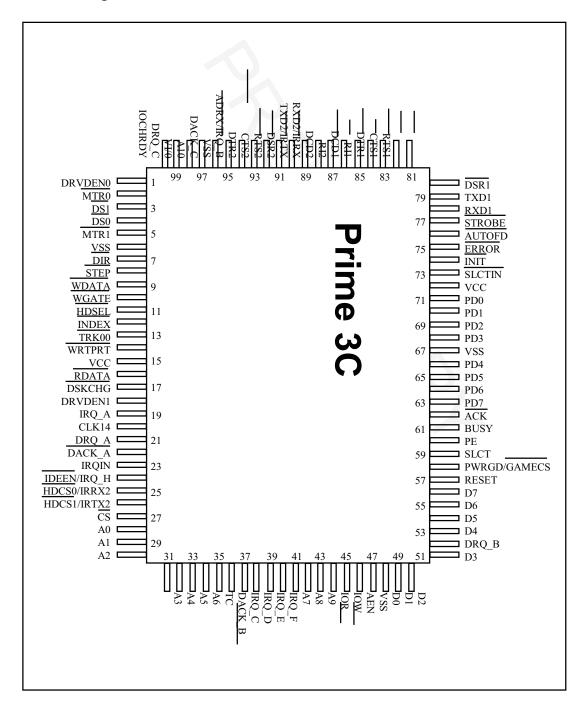

# 1. Pin Configuration

# 2. Pin Description

| PIN NO.               | PIN<br>NAME                | BUFFER<br>TYPE                                                                                                                                                          | DESCRIPTION                                                                                                                                                                                                                                                                      |  |  |  |  |

|-----------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                       | 1) HOST INTERFACE          |                                                                                                                                                                         |                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 19,<br>37-40          | IRQ_A<br>IRQ_C<br>IRQ_D    | Out  Interrupt Request pin. The interrupt request from the device or IRQIN is output on one of the IRQA-G signals. In the configuration registers for more information. |                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                       | IRQ_E<br>IRQ_F             |                                                                                                                                                                         | If EPP or ECP Mode is enabled, this output is pulsed low, then released to allow sharing of interrupts.                                                                                                                                                                          |  |  |  |  |

| 21,52,<br>99          | DRQ_A<br>DRQ_B<br>DRQ_C    | Out                                                                                                                                                                     | DMA Request pin. This active high output is the DMA request for byte transfers of data between the host and the chip. This signal is cleared on the last byte of the data transfer by the DACK signal going low (or by IOR going low if DACK was already low as in demand mode). |  |  |  |  |

| 22,36,<br>96          | DACK_A<br>DACK_B<br>DACK_C | In                                                                                                                                                                      | DMA Acknowledge pin. This active low input acknowledging the request for a DMA transfer of data between the host and the chip. This input enables the DMA read or write internally.                                                                                              |  |  |  |  |

| 27                    | CS                         | In                                                                                                                                                                      | Chip Select pin. When enabled, this active low pin serves as an input for an external decoder circuit which is used to qualify address lines above A10.                                                                                                                          |  |  |  |  |

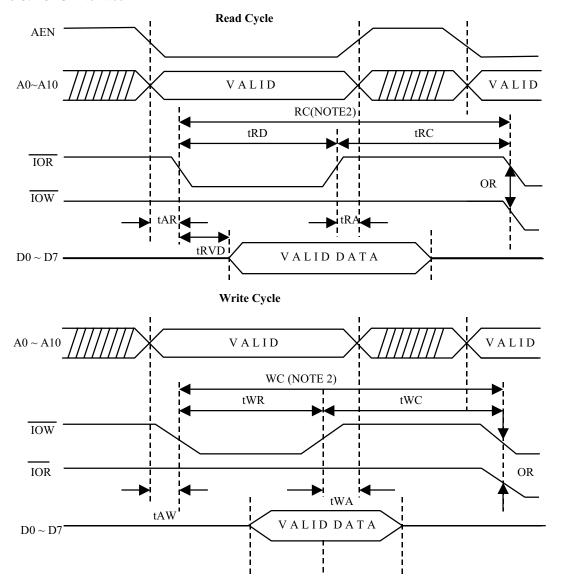

| 28-34<br>41-43,<br>97 | A0-A10                     | In                                                                                                                                                                      | I/O Address pin. These host address bits determine the I/O address to be accessed during IOR and IOW cycles. These bits are latched internally by the leading edge of IOR and IOW. All internal address decodes use the full A0 to A10 address bits.                             |  |  |  |  |

| 35                    | TC                         | In                                                                                                                                                                      | Terminal Count pin. This signal indicates to the chip that DMA data transfer is complete. TC is only accepted when DACK_x is low. TC is active high.                                                                                                                             |  |  |  |  |

| 44                    | ĪOR                        | In                                                                                                                                                                      | I/O Read pin. This active low signal is issued by the host microprocessor to indicate a read operation.                                                                                                                                                                          |  |  |  |  |

| 45                    | ĪOW                        | In                                                                                                                                                                      | I/O Write pin. This active low signal is issued by the host microprocessor to indicate a write operation.                                                                                                                                                                        |  |  |  |  |

| 46                    | AEN                        | In                                                                                                                                                                      | Address Enable pin. Active high Address Enable indicates DMA operations on the host data bus. Used internally to qualify appropriate address decodes.                                                                                                                            |  |  |  |  |

| 48-51<br>53-56        | D0-D7                      | In/Out                                                                                                                                                                  | Data Bus 0-7. This data bus used by the host microprocessor to transmit data to and to receive from the chip. These pins are in a high- impedance state when not in the output mode.                                                                                             |  |  |  |  |

| 57                    | RESET                      | In                                                                                                                                                                      | This active high signal resets the chip and must be valid for 500ns minimum. The affect on the internal registers is described in the appropriate section. The configuration registers are not affected by this reset.                                                           |  |  |  |  |

| PIN NO. | PIN<br>NAME              | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                  |  |  |  |  |  |

|---------|--------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|         | 2) FLOPPY DISK INTERFACE |                |                                                                                                                                                                                                              |  |  |  |  |  |

| 1       | DRVD-<br>EN0             | Out            | Indicates the drive and media selected.                                                                                                                                                                      |  |  |  |  |  |

| 2, 5    | MTR0,<br>MTR1            | Out            | Motor On 0,1 pins. These active low open drain outputs select motor drives 0-1.                                                                                                                              |  |  |  |  |  |

| 3, 4    | DS1,<br>DS0              | Out            | Drive Select pin. Active low open drain outputs select drives 0-1.                                                                                                                                           |  |  |  |  |  |

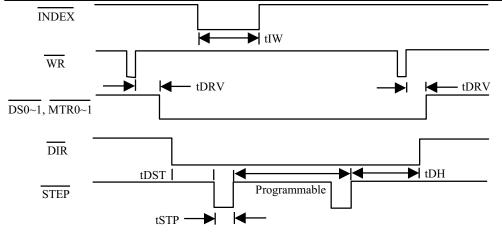

| 7       | DIR                      | Out            | Direction Control pin. This high current low active output determines the direction of the head movement. A logic 1 on this pin means outward motion, while a logic 0 means inward motion.                   |  |  |  |  |  |

| 8       | STEP                     | Out            | Step Pulse pin. This active low high current driver issues a low pulse for each track-to-track movement of the head                                                                                          |  |  |  |  |  |

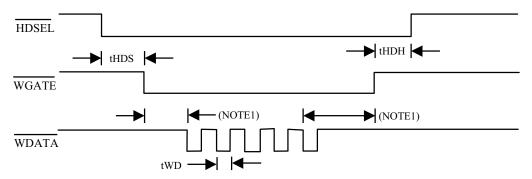

| 9       | WDATA                    | Out            | Write Data pin. This active low high current driver provides the encoded data to the disk drive. Each falling edge causes a flux transition on the media.                                                    |  |  |  |  |  |

| 10      | WGATE                    | Out            | Write Gate pin. This active low high current driver allows current to flow through the write head. It becomes active just prior to writing to the diskette.                                                  |  |  |  |  |  |

| 11      | HDSEL                    | Out            | Head Select pin. This high current output selects the floppy disk side for reading or writing. A logic 1 on this pin means side 0 will be accessed, while a logic 0 means side 1 will be accessed.           |  |  |  |  |  |

| 12      | INDEX                    | In             | This active low Schmitt Trigger input senses from the disk drive that the head is positioned over the beginning of a track, as marked by an index hole.                                                      |  |  |  |  |  |

| 13      | TRK00                    | In             | This active low Schmitt Trigger input senses from the disk drive that the head is positioned over the outermost track.                                                                                       |  |  |  |  |  |

| 14      | WRTPRT                   | In             | Write Protected pin. This active low Schmitt Trigger input senses from the disk drive that a disk is write protected. Any write command is ignored.                                                          |  |  |  |  |  |

| 16      | RDATA                    | In             | Read Disk Data pin. Raw serial bit stream from the disk drive, low active. Each falling edge represents a flux transition of the encoded data.                                                               |  |  |  |  |  |

| 17      | DSKCHG                   | In             | Disk Change pin. This input senses that the drive door is open or that the diskette has possibly been changed since the last drive selection. This input is inverted and read via bit 7 of I/O address 3F7H. |  |  |  |  |  |

| 18      | DRVDEN1                  | Out            | Indicates the drive and media selected.                                                                                                                                                                      |  |  |  |  |  |

| PIN NO. | PIN<br>NAME              | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|---------|--------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|         | 3) SERIAL PORT INTERFACE |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 88      | RXD2/<br>IRRX            | In             | Receive Data pin. Receiver serial data input for port 2. IR Receive Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 89      | TXD2/<br>IRTX            | Out            | Transmit Data pin. Receiver serial data output for port 2. IR Transmit Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 78      | RXD1                     | In             | Receive Data pin. Receiver serial data input for port 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 79      | TXD1                     | Out            | Transmit Data pin. Transmit serial data output for port 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 81, 91  | RTS1,<br>RTS2            | Out            | Active low Request To Send outputs for the serial port. Handshake out put signal notifies modem that the UART is ready to transmit data. This signal can be programmed by writing to bit 1 of Modem Control Register (MCR). The hardware reset will reset the RTS signal to inactive mode (high). Forced inactive during loop mode operation.                                                                                                                                                                                                                      |  |  |  |  |

| 83, 93  | DTR1,<br>DTR2            | Out            | Active low Data Terminal Ready outputs for the serial port. Handshake output signal notifies modem that the UART is ready to establish data communication link. This signal can be programmed by writing to bit 0 of Modem Control Register (MCR). The hardware reset will reset the DTR signal to inactive mode (high). Forced inactive during loop mode operation.                                                                                                                                                                                               |  |  |  |  |

| 82, 92  | CTS1,<br>CTS2            | In             | Active low Clear to Send inputs for the serial port. Handshake signal which notifies the UART that the modem is ready to receive data. The CPU can monitor the status of CTS signal by reading bit 4 of Modem Status Register (MSR). A CTS signal state change from low to high after the last MSR read will set MSR bit 0 to a logic 1. If bit 3 of Interrupt Enable Register is set, the interrupt is generated when CTS changes state. The CTS signal has no effect on the transmitter. * Note: Bit 4 of MSR is the complement of CTS.                          |  |  |  |  |

| 80, 90  | DSR1,<br>DSR2            | In             | Active low Data Set Ready inputs for the serial port. Handshake signal which notifies the UART that the modem is ready to establish the communication link. The CPU can monitor the status of $\overline{DSR}$ signal by reading bit 5 of Modem Status Register (MSR). A $\overline{DSR}$ signal state change from low to high after the last MSR read will set MSR bit 1 to a logic 1. If bit 3 of Interrupt Enable Register is set, the interrupt is generated when $\overline{DSR}$ changes state. * Note: Bit 7 of MSR is the complement of $\overline{DSR}$ . |  |  |  |  |

| 85, 87  | DCD1,<br>DCD2            | In             | Active low Data Carrier Detect inputs for the serial port. Handshake signal which notifies the UART that the carrier signal detected by the modem. The CPU can monitor the status of DCD signal by reading bit 7 of Modem Status Register (MSR). A DCD signal state change from low to high after the last MSR read will set MSR bit 3 to a 1. If bit 3 of Interrupt Enable Register is set, the interrupt is generated when DCD changes state. * Note: Bit 7 of MSR is the complement of DCD.                                                                     |  |  |  |  |

| PIN NO. | PIN<br>NAME | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 84, 86  | RII,<br>RI2 | In             | Active low Ring Indicator inputs for the serial port. Handshake signal which notifies the UART that the telephone ring signal is detected by the modem. The CPU can monitor the status of RI signal by reading bit 6 of Modem Status Register (MSR). A RI signal state change from low to high after the last MSR read will set MSR bit 2 to a logic ?? If bit 3 of Interrupt Enable Register is set, the interrupt is generated when RI changes state. * Note: Bit 6 of MSR is the complement of RI. |

|         |             |                | 4) PARALLEL PORT INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 73      | SLCTIN      | In/Out         | Printer Select Input pin. The active low output selects the printer. This is the complement of bit 3 of the Parallel Control Register.                                                                                                                                                                                                                                                                                                                                                                |

|         |             |                | Refer to Parallel Port description for use of this pin in ECP and EPP mode.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 74      | INIT        | In/Out         | Initiate pin. This output is bit 2 of the Parallel Control Register. This is used to initiate the printer when low.                                                                                                                                                                                                                                                                                                                                                                                   |

|         |             |                | Refer to Parallel Port description for use of this pin in ECP and EPP mode.                                                                                                                                                                                                                                                                                                                                                                                                                           |

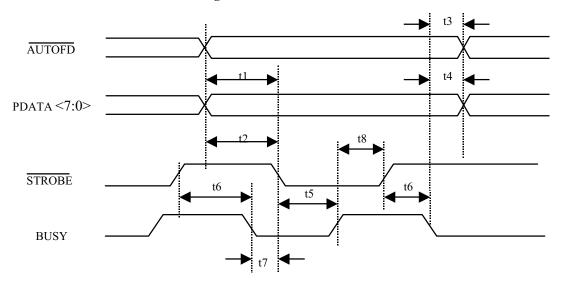

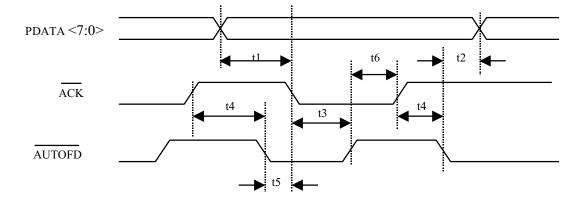

| 76      | AUTOFD      | In/Out         | Autofeed pin. This output goes low to cause the printer to automatically feed one line after each line is printed. The AUTOFD output is the complement of bit 1 of the Parallel Control Register.                                                                                                                                                                                                                                                                                                     |

|         |             |                | Refer to Parallel Port description for use of this pin in ECP and EPP mode.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 77      | STROBE      | In/Out         | An active low pulse on this output is used to strobe the printer data into the printer. The STROBE output is the complement of bit 0 of the Printer Control Register.                                                                                                                                                                                                                                                                                                                                 |

|         |             |                | Refer to Parallel Port description for use of this pin in ECP and EPP mode.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 61      | BUSY        | In             | This is a status output from the printer, a high indicating that the printer is not ready to receive new data. Bit 7 of the Printer Status Register is the complement of the BUSY input.                                                                                                                                                                                                                                                                                                              |

|         |             |                | Refer to Parallel Port description for use of this pin in ECP and EPP mode.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 62      | ACK         | In             | Acknowledge pin. A low active output from the printer indicating that it has received the data and is ready to accept new data. Bit 6 of the Printer Status Register reads the ACK input.                                                                                                                                                                                                                                                                                                             |

|         |             |                | Refer to Parallel Port description for use of this pin in ECP and EPP mode.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 60      | PE          | In             | Paper End. Another status output from the printer, a high indicating that the printer is out of paper. Bit 5 of the Printer Status Register reads the PE input.                                                                                                                                                                                                                                                                                                                                       |

|         |             |                | Refer to Parallel Port description for use of this pin in ECP and EPP mode.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PIN NO.        | PIN<br>NAME  | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                            |  |

|----------------|--------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 59             | SLCT         | In             | Printer Selected Status pin. This high active output from the printer indicates that it has power on. Bit 4 of the Printer Status Register reads the SLCT input. Refer to Parallel Port description for use of this pin in ECP and EPP mode.                                                                                                                           |  |

| 75             | ERROR        | In             | A low on this input from the printer indicates that there is an error condition at the printer. Bit 3 of the Printer Status register reads the ERR input. Refer to Parallel Port description for use of this pin in ECP and EPP mode.                                                                                                                                  |  |

| 63-66<br>68-71 | PD7-PD0      | In/Out         | Port Data pin. The bi-directional parallel data bus is used to transfer information between the chip and peripherals.                                                                                                                                                                                                                                                  |  |

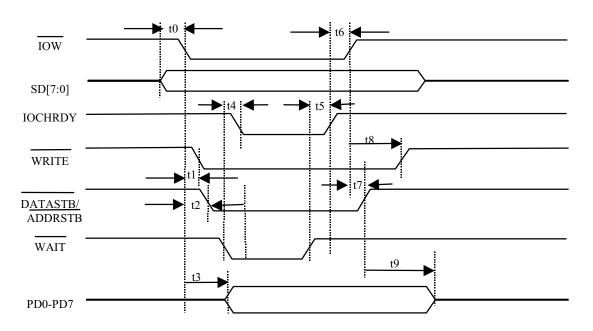

| 100            | IOCH-<br>RDY | Out            | In EPP mode, this pin is pulled low to extend the read/write command. This pin has an internal pull-up.                                                                                                                                                                                                                                                                |  |

|                |              | 5) IDE/16      | BIT ADDRESS QUALIFICATION/ ALT IR PINS                                                                                                                                                                                                                                                                                                                                 |  |

| 24             | IDEEN        | In<br>(Note)   | IDE Enable pin. This active low signal is active when the IDE is enabled and the I/O address is accessing an IDE register.                                                                                                                                                                                                                                             |  |

|                | IRQ_H        | Out            | The interrupt request from a logical device or IRQIN may be output on the IRQ_H signal. Refer to the configuration registers for more information.                                                                                                                                                                                                                     |  |

|                |              |                | If EPP or ECP Mode is enabled, this output is pulsed low, then released to allow sharing of interrupts.                                                                                                                                                                                                                                                                |  |

| 25             | HDCS0        | Out<br>(Note)  | IDE Chip Select pin. This is the Hard Disk Chip select corresponding to the eight control block addresses.                                                                                                                                                                                                                                                             |  |

|                | IRRX2        | In             | IR Receive pin. Alternate IR Receive input.                                                                                                                                                                                                                                                                                                                            |  |

| 26             | HDCS1        | Out<br>(Note)  | IDE Chip Select pin. This is the Hard Disk Chip select corresponding to the alternate status register.                                                                                                                                                                                                                                                                 |  |

|                | IRTX2        |                | IR Transmit pin. Alternate IR Transmit output.                                                                                                                                                                                                                                                                                                                         |  |

|                |              |                | 6) MISCELLANEOUS                                                                                                                                                                                                                                                                                                                                                       |  |

| 20             | CLK14        | ICLK           | Clock pin. The external connection to a single source 14.318 MHz clock.                                                                                                                                                                                                                                                                                                |  |

| 23             | IRQIN        | In             | This pin is used to steer an interrupt signal from an external device onto one of eight IRQ outputs, IRQA-H.                                                                                                                                                                                                                                                           |  |

| 58             | PWRGD        | In             | This active high input indicates that the power (Vcc) is valid. For device operation, PWRGD must be active. When PWRGD is inactive, all outputs are put into high impedance. The contents of all registers are preserved as long as Vcc has a valid value. The driver current drain in this mode drops to ISTBY (standby current). This input has an internal pull-up. |  |

|                | GAMECS       | Out            | This is the Game Port Chip Select output active low. It will go active when the I/O address, qualified by AEN, matches that selected in Configuration Register GDR.                                                                                                                                                                                                    |  |

| PIN NO.        | PIN<br>NAME       | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                   |  |

|----------------|-------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 94             | ADRX              | Out            | Address x pin. Active low address decode out; used to decode a 1, 8, or 16 byte address block. (An external pull-up is required). Refer to Configuration Registers (index=D6,D7) for more information. This pin has a 30 uA internal pull-up. |  |

|                | IRQ_B             | Out            | The interrupt request from a logical device or IRQIN may be output on IRQ_B. Refer to the configuration registers for more information.                                                                                                       |  |

|                |                   |                | (If EPP or ECP Mode is enabled, this output is pulsed low, then released to allow sharing of interrupts.)                                                                                                                                     |  |

| 98             | V <sub>I</sub> /o |                | I/O Power pin. I/O Interface Supply Pin (5V).                                                                                                                                                                                                 |  |

| 15,72          | Vcc               |                | Positive Supply Voltage.                                                                                                                                                                                                                      |  |

| 6,47,<br>67,95 | GND               |                | Ground Supply.                                                                                                                                                                                                                                |  |

Note : When IDE and IRQ\_H, IRRX2, IRTX2 are not selected, 3  $\mu$ A pull-ups are active

on the Pin 24, Pin 25, and Pin 26 Note: IDE does not decode for 377, 3F7

Note : RI and the Serial interrupt is always active if system power is applied to the chip.

# 3. CONFIGURATION

# 3.1 Configuration Register

The GM82C803C has configuration registers. The configuration registers can be set by software. Each configuration register is pointed by the value of the index register, and the contents of the configuration register is changed by writing data to the port 399H.

3.1.1 Device Identification Register (IDR : read only)

Index = C0

The contents of this is 3C for GM82C803C.

3.1.2 Device Revision Register (RVR: read only)

Index = C1

This indicates revision number, the default is 00

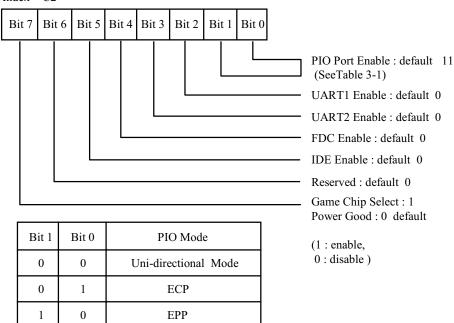

3.1.3 Function Selection Register (FSR)

Index = C2

1

1

(Table 3-1 PIO Port Mode Selection)

PIO Disable

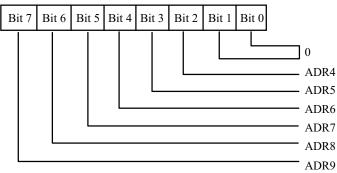

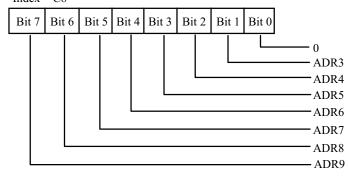

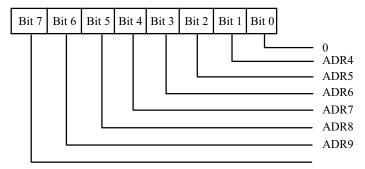

# 3.1.4 FDC Address Register (FAR)

Index = C3

This register is used to select the base address of the Floppy Disk Controller.

The FDC can be set to 48 locations on 16 byte boundaries from 100H-3F0H.

Upper address decode requirements: CS = ??and A10 = ??are required to access the FDC registers.

A[3:0] are decoded as 0xxxb

# 3.1.5 IDE Base address Register (IBR)

Index = C4

This register is used to select the base address of the IDE Interface Control Registers (0-7).

This can be set to 48 locations on 16byte boundaries from 100H-3F0H.

Upper address decode requirements:  $\overline{CS}$  = ??and A10 = ??are required to access the IDE registers. A[3:0] are decoded as 0xxxb

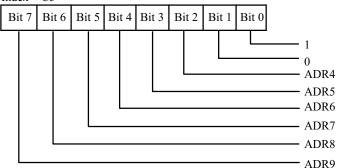

## 3.1.6 IDE Status address Register (ISR)

Index = C5

This register is used to select the base address of the IDE Interface Alternate Status Registers.

This can be set to 48 locations from 106H-3F6H.

Upper address decode requirements:  $\overline{CS}$  = ??and A10 = ??are required to access the IDE registers. A[3:0] must be 0110b

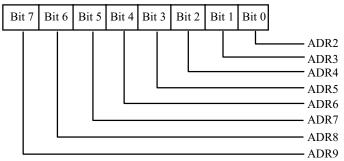

# 3.1.7 Parallel Port base Address Register (PAR)

Index = C6

This register is used to select the base address of the parallel port.

If EPP is not enabled, the parallel port can be set to 192 locations, on 4 byte boundaries form 100h-3FCh.

If EPP is enabled, the parallel port can be set to 96 locations, on 8 byte boundaries from 100h-3F8h.

Upper address decode requirements: CS = ??and A10 =??are required to access the parallel port when not ECP mode. (A10 active: when in ECP mode)

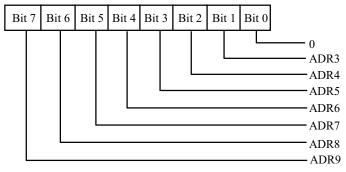

# 3.1.8 First Serial port base address Register (FSR)

Index = C7

This register is used to select the base address of the UART1.

The serial port can be set to 96 locations on 8 byte boundaries from 100H-3F8H.

Upper address decode requirements : CS = ??and A10 = ??are required to access UART 1 registers. A[3:0] are decoded as 0xxxb

## 3.1.9 Second Serial port base address Register (FSR) Index = C8

This register is used to select the base address of the UART2.

The serial port can be set to 96 locations on 8 byte boundaries from 100H-3F8H.

Upper address decode requirements : CS = ??and A10 = ??are required to access UART 2 registers. A[3:0] are decoded as 0xxxb

# 3.1.10 DMA Selection Register (DSR)

Index = C9

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | FDC DMA |

|-------|-------|-------|-------|---------|

| 0     | 0     | 0     | 0     | None    |

| 0     | 0     | 0     | 1     | DMA_A   |

| 0     | 0     | 1     | 0     | DMA_B   |

| 0     | 0     | 1     | 1     | DMA_C   |

| Bit 3 | Bit 2 | Bit 1 | Bit 0 | Parallel DMA |

|-------|-------|-------|-------|--------------|

| 0     | 0     | 0     | 0     | None         |

| 0     | 0     | 0     | 1     | DMA_A        |

| 0     | 0     | 1     | 0     | DMA_B        |

| 0     | 0     | 1     | 1     | DMA_C        |

This register is used to select the DMA for the FDC (bits 7:4) and the parallel port (bits 3:0). Any unselected DMA ACK output is in tristate.

# 3.1.11 IRQ Selection Register (IRR)

Index = CA

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | FDC IRQ |

|-------|-------|-------|-------|---------|

| 0     | 0     | 0     | 0     | None    |

| 0     | 0     | 0     | 1     | IRQ_A   |

| 0     | 0     | 1     | 0     | IRQ_B   |

| 0     | 0     | 1     | 1     | IRQ_C   |

| 0     | 1     | 0     | 0     | IRQ_D   |

| 0     | 1     | 0     | 1     | IRQ_E   |

| 0     | 1     | 1     | 0     | IRQ_F   |

| 0     | 1     | 1     | 1     | None    |

| 1     | 0     | 0     | 0     | IRQ_H   |

| Bit 3 | Bit 2 | Bit 1 | Bit 0 | Parallel IRQ |

|-------|-------|-------|-------|--------------|

| 0     | 0     | 0     | 0     | None         |

| 0     | 0     | 0     | 1     | IRQ_A        |

| 0     | 0     | 1     | 0     | IRQ_B        |

| 0     | 0     | 1     | 1     | IRQ_C        |

| 0     | 1     | 0     | 0     | IRQ_D        |

| 0     | 1     | 0     | 1     | IRQ_E        |

| 0     | 1     | 1     | 0     | IRQ_F        |

| 0     | 1     | 1     | 1     | None         |

| 1     | 0     | 0     | 0     | IRQ_H        |

This register is used to select the IRQ for the FDC (bits 7:4) and the parallel port (bits 3:0). Any unselected IRQ output (registers : IRR, SIR, IIR) is in tristate.

# 3.1.12 Serial IRQ selection Register (SIR)

Index = CB

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Serial 1 IRQ |

|-------|-------|-------|-------|--------------|

| 0     | 0     | 0     | 0     | None         |

| 0     | 0     | 0     | 1     | IRQ_A        |

| 0     | 0     | 1     | 0     | IRQ_B        |

| 0     | 0     | 1     | 1     | IRQ_C        |

| 0     | 1     | 0     | 0     | IRQ_D        |

| 0     | 1     | 0     | 1     | IRQ_E        |

| 0     | 1     | 1     | 0     | IRQ_F        |

| 0     | 1     | 1     | 1     | None         |

| 1     | 0     | 0     | 0     | IRQ_H        |

| Bit 3 | Bit 2 | Bit 1 | Bit 0 | Serial 2 IRQ |

|-------|-------|-------|-------|--------------|

| 0     | 0     | 0     | 0     | None         |

| 0     | 0     | 0     | 1     | IRQ_A        |

| 0     | 0     | 1     | 0     | IRQ_B        |

| 0     | 0     | 1     | 1     | IRQ_C        |

| 0     | 1     | 0     | 0     | IRQ_D        |

| 0     | 1     | 0     | 1     | IRQ_E        |

| 0     | 1     | 1     | 0     | IRQ_F        |

| 0     | 1     | 1     | 1     | None         |

| 1     | 0     | 0     | 0     | IRQ_H        |

This register is used to select the IRQ for serial port 1 (bits 7:4) and the serial port 2 (bits 3:0). Any unselected IRQ output (registers : IRR, SIR, IIR) is in tristate.

# 3.1.13 In IRQ selection Register (IIR)

Index = CD

This register is used to select the IRQ for IRQIN (bits 3:0), bits 7:4 are reserved and return zero when read. Any unselected IRQ output (registers: IIR, SIR, IRR) is in tristate.

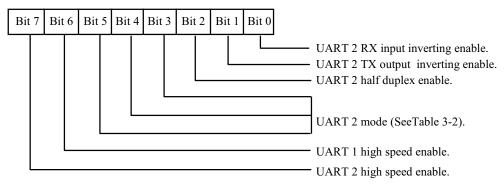

# 3.1.14 UART Mode Register (UMR)

Index = CE

This register controls the operating mode of the UART.

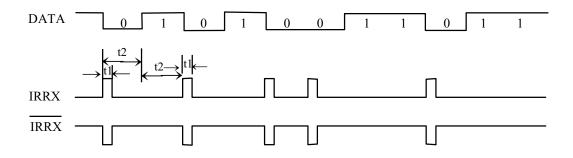

| Bit 5 | Bit 4 | Bit 3 | UART 2 MODE                       |  |

|-------|-------|-------|-----------------------------------|--|

| 0     | 0     | 0     | Standard (Default)                |  |

| 0     | 0     | 1     | IrDA (HPSIR)                      |  |

| 0     | 1     | 0     | Amplitude Shift Keyed IR @ 500KHz |  |

| 0     | 1     | 1     | Reserved                          |  |

| 1     | Х     | х     | Reserved                          |  |

(Table 3-2. UART 2 MODE)

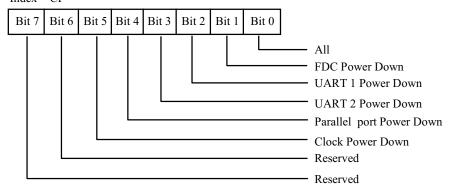

# 3.1.15 Power Down Register (PDR)

Index = CF

This register controls which part falls in power down mode.

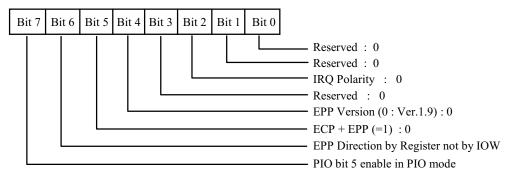

# 3.1.16 Printer Control Register (PCR)

Index = D0

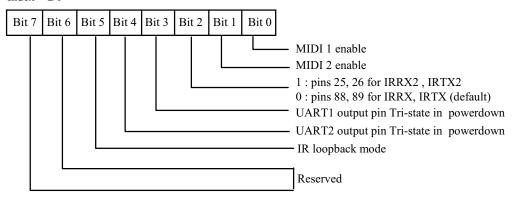

# 3.1.17 MIDI Support Register (MSR)

Index = D1

MIDI enable means UART clock is 24 MHz/12 instead of 24 MHz/13

## 3.1.18 Test Mode Register (TMR, T3R)

Index = D2, D4

These registers are used to support chip debugging and test.

The system should not access these.

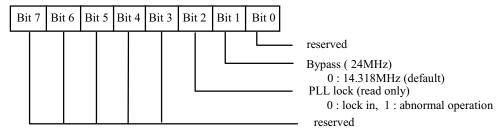

## 3.1.19 Clock Mode Register (T2R)

Index = D3

This register controls the operating mode of the clock generator. If you want to use 24MHz external clock, you must change bit 1 of this register. Default = 0 (14.MHz clock)

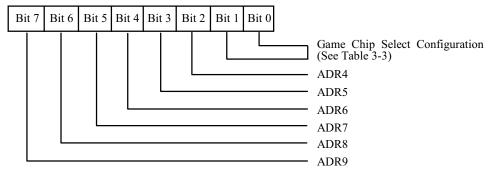

# 3.1.20 Game chip select Decoding Register (GDR)

Index = D5

| Bit 1 | Bit 0 | Configuration   |

|-------|-------|-----------------|

| 0     | 0     | GAMECS Disable  |

| 0     | 1     | ADR[3:0]= 0001b |

| 1     | 0     | ADR[3:0]= 0xxxb |

| 1     | 1     | ADR[3:0]= xxxxb |

| Bit 5 | Bit 4 | Configuration                    |

|-------|-------|----------------------------------|

| 0     | 0     | ADRx Disable                     |

| 0     | 1     | 1 byte decode, ADR[3:0]= 0001b   |

| 1     | 0     | 8 byte decode, ADR[3:0]= 0xxxb   |

| 1     | 1     | 16 byte decode, ADR[3:0] = xxxxb |

(Table 3-3. Game chip select Configuration)

(Table 3-4. ADRx Configuration)

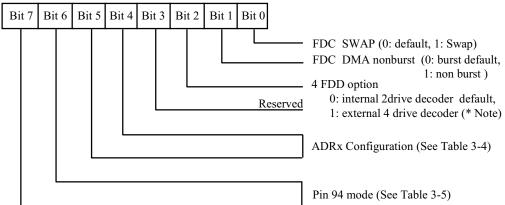

# 3.1.21 Pin 94 Mode Register (PMR)

Index = D6

| Bit 7 | Bit 6 | Configuration |  |  |

|-------|-------|---------------|--|--|

| 0     | X     | Tri-state     |  |  |

| 1     | 0     | ADRX          |  |  |

| 1     | 1     | IRQ_B         |  |  |

(Table 3-5. Pin 94 Mode Configuration)

\* Note: If you want to use 4 FDD, you require the external 2 to 4 decoder

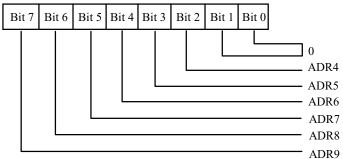

# 3.1.22 General purpose address Decode Register (GDR)

Index = D7

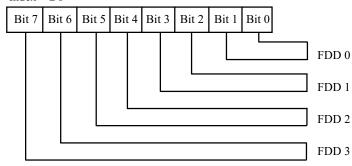

# 3.1.23 DRVDEN Selection Register

Index = D8

| FD    | D 3   | FDD 2 |       | FDD 1 |       | FDD 0 |       |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| DT1   | DT0   | DT1   | DT0   | DT1   | DT0   | DT1   | DT0   |

DTx: Drive Type Select

| DT1 | DT0 | DRVDEN 0 (Note) | DRVDEN 1 (Note) |

|-----|-----|-----------------|-----------------|

| 0   | 0   | DENSEL          | DRATE 0         |

| 0   | 1   | DRATE 1         | DRATE 0         |

| 1   | 0   | DENSEL          | DRATE 0         |

| 1   | 1   | DRATE 0         | DRATE 1         |

Note: DENSEL, DRATE 1 and DRATE 0 map to two output pins DRVDEN0 and DRVDEN1.

# 3.1.19 Software Configuration procedure

Configuration is accomplished in three basic steps:

- a) Enter configuration mode

- b) Configure the GM82C803C

- c) Escape from configuration mode

Any deviation from this sequence causes the configuration state machine to return to its initial idle state. The configuration procedure is intentionally complicated to prevent an errant program from making accidental changes to the chip configuration.

Enter Configuration Mode

Write 33h to port 398h twice consecutively.

The following is an example in 8086 assembly language:

```

MOV DX,398h: Port Address

```

MOV AL,33h : Data

OUT DX, AL

OUT DX, AL: In configuration mode

Configure the Chip

The 25 configuration registers can be written to or read from.

To read or write data from/to the registers:

- 1. Write index to port 398h

- 2. Write data to port 399h/Read data from port 399h. (where \( \frac{1}{2}\) ata? is the value to be written to/to be read from the register which the index points to.)

Escape from Configuration Mode

Write 55h to port 398h once.

The following is an example

MOV DX, 398h : Port Address

MOV AL, 55h : Data

OUT DX, AL : Exit from configuration mode

# **GM82C803C Configuration Registers**

| Index | Default | Bit 7                              | Bit 6                   | Bit 5        | Bit 4       | Bit 3      | Bit 2           | Bit 1                     | Bit 0                    |  |

|-------|---------|------------------------------------|-------------------------|--------------|-------------|------------|-----------------|---------------------------|--------------------------|--|

| C0    | 3C      |                                    | Device ID (3C)          |              |             |            |                 |                           |                          |  |

| C1    | 00      |                                    |                         | Revision     | n number (0 | 00)        |                 |                           |                          |  |

| C2    | 03      | GCS/<br>PWRGDS                     | Reserved                | IDE          | FDC         | UART2      | UART1           | PIO 1                     | PIO 2                    |  |

| СЗ    | 3C      |                                    | FDC A                   | Address AD   | R[9:4]      |            |                 | 0                         | 0                        |  |

| C4    | 3C      |                                    | IDE B                   | ase Addres   | s ADR[9:4   | ]          |                 | 0                         | 0                        |  |

| C5    | 3D      |                                    | IDE St                  | tatus Addre  | ss ADR[9:   | 4]         |                 | 0                         | 1                        |  |

| С6    | 00      |                                    | Paralle                 | el port Base | e Address A | ADR[9:2]   |                 | •                         |                          |  |

| С7    | 00      |                                    | First S                 | Serial port  | Base Addr   | ess ADR[9: | 3]              |                           | 0                        |  |

| С8    | 00      |                                    | Second                  | Serial por   | t Base Ad   | dress ADR[ | 9:3]            |                           | 0                        |  |

| С9    | 00      |                                    | FDC DRQ                 | )            |             |            | Parallel p      | ort DRQ                   |                          |  |

| CA    | 00      |                                    | FDC IRQ                 |              |             |            | Parallel p      | ort IRQ                   |                          |  |

| СВ    | 00      |                                    | Serial 1 IRQ Serial 2 I |              |             |            | IRQ             |                           |                          |  |

| СС    | 00      |                                    | Reserved                |              |             |            |                 |                           |                          |  |

| CD    | 00      |                                    | Reserved                |              |             | IRC        | ) IN IRQ        |                           |                          |  |

| CE    | 00      | UART2<br>Speed                     | UART1<br>Speed          | Ţ            | JART2 Mo    | ode        | UART2<br>Duplex | UART2<br>XMIT<br>Polarity | UART2<br>RCV<br>Polarity |  |

| CF    | 00      | Rese                               | erved                   |              |             | Power Dov  | wn mode         |                           |                          |  |

| D0    | 00      |                                    |                         | EC           | CP Mode     |            |                 | Res                       | erved                    |  |

| D1    | 00      |                                    | Reserved                |              | UART        | 1,2 mode   | ALT I/O         | MIDI 2                    | MIDI 1                   |  |

| D2    | 00      |                                    |                         | Т            | est Mode r  | egister 1  |                 |                           |                          |  |

| D3    | 00      | Reserved PLL lock                  |                         |              |             |            | Bypass          | Reserved                  |                          |  |

| D4    | 00      | Test Mode register 3               |                         |              |             |            |                 |                           |                          |  |

| D5    | 3C      | GAME CS ADR[9:4]                   |                         |              |             | GAME C     | CS Config.      |                           |                          |  |

| D6    | 00      | ADRx-IRQ_B ADRx Config Reserved FD |                         |              |             |            | DC mode         | ;                         |                          |  |

| D7    | 00      |                                    | Ger                     | neral Purpo  | ose Address | s ADR[10:4 | ]               |                           | 0                        |  |

| D8    | 00      | FDD                                | 3 -DTx                  | FDD          | 2 -DTx      | FDD        | 1-DTx           | FDD                       | 0 -DTx                   |  |

#### 4. FUNCTIONAL DESCRIPTION

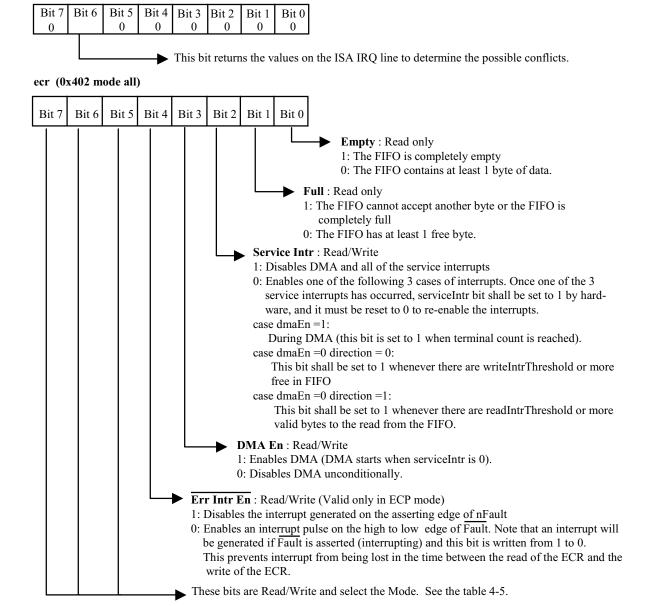

#### 4.1 PARALLEL PORT

The Prime 3C supports the IBM XT/AT Compatible parallel port, the PS/2 type bi-directional parallel port, the EPP (Enhanced Parallel Port) and the ECP (Extended Capabilities Port) modes. The information on selecting the mode of operation, changing base address of parallel port, powerdown parallel port and disabling parallel port are descripted at PRIME3C configuration registers.

## IBM XT/AT Compatible Mode

The IBM XT/AT Compatible parallel port is selected in FSR register and supports Centronics style standard mode. The PRIME3C also supports the optional PS/2 type bi-directional parallel port by setting the bit7 of PCR register.

The registers used in compatible mode are shown in table 4-1.

| REGISTER      | ADDRESS            |

|---------------|--------------------|

| DATA (DTR)    | BASE ADDRESS + 00H |

| STATUS (STR)  | BASE ADDRESS + 01H |

| CONTROL (CTR) | BASE ADDRESS + 02H |

(Table 4-1 Compatible Mode Register Set)

#### DATA REGISTER (DTR)

This register transfers 8 bit data and is located at an offset of 00H from base address. The reset value is 00H. In compatible mode, the data written to this register is transmitted to parallel port. The read operation in this mode causes the data register to present the last data written to it by CPU. In PS/2 style bi-direction mode, a write operation causes the data to be latched. If the direction bit(the bit5 of CTR) is 0, the latched data is presented on parallel port. If the direction bit is 1, the data is only latched. When direction bit is 0, a read operation in this mode causes the data register to present the last data written to port by CPU. When direction bit is 1 and bi-directional mode, a read operation causes the data on parallel port to be presented on system data port. The table 4-2 shows these operations.

| MODE         | DIRECTION | nIOR | nIOW | RESULT                          |

|--------------|-----------|------|------|---------------------------------|

| compatible   | X         | 1    | 0    | DATA Written to PD[0:7]         |

| compatible   | X         | 0    | 1    | DATA Read from the Output Latch |

| bi-direction | 0         | 1    | 0    | DATA Written to PD[0:7]         |

| bi-direction | 1         | 1    | 0    | DATA Written is Latched         |

| bi-direction | 0         | 0    | 1    | DATA Read from the Output Latch |

| bi-direction | 1         | 0    | 1    | DATA Read from PD[0:7]          |

( Table 4-2 Read and Write of Data Register in Compatible and Bi-direction Mode )

## STATUS REGISTER (STR)

This register is located at an offset of 01H from base address and is read-only register. This register can be accessed in all parallel port modes. The bits of STR are defined as follows:

#### **BIT 0 TIMEOUT**

This bit is valid in only EPP mode and indicates that a 10 usec timeout has occurred. A logic 0 means that no timeout error has occurred. A logic 1 indicates that a timeout error has been detected. This bit can be cleared by RESET or writing a 1 to this bit. In not EPP mode, this bit is always 0.

#### BIT 1, 2

These bits are reserved and always 0.

## BIT 3 ERROR

This bit reflects the state of the ERROR input pin. A logic 0 means that error has been detected.

#### BIT 4 SLCT

This bit reflects the state of the SLCT input pin. A logic 1 indicates that printer is on-line. A logic 0 means printer is not selected.

#### BIT 5 PE

This bit reflects the state of the PE input pin. A logic 1 indicates that printer is out of paper.

## BIT 6 ACK

This bit reflects the state of the  $\overline{ACK}$  input pin. A logic 0 indicates that printer has been received a character and is ready to accept another.

# BIT 7 BUSY

This bit reflects the inverted state of the BUSY input pin. A logic 0 indicates that printer is busy and cannot accept a new data.

#### **CONTROL REGISTER (CTR)**

This register is located at an offset of 02H from base address. The reset value is 00H. This read/write register provides control of all output signals. This register can be accessed in all parallel port.

#### BIT 0 STROBE

This bit is inverted of the STROBE pin and controls data strobe to printer.

#### BIT 1 AUTOFD

This bit is inverted of the AUTOFD pin. A logic 1 causes the printer to generate an automatic line feed at the end of each line.

# BIT 2 INIT

This bit controls INIT pin used to initialize the printer. A logic 0 generates active low pulse to initialize the printer.

#### BIT 3 SLCTIN

This bit is inverted of the SLCTIN pin. A logic 1 causes the printer to be selected.

#### BIT 4 IROEN

This is the interrupt request enabling bit. When this bit is 1, parallel port interrupt is generated in respond to a transition of ACK signal from the printer. Otherwise, all interrupts are disabled and all pending interrupts are cleared.

#### BIT 5 DIR

This bit controls the parallel port direction. A logic 0 indicates that the parallel port is in output mode and a logic 1 indicates that parallel port is in input mode. In the compatible mode, this bit is always 0 regardless of the state of this bit.

#### BIT 6.7

These bits are reserved and always 0.

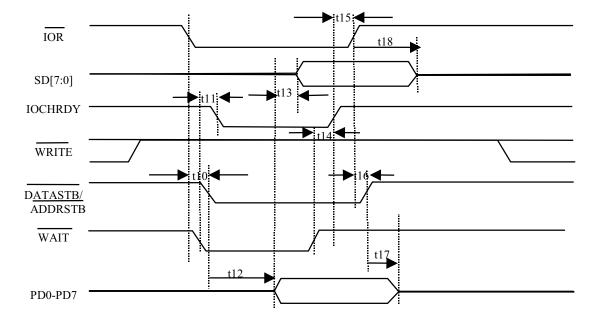

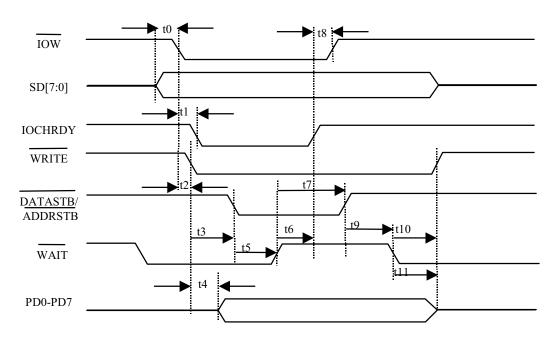

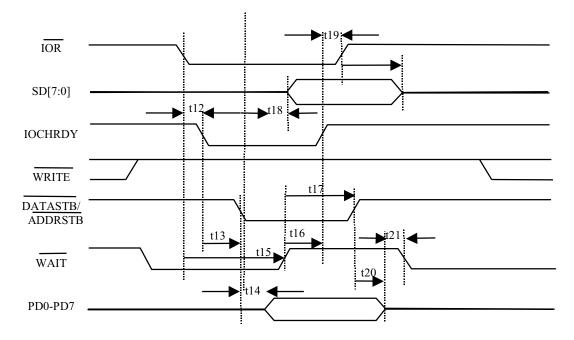

#### 3.2 EPP MODE

The EPP mode is high speed and bi-direction protocol and the data rate is up to 2M byte/sec. The EPP mode provides for greater throughput than compatible mode by supporting faster transfer time and a mechanism that allows the host to address peripheral device registers directly. The PRIME3C supports EPP mode(IEEE 1284) that can be selected through the FSR. When PRIME3C is in EPP mode, the PRIME3C also supports PS/2 style bi-direction mode. The PRIME3C supports 2 EPP modes: EPP ver. 1.7 and ver. 1.9. The EPP version is selected by the bit 4 of PCR and the default version is ver. 1.9. There are 4 operations in EPP mode: address write, address read, data write and data read. Before accessing the EPP registers, the software must write 0's to bit0,1,3 and 5 of CTR because the output pins and direction of data are controlled by EPP hardware. If the bit 6 of PCR is 1, the software must control direction of data by setting and resetting the bit5 of CTR(direction bit). The EPP operations are closely related with the system timing(I/O read and write). For this reason, a timer is required to prevent system from being locked up. If more than 10 usec have elapsed from start of the EPP cycle, the timeout timer generates timeout error and sets the timeout bit of STR. This timeout condition is available only in EPP ver. 1.9.

The EPP mode has 8 addressable ports. These ports are defined as follows.

| data port        | base address + 00H | EPP data port 0 | base address + 04H    |

|------------------|--------------------|-----------------|-----------------------|

| status port      | base address + 01H | EPP data port 1 | $base\ address + 05H$ |

| control port     | base address + 02H | EPP data port 2 | base address + 06H    |

| EPP address port | base address + 03H | EPP data port 3 | base address + 07H    |

# DATA REGISTER (base address + 00H)

This register is Compatible parallel port and same with DTR register in Compatible mode.

# STATUS REGISTER (base address + 01H)

This register is same with STR register in Compatible mode.

## **CONTROL REGISTER (base address + 02H)**

This register is same with CTR register in Compatible mode.

## EPP ADDRESS REGISTER (base address + 03H)

This register is cleared at initialization by RESET. A write operation to this port initiates an EPP ADDRESS WRITE operation that is used for EPP device/register selection. A read operation to this port generates EPP ADDRESS READ operation.

# EPP DATA PORT 0 REGISTER (base address + 04H)

This register is cleared at initialization by RESET. Access to this port initiate EPP DATA WRITE or EPP DATA READ operations with bit[7:0].

#### EPP DATA PORT 1 REGISTER (base address + 05H)

This register is cleared at initialization by RESET. Refer to EPP DATA PORT 0 for a description of operation.

# EPP DATA PORT 2 REGISTER (base address + 06H)

This register is cleared at initialization by RESET. Refer to EPP DATA PORT 0 for a description of operation.

## EPP DATA PORT 3 REGISTER (base address + 07H)

This register is cleared at initialization by RESET. Refer to EPP DATA PORT 0 for a description of operation.

**TABLE4-3. Parallel Port Pin Out**

| Connector                           | SPP , ECP                                                            | Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EPP Mode                                                           | Pin                                                                |

|-------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|

| Pin No.                             | Mode                                                                 | Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    | Direction                                                          |

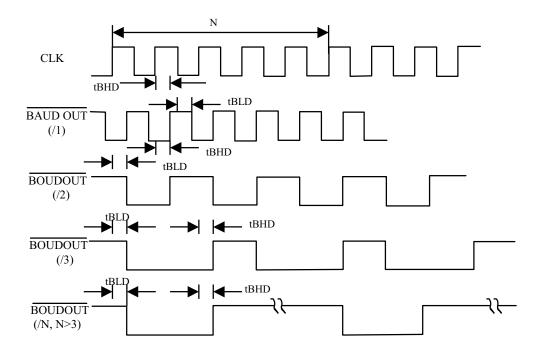

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 | STROBE PD0 PD1 PD2 PD3 PD4 PD5 PD6 PD7 ACK BUSY PE SLCT AUTOFD ERROR | I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / I   I   I   I   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O   I / O | WRITE PD0 PD1 PD2 PD3 PD4 PD5 PD6 PD7 ACK WAIT PE SLCT DSTRB ERROR | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O |